摘 要: 設(shè)計(jì)了一種基于電容倍增的無(wú)電容式LDO,將電容倍增模塊嵌入到了誤差運(yùn)算放大器的第一級(jí),提升了系統(tǒng)的環(huán)路帶寬,有良好的瞬態(tài)響應(yīng)。電路通過(guò)0.13 m標(biāo)準(zhǔn)CMOS工藝仿真實(shí)現(xiàn),仿真結(jié)果顯示,系統(tǒng)靜態(tài)功耗為42 W,當(dāng)負(fù)載從0~50 mA變化時(shí),電壓最大波動(dòng)為87 mV,建立時(shí)間為2.5 s。

關(guān)鍵詞: LDO;電容倍增;瞬態(tài)響應(yīng)

0 引言

作為電源管理芯片中重要的一員,低壓差線性穩(wěn)壓器(Low-Dropout regulator,LDO)因其紋波低、噪聲低、體積小等優(yōu)點(diǎn)被廣泛應(yīng)用到各種便攜式電子產(chǎn)品(如手機(jī)、PDA等)中。傳統(tǒng)的LDO利用片外大電容穩(wěn)定其輸出電壓,但是不易于系統(tǒng)集成[1-3]。與傳統(tǒng)的LDO相比,無(wú)電容式LDO不需要較大的片外電容,易于系統(tǒng)集成,然而其穩(wěn)定性和瞬態(tài)響應(yīng)成為設(shè)計(jì)的難點(diǎn)。為了保證無(wú)電容式LDO的穩(wěn)定性,通常利用米勒效應(yīng)來(lái)實(shí)現(xiàn)極點(diǎn)分類,為了達(dá)到足夠的相位裕度,通常需要采用較大的米勒補(bǔ)償電容,消耗較大的芯片面積。參考文獻(xiàn)[4]提出了一種經(jīng)典的電容倍增技術(shù),但是其電容倍增系數(shù)受到電流鏡電流之比的限制;參考文獻(xiàn)[5]提出的電容倍增技術(shù)能提高電容倍增系數(shù),有效地減小所需補(bǔ)償電容的面積,但由于誤差放大器輸出節(jié)點(diǎn)的非對(duì)稱性,為系統(tǒng)引入了失調(diào),影響了LDO的線性調(diào)整率。

本文提出LDO結(jié)構(gòu),將電容倍增技術(shù)嵌入到第一級(jí),使得第一級(jí)完全對(duì)稱,且能提高環(huán)路帶寬,提高了環(huán)路瞬態(tài)響應(yīng)速度,電路采用0.13 m標(biāo)準(zhǔn)CMOS工藝仿真實(shí)現(xiàn)。

1 電容倍增技術(shù)

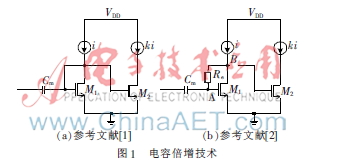

參考文獻(xiàn)[1]提出的電容倍增技術(shù)如圖1(a)所示,該技術(shù)基于電流模式實(shí)現(xiàn),其原理為:采樣流過(guò)電容的電流,通過(guò)電流鏡實(shí)現(xiàn)放大后再反饋到電容的另一端,以實(shí)現(xiàn)電容倍增效果。其等效電容為(1+k),其中k為電流鏡的放大系數(shù)。

參考文獻(xiàn)[2]采用的電容倍增技術(shù)如圖1(b)所示,在M1的柵極和漏極之間插入了一個(gè)電阻Re,同樣能實(shí)現(xiàn)自偏置效果,無(wú)需額外的偏置電路。A點(diǎn)仍為低阻節(jié)點(diǎn),但是B點(diǎn)不再是低阻節(jié)點(diǎn),因此流過(guò)Cm的電流通過(guò)Re和M1放大成電壓V1,然后通過(guò)M2再次轉(zhuǎn)換成電流。其等效電容可表示為:

Ceq=(1+k)gm1RbCm(1)

從式(1)可以看出,其等效電容與參考文獻(xiàn)[1]中提出的電容倍增技術(shù)相比,提高了gm1Re倍,因此對(duì)于固定的負(fù)載電容,所需要的片上補(bǔ)償電容大大減小。

2 LDO電路設(shè)計(jì)

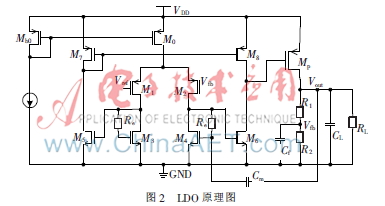

本文提出的LDO結(jié)構(gòu)如圖2所示,主要包括三部分。第一級(jí)全對(duì)稱的運(yùn)算放大器由M0~M8和電阻Re組成,其中包括由M3、Re、M5和M4、Re、M6組成的電容倍增模塊,該模塊嵌入第一級(jí),與參考文獻(xiàn)[2]相比,功耗減小了。同時(shí)第一級(jí)為完全對(duì)稱結(jié)構(gòu),因此能減小失調(diào)。第二級(jí)運(yùn)算放大器由功率管Mp和采樣電阻組成。第三部分為頻率補(bǔ)償部分。Vref為帶隙基準(zhǔn)源產(chǎn)生的基準(zhǔn)電壓;Cm為米勒補(bǔ)償電容;RL為負(fù)載電阻;CL為負(fù)載電容,為100 pF。

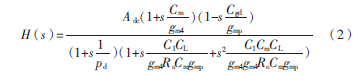

為了分析環(huán)路的穩(wěn)定性,求出其傳輸函數(shù)為:

其中,gmi為Mi的跨導(dǎo),R1為第一級(jí)輸出電阻,Ro為第二級(jí)輸出阻抗,C1為第一級(jí)輸出電容,其值分別為:

Ro=(R1+R1)//Rp//RL(3)

C1=Cgs_p+ApassCgd_p(4)

Adc和pd為運(yùn)算放大器的直流增益和主極點(diǎn),分別為:

Adc=kgm1gmpR1Ro(5)

![V{ZG9GJZ6JBP19@]L}OTC9C.jpg V{ZG9GJZ6JBP19@]L}OTC9C.jpg](http://files.chinaaet.com/images/2015/06/24/6357077349023700009230179.jpg)

由式(7)可以看出,本文提出的LDO結(jié)構(gòu)具有大的電容倍增系數(shù),同時(shí)與參考文獻(xiàn)[5]相比,GBW提升了k倍,因此具有更好的瞬態(tài)特性。

3 仿真實(shí)驗(yàn)

為了驗(yàn)證本文所提出的LDO的合理性,對(duì)圖2所示的電路采用0.13 μm 標(biāo)準(zhǔn)CMOS工藝仿真驗(yàn)證,當(dāng)工作溫度為25℃、輸入電壓為1.2 V、輸出電壓為1 V、負(fù)載電容為100 pF時(shí),由于采用了本文提出的電容倍增技術(shù),片上補(bǔ)償電容僅為0.8 pF。空載和負(fù)載為50 mA時(shí),LDO環(huán)路頻率響應(yīng)曲線如圖3所示。

仿真結(jié)果顯示,在0~50 mA全負(fù)載范圍內(nèi),最小增益為45.66 dB,單位增益帶寬為570 kHz,相位裕度為60°,反饋環(huán)路具有很好的穩(wěn)定性。同時(shí)由于將電容倍增模塊嵌入到了誤差運(yùn)算放大器的第一級(jí),因此提高了環(huán)路的單位增益帶寬。

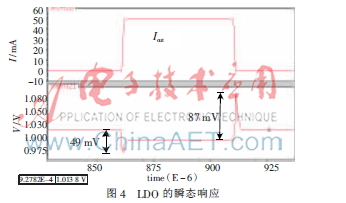

當(dāng)負(fù)載從空載跳到50 mA然后再跳回空載時(shí),系統(tǒng)的瞬態(tài)響應(yīng)如圖4所示。仿真結(jié)果顯示,上沖電壓為87 mV,調(diào)整時(shí)間為2.5 s;下沖電壓為49 mV,調(diào)整時(shí)間為2.0 s,由于系統(tǒng)單位增益帶寬得到了提升,因此具有良好的瞬態(tài)響應(yīng)特性。

4 結(jié)論

本文設(shè)計(jì)了一種新型的LDO,分析了電容倍增技術(shù)的原理,且將電容倍增模塊嵌入到了誤差運(yùn)算放大器的第一級(jí),提升了系統(tǒng)的環(huán)路帶寬,有良好的瞬態(tài)響應(yīng)。電路通過(guò)0.13 m標(biāo)準(zhǔn)CMOS工藝仿真實(shí)現(xiàn),結(jié)果顯示,系統(tǒng)靜態(tài)功耗為42 W,當(dāng)負(fù)載在全負(fù)載范圍變化時(shí),電壓波動(dòng)最大為87 mV,建立時(shí)間為2.5 s,能夠滿足SoC系統(tǒng)中供電電源的要求。

參考文獻(xiàn)

[1] 應(yīng)建華,黃楊,黃萌,等.基于電容倍增技術(shù)的LDO補(bǔ)償方法[J].微電子學(xué)與計(jì)算機(jī),2009,26(11):102-105.

[2] 劉明亮,明鑫,歐雪春,等.一種帶過(guò)溫保護(hù)和折返電流限的LDO設(shè)計(jì)[J].微電子學(xué)與計(jì)算機(jī),2011,41(3):411-415.

[3] LIN H C, WU H H, CHANG T Y. An active-frequency compensation scheme for CMOS Low-Dropout regulators with transient-response improvement[J]. IEEE Transactions on Circuits And Systems-II: Express Briefs, 2009,55(9):853-857.

[4] GABRIEL A, RINCON-MORA. Active capacitor multiplier in miller-compensatedcircuits[J]. IEEE Transactions on Solid-State Circuits, 2000, 35(1):26-32.

[5] MILLIKEN R J, Silva-Martínez Jose, Sánchez-Sinencio Edgar. Full on-chip CMOS Low-Dropout voltage regulator[J]. IEEE Transactions on Circuits and Systems-I: Regular Papers, 2007,54(9):1879-1890.

[6] 王晉雄,原義棟,張海峰.一種高線性調(diào)整率無(wú)電容型LDO的設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2012,38(11):44-47.