基于MSP430和Cyclone II 的網絡數據加密實現

國外電子元器件 西安電子科技大學 董暉 武攀

摘要: 通過對整個設計的調試驗證,結果滿足設計要求。整個系統(tǒng)具有較高的安全性和保密性,可為要求通信安全的網絡應用提供一種基于硬件的加密方式,基于FPGA的加密算法設計具有很高的靈活性,如果采用更加先進的加密算法,可進一步提高系統(tǒng)的安全性和保密性。

Abstract:

Key words :

1 引言

隨著信息技術和網絡化進程的發(fā)展,網絡通信安全問題日益突出。現場可編程門陣列(FPGA)以其自身設計靈活、可靠性高的優(yōu)點廣泛應用于加密領域。硬件實現的加密算法不占用計算機資源.加密過程完全與外部總線隔離,具有較高的數據保護能力。算法可靈活改變,具有較強的獨立性。加密機由單片機,FPGA和El通信接口組成。FPGA內部算法由VHDL語言編寫。該系統(tǒng)適用于要求數據安全較高的場合,其終端可為計算機,銀行POS機等,提供數據傳輸的安全性和保密性。

2 流加密解密原理及算法

2.1 流加密解密原理

流密碼由密鑰和密碼算法兩部分組成,密鑰一般存儲在加解密設備內部,在數據傳輸前已設置完成。密碼算法在較長時間內是不變的。在同步流密碼中,只要發(fā)送端和接收端有相同的密鑰和內部狀態(tài),就能產生相同的密鑰流。

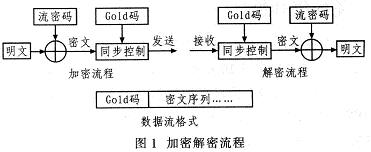

數據傳輸時,加密端和解密端使用同一個初始密鑰,加密時密碼流與明文相異或得到密文,同時每隔一定時間加入同步數據;解密時以同步模式產生的密文與密碼流進行異或得到明文,同步模式采用63位Gold碼。整個加解密過程與發(fā)送數據格式如圖1所示。在發(fā)送密文中加入初始同步碼,接收端利用Gold碼的三值特性檢測Gold碼實現同步數據。對接收數據流和Gold碼做互相關運算,相關結果滿足Gold碼的三值特性,說明當前數據流是發(fā)送端加入的同步Gold碼.標志為密文的起始,然后調用解密算法對后續(xù)的密文解密,恢復傳輸的數據。

2.2 A5/1算法原理

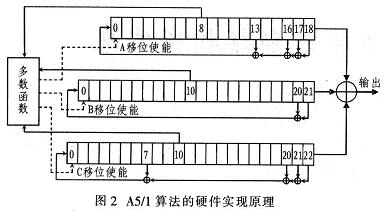

A5/1引是GSM移動通信中數據傳輸的流密碼加密算法。A5/1密碼流產生器生成的密碼與明文數據幀的每一位相異或得到密文序列。A5/1算法由3個不同長度的線性反饋移位寄存器R1,R2,R3組成,其長度分別為19,22,23位,其反饋特征方程分別為:x18+x17+x16+x13+1,x22+x21+x20+x7+1。算法的初始密鑰是64位向量。密碼流輸出位為3個移位寄存器的異或輸出。移位寄存器的使能由多數函數控制。Rl的第8位、R2的第10位、R3的第10位為多數函數數據輸入,它們決定3個移位寄存器的移位狀況。在這3個數據位中,如果有兩個或兩個以上的都為0,多數函數值就為0;如果有兩個或兩個以上的都為1,多數函數值就為1。多數函數輸入的3個數據位中與多數函數值相同,相應的移位寄存器就移位。A5/1的硬件實現原理如圖2所示。密碼流的產生分兩個階段.第一階段給寄存器裝人64位初始值;第二階段則根據時鐘節(jié)拍和使能控制產生密碼流。

2.3 W7算法原理

W7H算法與A5/1算法在結構原理上有相似之處。W7算法由8個類似于A5/1算法硬件結構模塊并行組成,每一個模塊都包含3個線性反饋移位寄存器和多數函數。不同的是w7算法是128位的初始密鑰,線性反饋移位寄存器的長度圖2 A5/1算法的硬件實現原理和反饋結構都不同于A5/1算法。3個線性反饋移位寄存器長度分別為38、43、47位。8個并行模塊采用同一初始密鑰。但反饋結構和多數函數的輸入位均各不相同。8個模塊的輸出組成8位密碼流,加密效率更高。各線性移位寄存器由固定數據位通過邏輯與產生1位數據,再將該位數據與最高位輸出異或,最后將3個移位寄存器輸出再異或輸出作為本并行塊的密碼位輸出。由于有8個并行塊,最后總的輸出8 bit,即1字節(jié)。設計時,每隔8個時鐘周期輸出一次,保證數據速率的一致性。

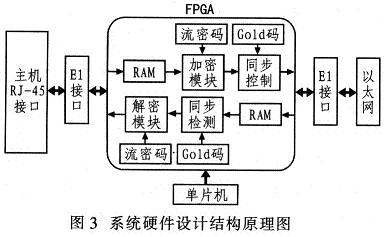

3 系統(tǒng)硬件設計

該系統(tǒng)硬件設計由單片機,FPGA和El接121等組成,如圖3所示。單片機用于輸入用戶初始密鑰;FPGA負責密鑰流產生以及加解密;E1接口實現數據流的發(fā)送和接收,完成HDB3碼和TTL電平之間的轉換,實現通信接口單元和協(xié)議數據處理單元之間的全雙工通信。

由于通信鏈路采用E1標準,該系統(tǒng)設計的外部數據鏈路接121采用E1接口,選用接口器件DS21348。DS21348支持El和T1線接口單元,通過寄存器設置選擇E1線接口單元。DS21348可配置為硬件模式,完成HDB3到TTL、TTL到HDB3的電平轉換,時鐘同步、數據信號格式轉換以及數據幀處理。該系統(tǒng)可并行處理兩路數據,一路加密,一路解密,實現全雙工通信。

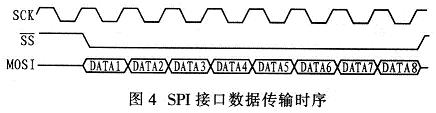

由于TI公司的MSP430系列微處理器平臺具有低功耗和小體積等特點,適合便攜式應用場合,所以單片機采用MSP430系列,并通過SPI接口實現與FPGA的數據通信。單片機外接一鍵盤,用于輸入初始密鑰。考慮到用戶輸入密鑰位數不能很多,可設置簡短的密鑰,并在單片機內部擴展至算法所需的位數,然后通過單片機SPI接口傳送至FGPA。SPI接口共4條信號線:串行時鐘(SCK),主機輸出/從機輸入(MOSI),主機輸入/從機輸出(MISO),從機片選(SS)。SPI接口可配置為主或從模式。設計配置為主模式。當單片機向FPGA傳輸命令或數據時,應用SPIO模式。當片選信號丙拉低,在每個時鐘(SCK)的上升沿發(fā)送數據,無需FPGA向單片機輸人數據,所以不使用MISO數據線。片選信號SS與FP-CA的RAM的使能相連,控制數據讀入。當用戶輸人初始密鑰后,經過數據擴展,與算法選擇數據通過SPI接口傳送至FPGA。SPI接口時序如圖4所示。

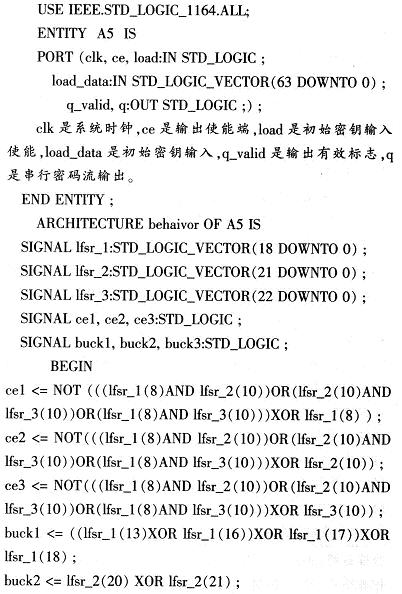

FPGA采用CycloneII系列中的EP20F256C6,該器件是低成本架構FPGA,可提供多達18 752個邏輯單元.152個用戶IO,239 616 bit的存儲位,密度超過CycloneI FPGA的3倍,完全滿足系統(tǒng)設計需要。CycloneII FPGA內部的邏輯資源可實現復雜應用。CycloneII器件采用的低成本串行配置器件,這種串行配置器件最大可提供64 Mbit的nash存儲器。所以,采用EP20F256C6可高效完成系統(tǒng)核心算法,有效節(jié)約成本。其內部算法由VHDL語言編程實現。主要程序模塊:加解密算法模塊(A5/1和W7)、數據存儲模塊、同步產生模塊、同步檢測模塊。加密和解密各有一套獨立的模塊集合。其中A5/1算法模塊的VHDL代碼如下:

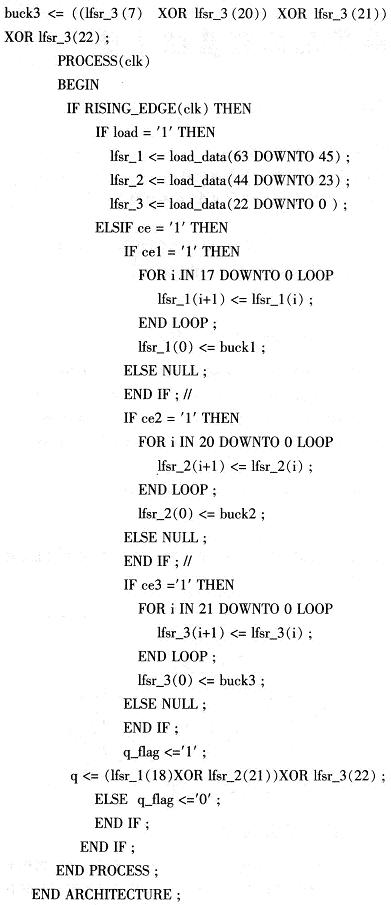

FPGA的模塊控制由兩個獨立的狀態(tài)機組成,用于處理加密算法和解密算法,其狀態(tài)轉換如圖5所示。

系統(tǒng)上電初始化后,由用戶向單片機輸入初始密鑰和算法選擇數據,通過SPI接口送入FPGA,FPGA接收到密鑰后將初始密鑰傳給算法模塊,算法模塊初始化后產生同步Gold碼,并等待數據,當待加密數據有效時,啟動加密算法;當數據無效時,再次進入等待數據狀態(tài)。相應地,解密模塊先檢測起始的同步Gold碼,檢測到后,當待解密數據有效時,啟動解密算法,當待解密數據無效時,再次進入等待數據狀態(tài)。如此往復,完成數據的加密解密過程。在密鑰傳輸過程中,由于兩種算法所需的初始密鑰位數不同,當使用w7算法時,初始密鑰在送入FPGA中后還需二次擴展達到所需的位數。

4 仿真與分析

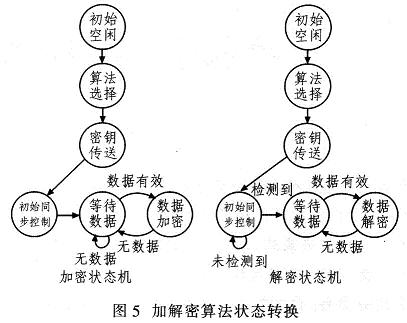

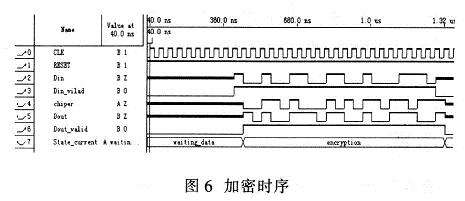

采用QuartuslI 8.0軟件仿真FPGA功能。共用4 865個邏輯單元,1 024 bit的片上存儲位,時序分析得到最大工作頻率為95.79 MHz。仿真加密時序如圖6所示。

5 結論

通過對整個設計的調試驗證,結果滿足設計要求。整個系統(tǒng)具有較高的安全性和保密性,可為要求通信安全的網絡應用提供一種基于硬件的加密方式,基于FPGA的加密算法設計具有很高的靈活性,如果采用更加先進的加密算法,可進一步提高系統(tǒng)的安全性和保密性。

此內容為AET網站原創(chuàng),未經授權禁止轉載。