在邏輯設(shè)計領(lǐng)域,只涉及單個時鐘域的設(shè)計并不多。尤其對于一些復(fù)雜的應(yīng)用,fpga" style="outline-style: none; color: rgb(51, 51, 51); text-decoration: none; font-family: Verdana, Arial, 微軟雅黑, 宋體; font-size: 16px; line-height: 30px;">FPGA往往需要和多個時鐘域的信號進(jìn)行通信。異步時鐘域所涉及的兩個時鐘之間可能存在相位差,也可能沒有任何頻率關(guān)系,即通常所說的不同頻不同相。

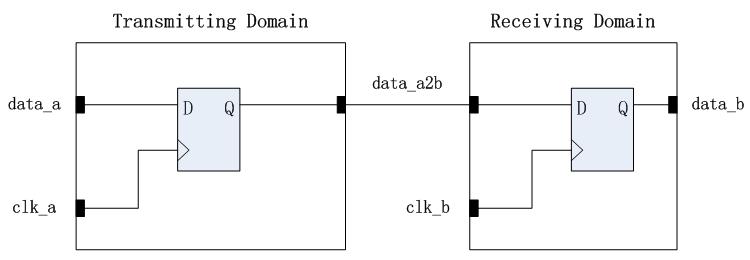

圖1是一個跨時鐘域的異步通信實例,發(fā)送域和接收域的時鐘分別是clk_a和clk_b。這兩個時鐘頻率不同,并且存在一定的相位差。對于接收時鐘域而言,來自發(fā)送時鐘域的信號data_a2b有可能在任何時刻變化。

圖1 跨時鐘域通信

對于上述的異步時鐘域通信,設(shè)計者需要做特殊的處理以確保數(shù)據(jù)可靠的傳輸。由于兩個異步時鐘域的頻率關(guān)系不確定,觸發(fā)器之間的建立時間和保持時間要求也無法得到保證。如果出現(xiàn)建立時間或者保持時間違規(guī),接收域?qū)蓸拥教幱趤喎€(wěn)態(tài)數(shù)據(jù),那么后果可想而知。

如何有效的進(jìn)行跨時鐘域的信號傳輸呢?最基本的思想是同步,在這個基礎(chǔ)上設(shè)計者可以利用各種協(xié)議約定進(jìn)行通信。單向控制信號檢測方式(前面提到過的脈沖信號檢測方法,這里為了和握手方式相區(qū)別,所以如此稱呼)、握手協(xié)議的方式或者借助存儲器的方式都是比較常用的處理手段。

本文將重點介紹握手方式進(jìn)行異步時鐘域的通信。

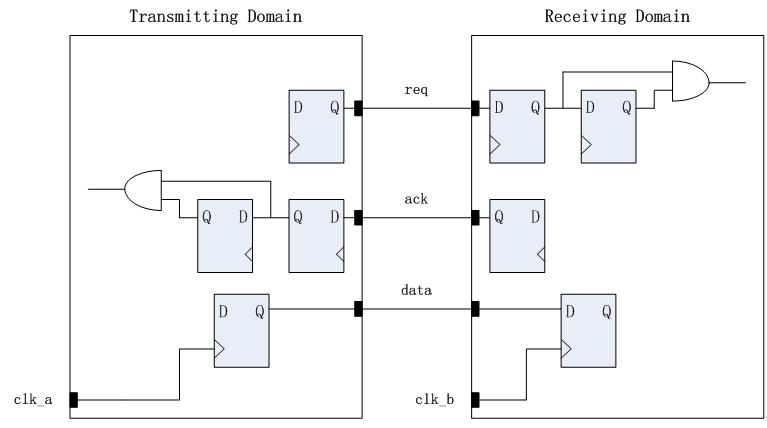

圖2是一個基本的握手通信方式。所謂握手,意即通信雙方使用了專用控制信號進(jìn)行狀態(tài)指示。這個控制信號既有發(fā)送域給接收域的,也有接收域給發(fā)送域的,有別于前面的單向控制信號檢測方式。

圖2 握手通信原理

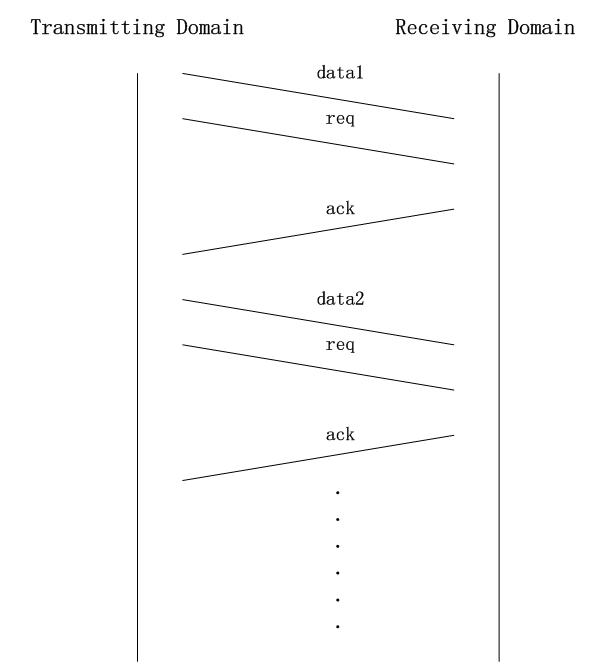

使用握手協(xié)議方式處理跨時鐘域數(shù)據(jù)傳輸,只需要對雙方的握手信號(req和ack)分別使用脈沖檢測方法進(jìn)行同步。在具體實現(xiàn)中,假設(shè)req、ack、data總線在初始化時都處于無效狀態(tài),發(fā)送域先把數(shù)據(jù)放入總線,隨后發(fā)送有效的req信號給接收域。接收域在檢測到有效的req信號后鎖存數(shù)據(jù)總線,然后回送一個有效的ack信號表示讀取完成應(yīng)答。發(fā)送域在檢測到有效ack信號后撤銷當(dāng)前的req信號,接收域在檢測到req撤銷后也相應(yīng)撤銷ack信號,此時完成一次正常握手通信。此后,發(fā)送域可以繼續(xù)開始下一次握手通信,如此循環(huán)。該方式能夠使接收到的數(shù)據(jù)穩(wěn)定可靠,有效的避免了亞穩(wěn)態(tài)的出現(xiàn),但控制信號握手檢測會消耗通信雙方較多的時間。以上所述的通信流程如圖3所示。

圖3 握手通信流程

下面通過一個簡單的工程代碼及其仿真測試進(jìn)一步加深大家對基本握手協(xié)議的認(rèn)識。

module handshack(

clk,rst_n,

req,datain,ack,dataout

);

input clk; //50MHz系統(tǒng)時鐘

input rst_n; //低電平復(fù)位信號

input req; //請求信號,高電平有效

input[7:0] datain; //輸入數(shù)據(jù)

output ack; //應(yīng)答信號,高電平有效

output[7:0] dataout;//輸出數(shù)據(jù),主要用于觀察是否和輸入一致

//--------------------------------------

//req上升沿檢測

reg reqr1,reqr2,reqr3;

always @(posedge clk or negedge rst_n)

if(!rst_n) begin

reqr1 <= 1'b1;

reqr2 <= 1'b1;

reqr3 <= 1'b1;

end

else begin

reqr1 <= req;

reqr2 <= reqr1;

reqr3 <= reqr2;

end

//pos_req2比pos_req1延后一個時鐘周期,確保數(shù)據(jù)被穩(wěn)定鎖存

wire pos_req1 = reqr1 & ~reqr2; //req上升沿標(biāo)志位,高有效一個時鐘周期

wire pos_req2 = reqr2 & ~reqr3; //req上升沿標(biāo)志位,高有效一個時鐘周期

//--------------------------------------

//數(shù)據(jù)鎖存

reg[7:0] dataoutr;

always @(posedge clk or negedge rst_n)

if(!rst_n) dataoutr <= 8'h00;

else if(pos_req1) dataoutr <= datain; //檢測到req有效后鎖存輸入數(shù)據(jù)

assign dataout = dataoutr;

//--------------------------------------

//產(chǎn)生應(yīng)答信號ack

reg ackr;

always @(posedge clk or negedge rst_n)

if(!rst_n) ackr <= 1'b0;

else if(pos_req2) ackr <= 1'b1;

else if(!req) ackr <= 1'b0;

assign ack = ackr;

endmodule

該實例的verilog代碼模擬了握手通信的接收域,其仿真波形如圖4所示。在發(fā)送域請求信號(req)有效的若干個時鐘周期后,先是數(shù)據(jù)(datain)被有效鎖存了(dataout),然后接收域的應(yīng)答信號(ack)也處于有效狀態(tài),此后發(fā)送域撤銷請求信號,接收域也跟著撤銷了應(yīng)答信號,由此完成一次通信。

圖4 握手通信仿真波形