1 引言

在系統(tǒng)設(shè)備不斷向小型化、集成化、網(wǎng)絡(luò)化發(fā)展的今天,嵌入式開發(fā)成為新技術(shù)發(fā)展的最前沿,改變著系統(tǒng)的整體結(jié)構(gòu)。FPGA由于其自身特點(diǎn),成為嵌入式開發(fā)的最佳平臺。Altera公司結(jié)合其最新一代高端器件推出了全新的嵌入式開發(fā)系統(tǒng),能夠?qū)崿F(xiàn)軟核niosII 32位處理器為核心的嵌入式開發(fā)系統(tǒng)。

在CvcloneII中,A1tera集成了完整的千兆以太網(wǎng)硬核,硬核包括MAC模塊以及可選擇的物理層PCS模塊和PMA模塊,其中MAC模塊支持l0/100/1000Mb/s。Altera的SOPCBuilder工具提供快速搭建SOPC系統(tǒng)的能力,這種架構(gòu)可以包含一個或多個CPU,提供存儲器接口,外圍設(shè)備和系統(tǒng)互連邏輯的復(fù)雜系統(tǒng)。

2 千兆以太網(wǎng)技術(shù)簡介

以太網(wǎng)技術(shù)是當(dāng)今應(yīng)用廣泛的網(wǎng)絡(luò)技術(shù),千兆以太網(wǎng)技術(shù)繼承了以往以太網(wǎng)技術(shù)的許多優(yōu)點(diǎn),同時又具有諸多新特性,例如傳輸介質(zhì)包括光纖和銅纜,使用8B/10B的編解碼方案,采用載波擴(kuò)展和分組突發(fā)技術(shù)等。正是因?yàn)榫哂辛己玫睦^承性和許多優(yōu)秀的新特性,千兆以太網(wǎng)已經(jīng)成為目前局域網(wǎng)的主流解決方案。

千兆以太網(wǎng)利用原以太網(wǎng)標(biāo)準(zhǔn)所規(guī)定的全部技術(shù)規(guī)范,其中包括CSMA/CD協(xié)議、以太網(wǎng)幀、全雙工、流量控制以及IEEE 802.3標(biāo)準(zhǔn)中所定義的管理對象。千兆以太網(wǎng)的關(guān)鍵技術(shù)是千兆以太網(wǎng)的MAC層和以太網(wǎng)接口的實(shí)現(xiàn)。隨著多媒體應(yīng)用的普及,干兆以太網(wǎng)必然得到廣泛應(yīng)用。

3 Altera的千兆以太網(wǎng)解決方案

3.1 IP核的支持

Altera提供了可參數(shù)化的千兆以太網(wǎng)megacore解決方案。該方案可在Altera的ArriaGX,CycloneII,CycloneIII系列FPGA上工作,可配置使其包含MAC,PCS,PMA模塊中的一種或多種,配置選擇及相應(yīng)的接口標(biāo)準(zhǔn)。

千兆以太網(wǎng)IP核的功能描述如下:

(1)支持IEEE 802.3標(biāo)準(zhǔn)。

(2)10/100/1 000 Mb,s以太網(wǎng)媒體訪問控制支持半雙工和全雙工工作模式。

(3)多通道MAC,支持最多24端口。

(4)以太網(wǎng)物理層編碼子層1000BASE一X/SGMII標(biāo)準(zhǔn)的自協(xié)商。

(5)接口使用方便。

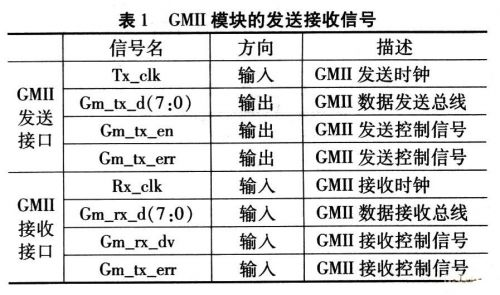

對于千兆以太網(wǎng)控制器的實(shí)現(xiàn),采用表第l行的配置。吉比特級以太網(wǎng)媒體控制器核(GEMAC)是針對1

Gb/s以太網(wǎng)媒體訪問控制器功能的可參數(shù)化的megacore解決方案。

3.2 基于FPGA的千兆以太網(wǎng)MAC控制器實(shí)現(xiàn)方案

3.2.1 整體設(shè)計方案

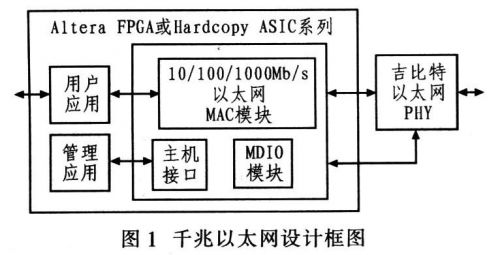

以太網(wǎng)控制器的FPGA設(shè)計工作包括以太網(wǎng)MAC子層的FPGA設(shè)計,MAC子層與上層協(xié)議的接口設(shè)計以及MAC與物理層(PHY)的GMII接口設(shè)計。該以太網(wǎng)控制器的總體結(jié)構(gòu)設(shè)計框圖如圖1所示,整個系統(tǒng)分為MAC模塊,主機(jī)接口模塊和管理數(shù)據(jù)輸入輸出模塊。其中,MAC模塊主要執(zhí)行在全雙工模式下的流量控制,MAC幀實(shí)現(xiàn)發(fā)送和接收功能,其主要操作有MAC幀的封裝與解包以及錯誤檢測,直接提供了到外部物理層器件的并行數(shù)據(jù)接口,物理層處理直接利用商用千兆PHY器件,主要開發(fā)集中在MAC控制器的研究。

管理數(shù)據(jù)輸入輸出模塊提供了標(biāo)準(zhǔn)的IEEE802.3介質(zhì)獨(dú)立接口,可用于連接以太網(wǎng)的鏈路層和物理層。主機(jī)接口則提供以太網(wǎng)控制器與上層協(xié)議(如TCP/IP協(xié)議)之間的接口,用于數(shù)據(jù)的發(fā)送、接收以及對控制器內(nèi)各種寄存器的設(shè)置。

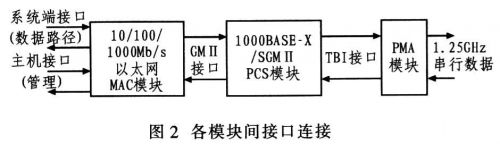

整個系統(tǒng)模塊間的接口連接如圖2所示。其中,PCS和PMA分別代表物理層的物理編碼子層和物理介質(zhì)接入層。

(1)通過MII/GMII接口提供了與以太網(wǎng)物理層(PHY)設(shè)備的無縫連接。

(2)吉比特模式下支持RGMII接口。

(3)可選擇的管理數(shù)據(jù)輸入/輸出模塊為以太網(wǎng)PHY提供管理信息。

(4)為用戶提供基于Aalon—ST的8 bit/32 bit接口。

(5)可選擇的集成物理介質(zhì)介入模塊。

3.2.3 千兆以太網(wǎng)IP核

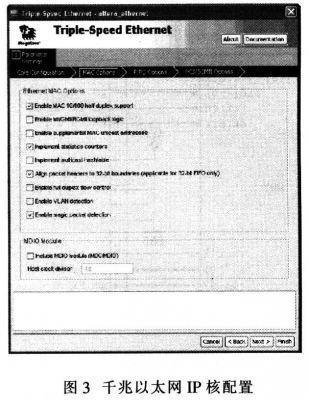

Altera提供三態(tài)以太網(wǎng)MAC控制器IP核,可實(shí)現(xiàn)單條或多條吉比特以太網(wǎng)鏈路,通過交換機(jī)或路由器可與任意以太網(wǎng)端口相連。其配置界面如圖3所示。

整個配置界面可將IP核配置為所需模式并進(jìn)行IP核參數(shù)設(shè)置,將IP核設(shè)置為千兆以太網(wǎng)MAC模塊,內(nèi)部提供FI—FO模塊。可選的PCS模塊由PHY器件提供,這個界面分為4個配置頁面,描述如下:

Core Configuration:核配置選項(xiàng),配置以太網(wǎng)功能模塊,是否包含PCS模塊、FIFO模塊,配置接口類型、端口數(shù)等;

MAC Options:MAC配置選項(xiàng),配置MAC模塊功能;

FIFO Options:FIFO存儲器選項(xiàng),可設(shè)置FlFO存儲器類型以及存儲器數(shù)據(jù)長度;

PCS/SGMII Options:物理介質(zhì)接入層模塊配置頁面,配置物理層。

相應(yīng)的接口信號包括:控制接口信號,復(fù)位信號,MAC系統(tǒng)端信號(包括接收接口信號和發(fā)送接口信號),MAC以太網(wǎng)端信號(包括GMII模塊信號和PHY管理接口信號)。