本文主要概括一下,如何針對(duì)Xilinx+ModelSim進(jìn)行FPGA的仿真設(shè)計(jì)。

1. xHDL仿真器

常用的硬件描述語言的仿真器有很多種,例如,VCS,Ncsim,Affirima,Verilog-XL,SpeedWave,F(xiàn)inisim和 ModelSim。個(gè)人認(rèn)為比較流行的就是ModelSim和Ncsim,像opencores提供的源碼大部分都含有Ncsim仿真支持,或者 ModelSim仿真支持。

1.1 ModelSim簡介

ModelSim仿真器在FPGA/CPLD設(shè)計(jì)中的使用得到了廣泛的應(yīng)用,這是因?yàn)镸odel Technology公司為各個(gè)FPGA/CPLD廠家都提供了OEM版本的ModelSim工具。ModelSim仿真原理是基于事件驅(qū)動(dòng)的,它可支持Verilog和VHDL語言的的單獨(dú)仿真與混合仿真。

1.2 ModelSim版本

ModelSIm仿真工具有許多版本,首先就是他的版本號(hào)很多,這里不多介紹,因?yàn)樗鼰o非就是軟件性能,功能的升級(jí)。這里主要是要說明ModelSim PE/LE/SE之間的區(qū)別:

為了滿足不同用戶的需要,ModelSim每個(gè)版本號(hào)都可以分為PE,LE和SE等類別。其中SE功能是比較完善的,但是它有一個(gè)特點(diǎn)就是,在進(jìn)行仿真前,要首先編譯相應(yīng)的仿真庫(通過設(shè)置,也可以一老永逸),后面會(huì)專門介紹。

在進(jìn)行Xilinx FPGA產(chǎn)品開發(fā)時(shí),我們有時(shí)會(huì)遇到ModelSim XE版本,這是ModelSim的Xilinx OEM版本,里面集成了Xilinx的仿真庫。同樣道理也適用于Altera。

2. 仿真庫的生成

結(jié)合自己的實(shí)際經(jīng)驗(yàn),本文以Verilog + ModelSim SE + Xilinx ISE為例來說明仿真庫的生成。

2.1 仿真庫的命名

在ModelSim中編譯器件的仿真庫時(shí),使用的仿真庫的名稱可以隨意定義,只要滿足操作系統(tǒng)的命明規(guī)則就行。但是在實(shí)際操作中,則不然。

當(dāng)我們使用Xilinx ISE + ModelSim進(jìn)行仿真時(shí),Xilinx ISE會(huì)產(chǎn)生一些對(duì)ModelSim進(jìn)行控制的文件,而在這些文件中,包含仿真庫的映射機(jī)制,因此為了兼容性,這里的仿真庫的命名就是固定的了,而不是任意定義。他們分別是Unisim_ver,Simprim_ver,Xilinxcorelib_ver。

2.2 仿真庫文件的說明

上面提到了ModelSim仿真所需要的3個(gè)基本的庫,這里主要介紹一下他們的作用。

Unisim_ver:如果要做綜合后的仿真,還要編譯這個(gè)庫。即UNISIM,Library of Unified Component simulation models,這個(gè)庫用來做功能仿真。這個(gè)庫包含了Xilinx的所有的標(biāo)準(zhǔn)元件,可以被絕大多數(shù)的綜合工具推論。UNISIM庫被分為VHDL和Verilog兩種。以Verilog為例:Verilog UNISIM庫文件中每一個(gè)元件使用一個(gè)獨(dú)立的文件。根據(jù)器件的不同,這個(gè)庫分為兩個(gè)目錄,對(duì)于FPGA器件家族,源文件位置在$Xilinx\Verilog\src\unisims目錄下,對(duì)于CPLD家族,源文件位置在$Xilinx\Verilog\src\uni9000目錄下。

Simprim_ver:這個(gè)庫用于布局布線后的仿真。對(duì)于Verilog來說,這個(gè)庫位于$Xilinx\Verilog\src\simprimes,對(duì)于VHDL來說,這個(gè)庫位于$Xilinx\VHDL\src\simprimes。

Xilinxcorelib_ver:這個(gè)庫僅僅用來做功能仿真。 但其和Unisim_ver不同,如果設(shè)計(jì)中調(diào)用了CoreGen產(chǎn)生的核,則需要編譯這個(gè)庫。Core Generator HDL Library models, 它包含了適用Core Generator產(chǎn)生的各種IP核的仿真模型。Xilinx的IP核都針對(duì)不同的器件結(jié)構(gòu)作了很好的優(yōu)化,但是對(duì)于使用者來說,大部分只能夠做為黑合來 處理。對(duì)于Verilog來說,其對(duì)應(yīng)的源文件位置所在的位置是$Xilinx\Verilog\src\xilinxcorelib,對(duì)VHDL來說, 其對(duì)應(yīng)的源文件所在的位置是$Xilinx\VHDL\src\xilinxcorelib。

2.3 仿真庫的建立

本節(jié)將以Verilog語言中時(shí)序仿真庫simprimes為例來說明,為ModelSim建立仿真庫。

第一步:將ModelSim根目錄下的配置文件Modelsim.ini屬性由只讀改為可讀寫。這樣做的目的就是為了讓軟件可以記錄仿真庫建立的路徑以及 映射關(guān)系。以后每次啟動(dòng)Modelsim時(shí),軟件會(huì)根據(jù)ModelSim.ini中的配置尋找仿真庫,并且形成映射關(guān)系。

第二步:在這一步,有2種方法可以作。

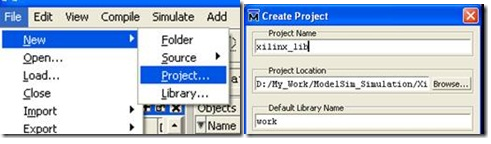

(1) 在modelsim環(huán)境下,新建工程,工程的路徑與你想把庫存儲(chǔ)的路徑一致。這里Project Name: Xilinx_lib;

Project Location: D:/My_Work/ModelSim_Simulation/Xilinx—即仿真庫保存的路徑。如下圖所示:

(2): 在主窗口中選擇[File] / [Change Directory]命令,將工作目錄改到我們想要保存仿真庫的目錄下,即D:/My_Work/ModelSim_Simulation/Xilinx。

以上兩個(gè)方法均可,最終的結(jié)果都是一樣的。

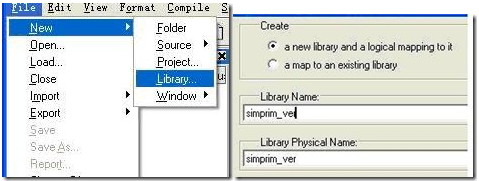

第三步:新建庫,庫名起作simprim_ver。我們首先就是要建的就是這個(gè)庫。

即在主窗口選擇[File] / [New] / [Library]命令,然后根據(jù)下圖設(shè)置[Create]選項(xiàng),[Library Name]選項(xiàng),以及Libray Physical Name]選項(xiàng)(軟件自動(dòng)生成)。如下圖所示:

這一操作實(shí)際上相當(dāng)于在ModelSim主窗口的腳本區(qū)域輸入命令

vlib simprimes_ver

vmap simprimes_ver simprimes_ver

第四步:這一步有兩種方法實(shí)現(xiàn),這兩種方式是等效的

(1): 在modelsim的命令欄上,打下如下命令:

vlog -work simprim_ver $xilinx/verilog/src/simprims/*.v

其中的$xilinx是Xilinx ISE的安裝路徑,你把這個(gè)改成你的就行了。編譯完之后,你會(huì)發(fā)現(xiàn)你的工程文件夾下出現(xiàn)了一個(gè)simprim文件夾,里面又有很多個(gè)文件夾。這些就是我們要的庫了。

(2): 在主窗口選擇[Compile] / [Compile]命令,彈出[Compile Source Files]窗口,然后選擇$xilinx/verilog/src/simprims/目錄下的所有*.v文件,點(diǎn)擊Compile按鈕執(zhí)行編譯。

第五步:按照第三步中的任意一種方式編譯其它兩個(gè)庫,對(duì)應(yīng)的命令行是:

vlog -work unisim_ver $xilinx /verilog/src/unisims/*.v

vlog -work xilinxcorelib_ver $xilinx /verilog/src/XilinxCoreLib/*.v

第六步:庫文件編譯好了以后,為了方便以后使用,可以修改ModelSim.ini配置文件,打開配置文件之后,可添加對(duì)Xilinx仿真庫的映射。經(jīng)過修改后,Xilinx ISE+ ModelSim進(jìn)行各個(gè)階段的仿真就不會(huì)出現(xiàn)任何的錯(cuò)誤了。PS:有的人反映,在仿真過程中,有時(shí)還需要指定庫的路徑,其原因就是ModelSim.ini文件沒有配置正確。

如果還需要其它的仿真庫支持,例如abel_ver, cpld_ver,可按照上述的1~5步完成這些仿真庫的添加。

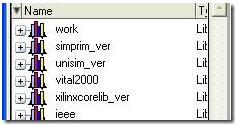

完成上面的步驟后,如果重新打開ModelSim,發(fā)現(xiàn)下面的庫文件的話,就說明,你的仿真環(huán)境建立好了,接下來就可以做你該做的事情了。

3. ModelSim常用命令

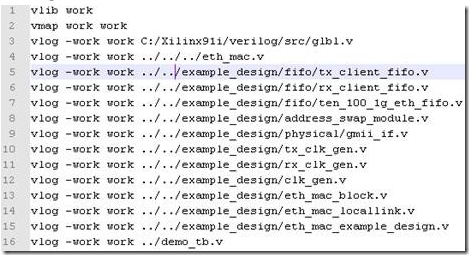

在作FPGA開發(fā)時(shí),由于需要屢次的修改源文件進(jìn)行調(diào)試,因此,每次仿真都不可避免的要進(jìn)行編譯。這道程序比較麻煩,ModelSim提供了一個(gè)捷徑,即我們只需要編寫一個(gè)*.do文件,然后再M(fèi)odelSim命令行里鍵入do *.do就可以替代這一麻煩過程。

下面以Giga Eth MAC開發(fā)仿真為例,說明一下*.do的語法結(jié)構(gòu),如下圖所示:

(1) vlib work >> 由于vlib<庫名>,表示創(chuàng)建一個(gè)庫,因此vlib work表示創(chuàng)建一個(gè)work庫,這里的work是庫的名稱。

(2) vmap work work >>vmap表示映射庫,前一個(gè)work表示以創(chuàng)建的庫的名稱,后一個(gè)work表示當(dāng)前ModelSim工作目錄下的文件夾,即將一個(gè)名為work的庫映射到當(dāng)前目下的work文件夾。

(3) vlog -work work C:/Xilinx91i/verilog/src/glbl.v >> vlog表示編譯源代碼,”-work”表示其后面跟著的參數(shù)表示編譯完的源文件要存放的位置,最后的參數(shù)表示源文件的位置,即該語法表示,將文件 C:/Xilinx91i/verilog/src/glbl.v編譯,得到的編譯后的文件,存放在當(dāng)前工作目錄下的work目錄下。

最終的仿真結(jié)果如下圖所示: