基于FPGA和MB86S02的數(shù)字圖像處理系統(tǒng)設(shè)計(jì)

摘要: 本系統(tǒng)以內(nèi)嵌Nios軟核的FPGA,低級(jí),高級(jí)為核心,并將圖像采集芯片和存儲(chǔ)器等外圍設(shè)備芯片嵌入到系統(tǒng)上,從而實(shí)現(xiàn)圖像的采集處理和顯示,并將處理后的數(shù)據(jù)通過調(diào)制解詞器經(jīng)由PSTN網(wǎng)絡(luò)發(fā)送到接收端(監(jiān)控中心),以便在監(jiān)控中心能夠使用在PC上編寫的上位機(jī)程序?qū)⑻幚砗蟮膱D像顯示出來。

Abstract:

Key words :

圖像處理技術(shù)是信息科學(xué)中近十年來發(fā)展最為迅速的學(xué)科之一。目前,數(shù)字圖像處理技術(shù)巳被廣泛應(yīng)用于航空航天、通信、醫(yī)學(xué)及工業(yè)生產(chǎn)等領(lǐng)域中。但是,如果單純使用現(xiàn)成的專用視頻圖像處理芯片,根本無(wú)法設(shè)計(jì)出具有自主知識(shí)產(chǎn)權(quán)的產(chǎn)品。隨著網(wǎng)絡(luò)技術(shù)、大規(guī)模,超太規(guī)模集成電路(ASIC)以及現(xiàn)場(chǎng)可編程門陣列(FPGA)的發(fā)展,它們?cè)趫D像領(lǐng)域的應(yīng)用越來越廣泛,同時(shí),圖像處理設(shè)計(jì)也正朝著速度快、容量大、體積小、重量輕的方向發(fā)展,這也為圖像處理系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)提供了新的方法和思路。

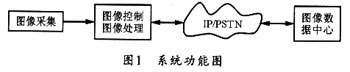

1 系統(tǒng)功能

本系統(tǒng)的功能圖如圖1所示,其結(jié)構(gòu)圖如圖2所示。它以內(nèi)嵌Nios軟核的FPGA,低級(jí),高級(jí)為核心,并將圖像采集芯片和存儲(chǔ)器等外圍設(shè)備芯片嵌入到系統(tǒng)上,從而實(shí)現(xiàn)圖像的采集處理和顯示,并將處理后的數(shù)據(jù)通過調(diào)制解詞器經(jīng)由PSTN網(wǎng)絡(luò)發(fā)送到接收端(監(jiān)控中心),以便在監(jiān)控中心能夠使用在PC上編寫的上位機(jī)程序?qū)⑻幚砗蟮膱D像顯示出來。

2圖像處理的實(shí)現(xiàn)

2.1圖像采集模塊

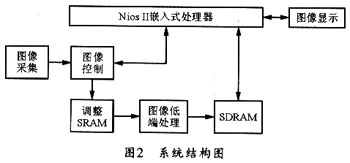

圖像采集模塊采用富士通公司生產(chǎn)的一款375x293(10萬(wàn))像素(即CIF恪式)的CMOS圖像傳感器MV86S02,該芯片在片內(nèi)集成了色彩信號(hào)處理器。這種將CMOS圖像傳感器與色彩信號(hào)處理器集成到一個(gè)芯片內(nèi)部的技術(shù)可以降低系統(tǒng)功耗和體積。由于MV86S02包含了圖像采集的所有前端處理功能,并可以直接輸出數(shù)字信號(hào)。因而大大方便了用戶的使用,簡(jiǎn)化了開發(fā)工作,同時(shí)又提高了系統(tǒng)的性能。

FPGA通過與7MB86S02型CMOS圖像模塊的連接,來通過VHDL程序?qū)B86S02所采集到的數(shù)字圖像數(shù)據(jù)存儲(chǔ)在SRAM中,以備后續(xù)的LCD顯示和數(shù)據(jù)處理使用,然后還可以由UART模塊或RTL8019模塊把已經(jīng)存儲(chǔ)的圖像數(shù)據(jù)發(fā)送到PC機(jī),最后在PC機(jī)上的接收程序的控制下來顯示接收的圖像。圖像采集模塊的時(shí)序仿真結(jié)果如圖3所示。

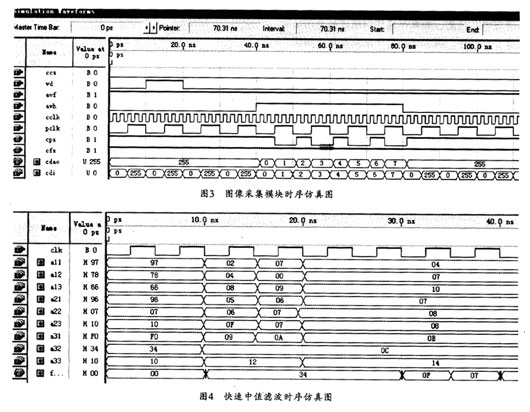

2 2圖像低端處理模塊

圖像的低級(jí)處理工作的數(shù)據(jù)量很大,因而要求速度要快.但算法相對(duì)簡(jiǎn)單。本文在FPGA中實(shí)現(xiàn)了低端處理的中值濾波的快速處理算法的硬件電路,中值濾波窗口內(nèi)所有像素點(diǎn)的度灰值都會(huì)從小到大(或O從大到小)順序排列,并以度灰值序列的中間值來代替窗口中心像索點(diǎn)的灰度值。這就意味著執(zhí)行過程中要進(jìn)行大量的比較和賦值運(yùn)算,改進(jìn)的快速濾波算法的設(shè)計(jì)思想是將二維濾波陣列分解為一維來進(jìn)行計(jì)算。即首先求出濾波窗口中水平各行像素點(diǎn)灰度值的中值,再求出這些水平各行中值的中值,并以此作為濾波結(jié)果。圖4給出了快速中值濾波的時(shí)序仿真圖。

2 3圖像的高級(jí)處理和顯示

高級(jí)的圖像處理可以參考低級(jí)處理方式來實(shí)現(xiàn)。但運(yùn)算的數(shù)據(jù)量較小,算法相對(duì)復(fù)雜,同時(shí)還具有一定的串行性。此次如繼續(xù)用硬件實(shí)現(xiàn),就要占用大量的硬件資源,因此,可以采用嵌入式的CPU來完成。由于CUu與FPGA的結(jié)構(gòu)有很大的帶寬,進(jìn)行數(shù)據(jù)交換也很方便,因此,本文基于FPGA的可編程片上系統(tǒng)(SOPC)技術(shù),將圖像的高級(jí)處理由NiosⅡ核CPU結(jié)合定制指令和外圍電路來實(shí)現(xiàn),以提高處理速度,

而將圖像顯示叉由嵌入NiosⅡ處理器和VGA顯示控制器來完成。

3結(jié)束語(yǔ)

以內(nèi)嵌Nios軟核的FPGA為核心處理器,可以完成圖像的采集控制,低級(jí),高級(jí)圖像處理以及圖像顯示的設(shè)計(jì)。由于基于FPGA的可編程片上系統(tǒng)(SOPC)技術(shù)和大規(guī)模高性能的FPGA豐富資源。因此,利用嵌人NiosⅡ處理器和必要的外圍電路,可使圖像處理在速度、功耗、靈活性、開發(fā)周期和成本控制方面都得到很大的改進(jìn)。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。