1 系統(tǒng)功能及結(jié)構(gòu)

系統(tǒng)主要目的是設(shè)計一個16位的VFC式AD轉(zhuǎn)換器,利用積分原理,將輸入電壓(或電流)轉(zhuǎn)換成頻率輸出。采用計數(shù)頻率高的CPLD器件實現(xiàn)測頻,單片機控制CPLD的測頻操作和頻率的計算。

用V /F轉(zhuǎn)換器完成AD轉(zhuǎn)換,需要1個定時器和2路計數(shù)器,計數(shù)器的計數(shù)頻率限制了V /F器件輸出頻率的提高。本設(shè)計采用計數(shù)頻率更高的CPLD器件和單片機共同組成測速模塊, CPLD通用性好,避免了對于專用器件的依賴,降低了因?qū)S闷骷.a(chǎn)或出現(xiàn)供貸問題所帶來的風(fēng)險,同時實現(xiàn)所需的控制。

VFC式AD 轉(zhuǎn)換器脈沖頻率與輸入電壓成比例,其精度高、線性度好、轉(zhuǎn)換速度居中、轉(zhuǎn)換位數(shù)與速度可調(diào)、與CPU的連線最少,且增加轉(zhuǎn)換位數(shù)時不會增加與CPU的連線,因此, VFC為AD 轉(zhuǎn)換技術(shù)提供了一種廉價而有效的解決辦法。

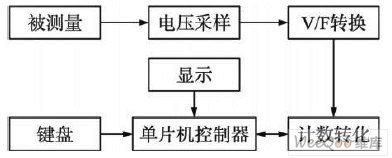

系統(tǒng)總體可以劃分為電壓采樣部分、模擬- 數(shù)字轉(zhuǎn)化部分,控制部分。其中電壓采樣部分包括:精密測試電壓源。模擬- 數(shù)字轉(zhuǎn)化部分包括:電壓放大和偏置,V /F轉(zhuǎn)換模塊,計數(shù)轉(zhuǎn)化模塊。控制部分包括:控制器模塊,鍵盤,顯示模塊,系統(tǒng)原理框如圖1所示。

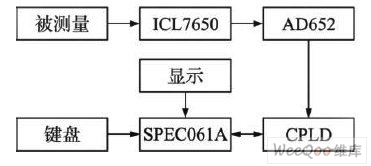

為實現(xiàn)各模塊的功能,分別選取了較好的方案實現(xiàn): ①精密基準(zhǔn)源,精密低溫漂高檔基準(zhǔn)源,分壓;②電壓放大及偏置,運算放大器ICL7650; ③V /F轉(zhuǎn)換,采用AD652芯片; ④頻率測試,采用CPLD (復(fù)雜可編程邏輯器件) ; ⑤控制器,采用凌陽的SPEC061A單片機; ⑥顯示,采用液晶屏; ⑦電氣隔離,采用光電耦合,所設(shè)計的系統(tǒng)如圖2所示。

圖1 系統(tǒng)原理框圖

圖2 所設(shè)計的系統(tǒng)框圖

2 系統(tǒng)硬件設(shè)計

2. 1 精密測試基準(zhǔn)源

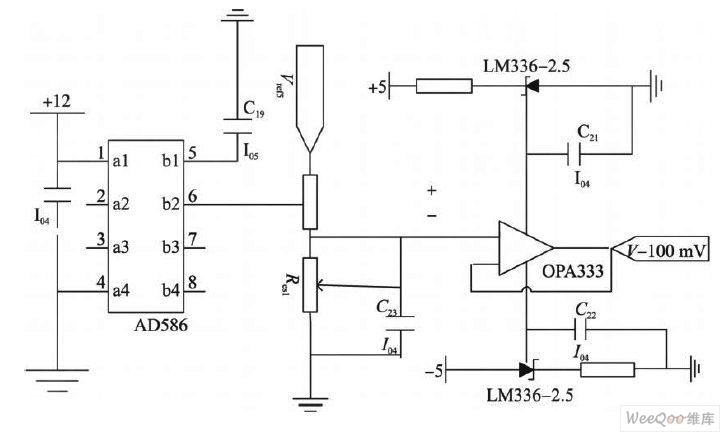

對于16位的AD轉(zhuǎn)換器,滿幅度輸入電壓僅為100 mV,如果要測試它的性能,則需要極高精度和非常低溫漂的基準(zhǔn)源, 電路原理如圖3 所示。

AD586是AD公司高精度5 V的基準(zhǔn)電壓源,溫漂低至2 10 - 6 /℃,噪聲為100 nV /Hz,通過固定電阻和可調(diào)電阻進行分壓產(chǎn)生0 ~100 mV 的電壓。為了增加電壓的負(fù)載能力,須進行電壓跟隨。OPA333是零漂移精密運放,漂移最大為0. 05μV /℃。同時采用兩個2. 5 V的基準(zhǔn)源LM336以降低電源波動的影響。LM336 的輸出電流為10 mA, 可滿足OPA33的需要。分壓用的電阻為指針式10 圈可調(diào),可以達到理想的精度。

圖3 基準(zhǔn)源電路原理圖

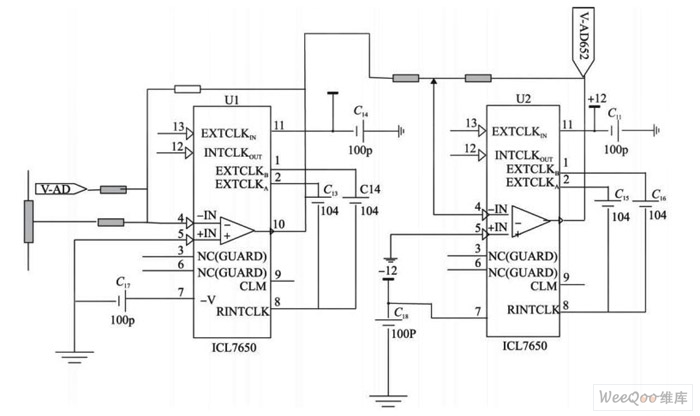

2. 2 電壓的放大及偏置

0~100 mV 的電壓不能直接送給V /F 變換AD652,而必須經(jīng)過精密放大和進行電位的偏置,這樣才能達到設(shè)計的精度。選擇具有斬波穩(wěn)定功能的ICL7650運算放大器,它可以提供低的偏置電 流(10pA) 、偏置電壓和相對時間、溫度的穩(wěn)定性。輸入的0~100 mV電壓經(jīng)過40倍的放大后,產(chǎn)生0~4 V的輸出,因為AD652在0 V輸入的情況下,輸出頻率也是0,這樣計數(shù)得到頻率難以達到16 位的精度,所以將輸入(0~4 V)的直流偏置設(shè)置為1 V,從而產(chǎn)生1~5 V的輸入信號送給AD652;運放的電阻須選用1 /1 000 精度的,保證了V /F變換的精度。

其原理圖如圖4所示。

2. 3 V /F轉(zhuǎn)換電路

電壓/頻率轉(zhuǎn)換即V /F轉(zhuǎn)換,是將一定的輸入電壓信號按線性的比例關(guān)系轉(zhuǎn)換成頻率信號,當(dāng)輸入電壓變化時,輸出頻率也響應(yīng)變化。

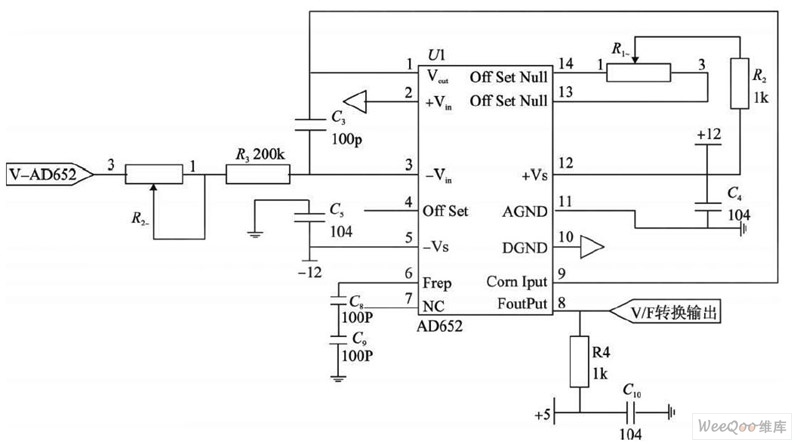

本設(shè)計采用專用集成芯片AD652,輔以的外圍電路即可實現(xiàn)V /F轉(zhuǎn)換,如圖5所示。AD652是美國ANALOG DEV ICES公司推出的高精度電壓頻率(V /F)轉(zhuǎn)換器,它由積分器、比較器、精密電流源、單穩(wěn)多諧振蕩器和輸出晶體管組成。該電路在±15 V電源電壓下,功耗電流小于15 mA,滿刻度為1 MHz時其非線性度小于0. 07 % , 最佳溫度穩(wěn)定性為±150 ppm /℃。用AD652實現(xiàn)V /F轉(zhuǎn)換,可以滿足較高的滿刻度頻率響應(yīng)和較低的最佳溫度穩(wěn)定性。

圖5 V /F轉(zhuǎn)換電路

由于使用外部時鐘設(shè)置滿量程輸出頻率,AD652可以獲得更高的線性度和穩(wěn)定性。通過使用同一時鐘驅(qū)動AD652和設(shè)置計數(shù)時間閘門,轉(zhuǎn)換精度與時鐘頻率無關(guān),不因時鐘頻率的改變而改變。

2. 4 基于CPLD的頻率計電路

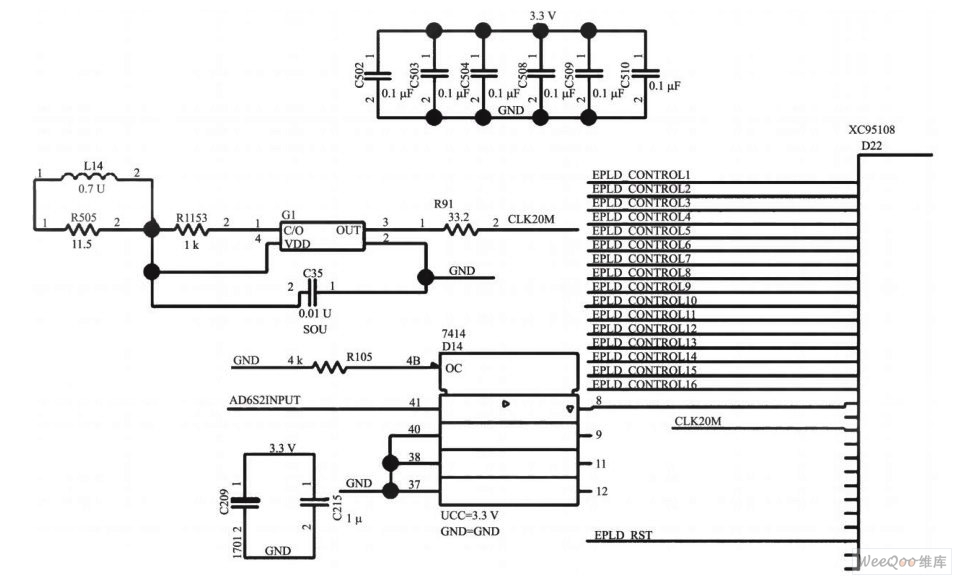

在本系統(tǒng)中, CPLD采用美國XIL INX公司生產(chǎn)的XC95108CPLD (復(fù)雜可編程邏輯器件) ,其片內(nèi)有108個宏, 2 400個門,頻率可以達125 MHz,引腳間延時715 ns,供電電壓5 V或313 V的在系統(tǒng)可編程器件,其可供用戶使用的I/O口數(shù)在64個以上。

XC95108采用FLASH編程工藝,可反復(fù)擦寫,所設(shè)計的電路如圖6所示。

由于輸入的信號是交流信號而CPLD (可編程邏輯器件)和施密特觸發(fā)器是數(shù)字芯片,不識別負(fù)信號,需將輸入交流信號變?yōu)橹绷餍盘枺脙蓚€電阻實現(xiàn)電壓鉗位功能,鉗位后的信號經(jīng)7414 (施密特觸發(fā)器)整形為方波后直接輸入CPLD 對其計數(shù)。

由于CPLD可以實現(xiàn)高速響應(yīng),可以實現(xiàn)準(zhǔn)確計數(shù)。

頻率計測得的數(shù)據(jù)為此系統(tǒng)的AD轉(zhuǎn)換結(jié)果,轉(zhuǎn)換精度受基準(zhǔn)晶振和AD652的V /F滿刻度時的量程的影響,由于CPLD 的基準(zhǔn)晶振選用的是20MHz的高精度晶振。設(shè)計的AD 轉(zhuǎn)換頻率為50kHz,所以在計數(shù)周期內(nèi)基準(zhǔn)晶振脈沖個數(shù)為400,CPLD因為隨機時間出現(xiàn)的誤差僅為一個脈沖,而AD652的滿刻度頻率高,可達 1MHz,所以精度可達到幾千分之一。

圖6 基于CPLD的頻率計電路原理圖

2. 5 單片機控制電路

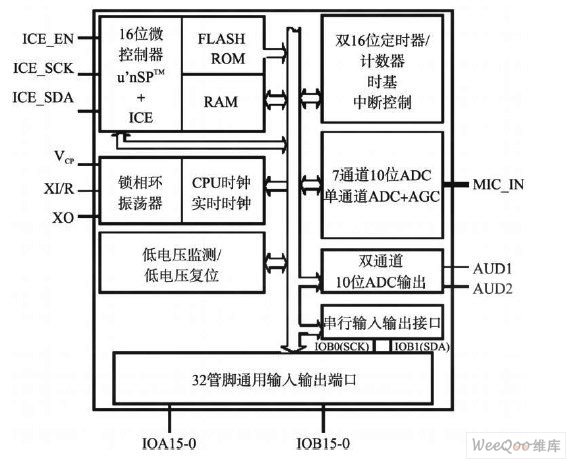

控制部分采用凌陽SPEC061A 單片機。

SPCE061A是凌陽科技新推出的一個16位結(jié)構(gòu)的微控制器,它在2. 6~3. 6 V工作電壓范圍內(nèi)的工作速度范圍為0. 32~49. 152MHz,較高的工作速度使其應(yīng)用領(lǐng)域更加拓寬。2 K字節(jié)SRAM和32 K字閃存ROM僅占一頁存儲空間, 32位可編程的多功能I/O端口;兩個16位定時器/計數(shù)器; 32 768 Hz實時時鐘;低電壓復(fù)位/監(jiān)測功能; 8通道10位模- 數(shù)轉(zhuǎn)化輸入并具有自動增益控制功能的麥克風(fēng)輸入方式:雙通道10位DAC方式的音頻輸出功能等。SPCE061A是數(shù)字聲音和語音識別產(chǎn)品的一種最經(jīng)濟的 應(yīng)用。

在本系統(tǒng)中, SPCE061A主要實現(xiàn)CPLD信息讀取,鍵盤接口和顯示模塊控制等功能。

圖7 單片機結(jié)構(gòu)框圖

2. 6 顯示接口設(shè)計

在顯示方面,由于LCD (L iquidCrystalD ISp lay)具有以下特點:

(1)低工作電壓,低功耗。

(2)顯示柔和,字跡清晰。

(3)不怕強光照射,光照越強,對比度越大,顯示效果越好。

(4)體積小,重量輕,平板型。

(5)可靠性高,壽命長。

因此本設(shè)計采用128 ×64的圖形點陣液晶顯示器來顯示頻率流量信息,液晶采用4行顯示,顯示信息豐富,可以滿足不同用戶的需求。同時,該液晶采用串口傳輸數(shù)據(jù),每秒刷屏一次,節(jié)約了單片機的資源,為今后的繼續(xù)開發(fā)和升級打下基礎(chǔ)。

2. 7 其它輔助抗干擾措施

一般來說,測控系統(tǒng)的功能設(shè)計與制作并不復(fù)雜,功能設(shè)計不過的是系統(tǒng)設(shè)計的起點,系統(tǒng)能否在運行過程中準(zhǔn)確無誤地實現(xiàn)這些功能才是系統(tǒng)設(shè)計的關(guān) 鍵。由于實際工作環(huán)境中存在各種各樣的干擾源,這些干擾源對系統(tǒng)的可靠運行往往會產(chǎn)生不利,甚至?xí)a(chǎn)生意想不到事,更有甚者的是造成整個系統(tǒng)的癱瘓和無法 工作運行,導(dǎo)致實驗生產(chǎn)設(shè)備的損壞和事故的發(fā)生,因此,測控系統(tǒng)的抗干擾防范措施在整個系統(tǒng)的設(shè)計中占有舉足輕重的位置。本設(shè)計增加了如耦合電路、后備電 源監(jiān)測系統(tǒng)、印刷電路板等硬件抗干擾設(shè)計,減少干擾源對系統(tǒng)的可靠運行所帶來的不利影響。

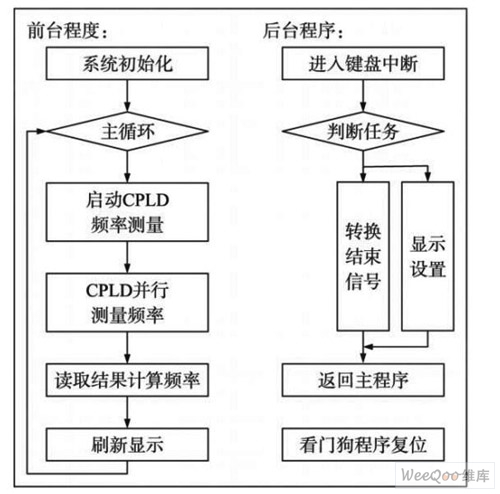

3 系統(tǒng)通信流程及軟件的實現(xiàn)

系統(tǒng)中的應(yīng)用軟件是根據(jù)系統(tǒng)功能要求設(shè)計的,總的原則主要從以下幾方面考慮:

(1)根據(jù)軟件功能要求,將系統(tǒng)軟件分成若干個相對獨立的部分。根據(jù)它們之間的聯(lián)系和時間上的關(guān)系,設(shè)計出合理的軟件總體結(jié)構(gòu),使其清晰、簡 潔、流程合理;(2)采用結(jié)構(gòu)化程序設(shè)計,各功能程序?qū)嵭心K化、子程序化。既便于調(diào)試、鏈接,又便于移植、修改;(3)建立正確的數(shù)學(xué)模型。根據(jù)功能要 求,描述出各個輸入和輸出變量之間的數(shù)學(xué)關(guān)系,它是關(guān)系到系統(tǒng)性能好壞的重要因素;(4)為提高軟件設(shè)計的總體效率,以簡明、直觀的方法對任務(wù)進行描述, 在編寫應(yīng)用軟件之前,繪制出程序流程圖。這不僅是程序設(shè)計的一個重要組成部分,而且是決定成敗的關(guān)鍵部分;(5)合理分配系統(tǒng)資源,其中最關(guān)鍵的是片內(nèi)內(nèi) 存分配。分配時應(yīng)充分發(fā)揮其特一長,做到物盡其用;(6)加強軟件的抗干擾設(shè)計,提高計算機應(yīng)用系統(tǒng)的可靠性。根據(jù)以上設(shè)計原則,軟件設(shè)計采用模塊結(jié)構(gòu), 整個軟件包括主程序、采樣子程序數(shù)據(jù)處理子程序、顯示子程序等模塊。

根據(jù)以上原則要求設(shè)計了系統(tǒng)的軟件程序流程圖如圖8所示:

圖8 控制程序流程圖。

4 測試結(jié)果及分析

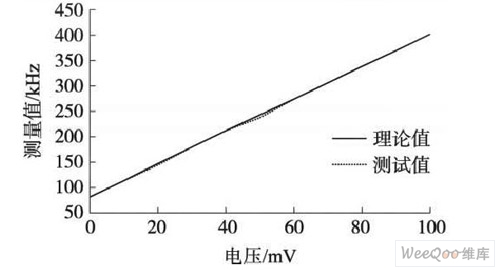

對所設(shè)計的電路的V /F轉(zhuǎn)換的性能進行了測試,結(jié)果如圖9所示。

圖9 V /F轉(zhuǎn)換測量對比值

通過示波器觀察,每秒鐘50 000個脈沖,即轉(zhuǎn)換頻率為50 kHz。由測試結(jié)果圖可知此次VF轉(zhuǎn)換滿足了高分辨率和較低的非線性度的要求,分辨率可達16位,線性誤差<0. 2 %,轉(zhuǎn)換頻率可達50 kHz。

5 結(jié)論

本次設(shè)計應(yīng)用V /F轉(zhuǎn)換器實現(xiàn)高分辨率AD轉(zhuǎn)換,具有較高的滿刻度頻率響應(yīng)、低功耗和較低的非線性度等特點,廣泛應(yīng)用于儀器儀表對溫度的控制中,滿足對設(shè)定溫度控制穩(wěn)定 性的要求。在系統(tǒng)設(shè)計中采用CPLD實現(xiàn)頻率計數(shù)功能,是數(shù)字系統(tǒng)精確測量頻率一種方法:在采樣時間內(nèi)同時對標(biāo)準(zhǔn)頻率信號和被測頻率信號計數(shù)。采樣完成 后,把二者的計數(shù)值相比,再乘以標(biāo)準(zhǔn)頻率就可以得到被測頻率的精確值。