1 系統(tǒng)方案設(shè)計(jì)

設(shè)計(jì)的數(shù)字示波器系統(tǒng)主要使用了Xilinx系統(tǒng)的開發(fā)環(huán)境,并在此環(huán)境內(nèi)部建立了AD采樣控制模塊、鍵盤控制模塊、VGA顯示模塊等多個(gè)模塊,從很大程度上減少了硬件電路的搭建,也因此提高了系統(tǒng)的穩(wěn)定性和可靠性,系統(tǒng)框圖如圖1所示。

另外,設(shè)計(jì)使用XPS將32位的MicroBlaze微處理器嵌入到了FPGA中,實(shí)現(xiàn)了可編程片的嵌入以及在可編程片上的系統(tǒng)設(shè)計(jì)。MieroBlaze通過(guò)LBM總線訪問(wèn)片上的存儲(chǔ)模塊BlockRAM,然后通過(guò)OPB總線上掛接外設(shè)進(jìn)行接口連接和驅(qū)動(dòng)。

VGA顯示部分采用雙緩沖機(jī)制進(jìn)行工作,在FPGA內(nèi)部建立RAM,按照一定時(shí)序降RAM內(nèi)的緩存數(shù)據(jù)映射到VGA顯示屏上。

2 硬件設(shè)計(jì)

2.1 信號(hào)調(diào)理電路模塊

信號(hào)調(diào)理電路模塊,對(duì)輸入的模擬信號(hào)進(jìn)行處理,由于輸入電壓幅度為-2.5~+2.5 V之間,而后一級(jí)的AD模塊采用了12位的高速A/D轉(zhuǎn)換芯片ADS804,只能對(duì)0~2 V的電壓進(jìn)行模/數(shù)轉(zhuǎn)換,故需要將輸入電壓先抬升為0~5 V,在應(yīng)用運(yùn)算放大器進(jìn)行比例縮小,達(dá)到0~2 V的模數(shù)轉(zhuǎn)換要求。

2.2 A/D轉(zhuǎn)換電路

A/D轉(zhuǎn)換模塊采用存儲(chǔ)采樣數(shù)據(jù)的并行數(shù)據(jù)處理方法,這樣可以使硬件電路得到最大程度的簡(jiǎn)化,同時(shí)也提高了系統(tǒng)的穩(wěn)定性。AD部分的采樣,選用實(shí)時(shí)采樣技術(shù)。能夠捕獲到單個(gè)信號(hào)。采樣速率為10 MHz,即在最高頻率1 MHz時(shí),實(shí)時(shí)采樣可以在每周期采10個(gè)點(diǎn)以保證取到一個(gè)完整的信號(hào)波形。

2.3 觸發(fā)電路模塊

觸發(fā)電路模塊屬于外觸發(fā),對(duì)模擬信號(hào)實(shí)現(xiàn)任意電平觸發(fā),該模塊采用電壓比較器來(lái)實(shí)現(xiàn)單次觸發(fā)。

2.4 存儲(chǔ)模塊

存儲(chǔ)模塊包括內(nèi)存儲(chǔ)和外存儲(chǔ)兩部分,使用外部電路進(jìn)行搭建的為外存儲(chǔ),內(nèi)存儲(chǔ)在軟件部分進(jìn)行說(shuō)明。

外部非易失性存儲(chǔ)器模塊采用存儲(chǔ)容量為16 KB的E2PROM芯片24C128,該芯片作為手動(dòng)存儲(chǔ)的存儲(chǔ)介質(zhì),從而實(shí)現(xiàn)掉電不丟失的設(shè)計(jì)目的。

2.5 VGA顯示模塊

VGA顯示模塊是建于FPGA內(nèi)的雙緩沖機(jī)制,由嵌入的MicroBlaze軟核進(jìn)行控制,能夠進(jìn)行多個(gè)頁(yè)面間的切換。另外,每個(gè)界面,可以實(shí)現(xiàn)中文信息、彩色通道和所測(cè)輸入波形的顯示,并可控制顯示內(nèi)容的顯示顏色。

2.6 鍵盤模塊

4×4矩陣鍵盤模塊實(shí)現(xiàn)人機(jī)交互。

通過(guò)鍵盤,可以對(duì)示波器的數(shù)字通道、模擬通道、混合通道、存儲(chǔ)、回放、波形左移、波形右移等功能進(jìn)行選擇。

3 基于FPGA的軟件設(shè)計(jì)

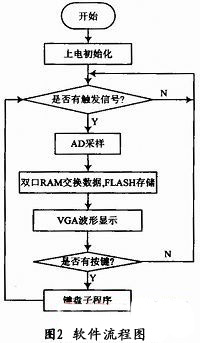

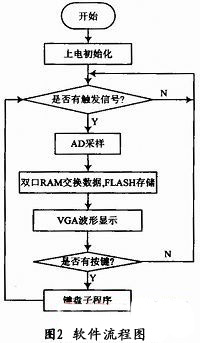

FPGA的硬件主要包括:觸發(fā)電路模塊、數(shù)字信號(hào)發(fā)生模塊、存儲(chǔ)模塊、鍵盤模塊、VGA顯示模塊等5個(gè)部分,軟件流程圖如圖2所示。

1 系統(tǒng)方案設(shè)計(jì)

設(shè)計(jì)的數(shù)字示波器系統(tǒng)主要使用了Xilinx系統(tǒng)的開發(fā)環(huán)境,并在此環(huán)境內(nèi)部建立了AD采樣控制模塊、鍵盤控制模塊、VGA顯示模塊等多個(gè)模塊,從很大程度上減少了硬件電路的搭建,也因此提高了系統(tǒng)的穩(wěn)定性和可靠性,系統(tǒng)框圖如圖1所示。

另外,設(shè)計(jì)使用XPS將32位的MicroBlaze微處理器嵌入到了FPGA中,實(shí)現(xiàn)了可編程片的嵌入以及在可編程片上的系統(tǒng)設(shè)計(jì)。MieroBlaze通過(guò)LBM總線訪問(wèn)片上的存儲(chǔ)模塊BlockRAM,然后通過(guò)OPB總線上掛接外設(shè)進(jìn)行接口連接和驅(qū)動(dòng)。

VGA顯示部分采用雙緩沖機(jī)制進(jìn)行工作,在FPGA內(nèi)部建立RAM,按照一定時(shí)序降RAM內(nèi)的緩存數(shù)據(jù)映射到VGA顯示屏上。

2 硬件設(shè)計(jì)

2.1 信號(hào)調(diào)理電路模塊

信號(hào)調(diào)理電路模塊,對(duì)輸入的模擬信號(hào)進(jìn)行處理,由于輸入電壓幅度為-2.5~+2.5 V之間,而后一級(jí)的AD模塊采用了12位的高速A/D轉(zhuǎn)換芯片ADS804,只能對(duì)0~2 V的電壓進(jìn)行模/數(shù)轉(zhuǎn)換,故需要將輸入電壓先抬升為0~5 V,在應(yīng)用運(yùn)算放大器進(jìn)行比例縮小,達(dá)到0~2 V的模數(shù)轉(zhuǎn)換要求。

2.2 A/D轉(zhuǎn)換電路

A/D轉(zhuǎn)換模塊采用存儲(chǔ)采樣數(shù)據(jù)的并行數(shù)據(jù)處理方法,這樣可以使硬件電路得到最大程度的簡(jiǎn)化,同時(shí)也提高了系統(tǒng)的穩(wěn)定性。AD部分的采樣,選用實(shí)時(shí)采樣技術(shù)。能夠捕獲到單個(gè)信號(hào)。采樣速率為10 MHz,即在最高頻率1 MHz時(shí),實(shí)時(shí)采樣可以在每周期采10個(gè)點(diǎn)以保證取到一個(gè)完整的信號(hào)波形。

2.3 觸發(fā)電路模塊

觸發(fā)電路模塊屬于外觸發(fā),對(duì)模擬信號(hào)實(shí)現(xiàn)任意電平觸發(fā),該模塊采用電壓比較器來(lái)實(shí)現(xiàn)單次觸發(fā)。

2.4 存儲(chǔ)模塊

存儲(chǔ)模塊包括內(nèi)存儲(chǔ)和外存儲(chǔ)兩部分,使用外部電路進(jìn)行搭建的為外存儲(chǔ),內(nèi)存儲(chǔ)在軟件部分進(jìn)行說(shuō)明。

外部非易失性存儲(chǔ)器模塊采用存儲(chǔ)容量為16 KB的E2PROM芯片24C128,該芯片作為手動(dòng)存儲(chǔ)的存儲(chǔ)介質(zhì),從而實(shí)現(xiàn)掉電不丟失的設(shè)計(jì)目的。

2.5 VGA顯示模塊

VGA顯示模塊是建于FPGA內(nèi)的雙緩沖機(jī)制,由嵌入的MicroBlaze軟核進(jìn)行控制,能夠進(jìn)行多個(gè)頁(yè)面間的切換。另外,每個(gè)界面,可以實(shí)現(xiàn)中文信息、彩色通道和所測(cè)輸入波形的顯示,并可控制顯示內(nèi)容的顯示顏色。

2.6 鍵盤模塊

4×4矩陣鍵盤模塊實(shí)現(xiàn)人機(jī)交互。

通過(guò)鍵盤,可以對(duì)示波器的數(shù)字通道、模擬通道、混合通道、存儲(chǔ)、回放、波形左移、波形右移等功能進(jìn)行選擇。

3 基于FPGA的軟件設(shè)計(jì)

FPGA的硬件主要包括:觸發(fā)電路模塊、數(shù)字信號(hào)發(fā)生模塊、存儲(chǔ)模塊、鍵盤模塊、VGA顯示模塊等5個(gè)部分,軟件流程圖如圖2所示。

3.1 觸發(fā)電路程序

AD采樣啟動(dòng)后,將從AD進(jìn)來(lái)的數(shù)據(jù)與觸發(fā)字進(jìn)行比較,當(dāng)滿足設(shè)定條件時(shí),會(huì)產(chǎn)生觸發(fā)信號(hào),此信號(hào)送到RAM控制器端。通過(guò)對(duì)外部觸發(fā)電路發(fā)出觸發(fā)信號(hào)與內(nèi)部的兩路數(shù)字信號(hào)進(jìn)行觸發(fā)的選擇后,RAM控制器得到觸發(fā)后將采樣數(shù)據(jù)寫入到RAM中。當(dāng)RAM在進(jìn)行寫數(shù)據(jù)過(guò)程中觸發(fā)信號(hào)是被抑制的;當(dāng)RAM達(dá)到預(yù)觸發(fā)深度時(shí),釋放觸發(fā)信號(hào),等待下一次觸發(fā)的到來(lái)。

3.2 數(shù)竽信號(hào)發(fā)生程序

利用DDS的原理,在FPGA內(nèi)部生成一個(gè)信號(hào)發(fā)生器。主要包括頻率控制寄存器、高速相位累加器和比較器3部分。具體做法為:使用一個(gè)表示信號(hào)平均值的數(shù)據(jù)與AD采樣得來(lái)的數(shù)據(jù)進(jìn)行比較得到同頻同相的A路信號(hào),再經(jīng)由A信號(hào)觸發(fā)計(jì)數(shù)器,經(jīng)過(guò)合理設(shè)置計(jì)數(shù)脈沖,得到有45°延時(shí),占空比25%的B路信號(hào)。最后對(duì)該相位值計(jì)算數(shù)字化正弦波幅度輸出。

表示信號(hào)平均值的數(shù)據(jù)由MicroBlaze測(cè)量信號(hào)提供。

3.3 存儲(chǔ)程序

存儲(chǔ)模塊分RAM存儲(chǔ)和FLASH存儲(chǔ)RAM存儲(chǔ)使用一個(gè)雙口RAM,寫和讀分開,波形數(shù)據(jù)滿足觸發(fā)條件時(shí)送進(jìn)RAM,存儲(chǔ)了1 024個(gè)點(diǎn),其中前560組送住VGA顯示。

FLASH存儲(chǔ)完成掉電不丟失的存儲(chǔ)目的。20世紀(jì)使用開發(fā)板上的一塊型號(hào)為AM29LV160DB的FLASH存儲(chǔ)器,當(dāng)按下存儲(chǔ)健后,F(xiàn)LASH把RAM中的數(shù)據(jù)寫到FLASH中,根據(jù)資料中的讀寫時(shí)序圖,使用狀態(tài)機(jī)實(shí)現(xiàn)這個(gè)過(guò)程,當(dāng)按下回顯的按鍵時(shí)將FLASH中的數(shù)據(jù)讀回圖像顯示RAM,再顯示出來(lái)。

3.4 鍵盤程序

鍵盤采用4×4矩陣鍵盤,使用FPGA進(jìn)行掃描控制,實(shí)現(xiàn)人機(jī)交互。

鍵盤子程序主要包括數(shù)字通道、模擬通道、混合通道、存儲(chǔ)、回放、波形左移、波形右移、垂直靈敏度檔位設(shè)置,掃描速度檔位設(shè)置等功能與按鍵的對(duì)應(yīng)。

3.4.1 顯示分辨率分析

垂直方向劃分為10 div,設(shè)置3檔垂直靈敏度:1 000 mV/div,100 mV/div和10 V/div,即每div可代表1 000 mV,100 mV和10 mV。

A/D轉(zhuǎn)換模塊的模擬信號(hào)輸入端的輸入信號(hào)電壓為0~2 V,當(dāng)示波器滿刻度顯示時(shí),被測(cè)信號(hào)的幅度將分別為:V11=1 V/div×10 div=10 V,V12=0.1 V/div×10 div=1 V,V13=10 mv/div×10 div=100 mV。A/D轉(zhuǎn)換器的滿刻度輸入值為Vmax=2 V,程控放大器電路的增益AN=Vmax/VIn,其中N=1,2,3,對(duì)應(yīng)于3檔不同垂直靈敏度的增益分別為:A1=2/10=0.2;A2=2/1=2;A3=2/0.1=20。

A/D轉(zhuǎn)換器的滿刻度輸入值為Vmax=5 V《10 V,將AD采樣的值和數(shù)字信號(hào)的值據(jù)當(dāng)前檔位進(jìn)行計(jì)數(shù)存儲(chǔ),即1μs/div時(shí)每10個(gè)點(diǎn)保存一個(gè),1 ms,/div時(shí)每10 000個(gè)點(diǎn)保存一個(gè),1 s/div時(shí)每采樣10 000 000個(gè)點(diǎn)保存一個(gè)。

3.4.2 掃描速率分析

A/D的轉(zhuǎn)換速率取決于被測(cè)信號(hào)的頻率范圍,或DSO對(duì)掃描速度的要求,設(shè)計(jì)掃描速度含1 ms/div,1μs,/div,1 s/div三檔,通過(guò)FPGA內(nèi)部建立分頻電路實(shí)現(xiàn)了最高采樣率16 MS/s,每10倍頻步進(jìn),共六檔,增加了該示波器的實(shí)用性。水平顯示分辨率為64點(diǎn)/div,以保證顯示波形清晰穩(wěn)定。

3.5 VGA顯示部分

VGA顯示模塊使用雙緩沖機(jī)制,軟核MicroBlaze通過(guò)讀寫顯存來(lái)控制VGA顯示。VGA顯示可顯示3種顏色,利用了SOPC的優(yōu)勢(shì)。GRAM位寬32b,大大提高了FPGA刷屏的速度。vga_dn與GRAM對(duì)內(nèi)嵌的MCU設(shè)計(jì)成為BlackBox,MCU只需向相應(yīng)地址發(fā)送合適數(shù)據(jù)即可顯示想要的波形。本設(shè)計(jì)主要實(shí)現(xiàn)了的顯示為:底色,漢字,示波器的顯示框,波形數(shù)據(jù)。通過(guò)取字摸的方式,可在顯示屏上顯示中文信息。當(dāng)部分的數(shù)據(jù)進(jìn)行綜合時(shí),這幾部分的數(shù)據(jù)各自有不同的優(yōu)先級(jí),當(dāng)多部分重疊時(shí),根據(jù)優(yōu)先級(jí)顯示出來(lái)。

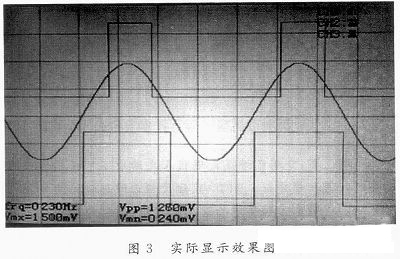

4 總體效果

圖3為同時(shí)顯示2個(gè)數(shù)字通道和1個(gè)模擬通道的界面,通道1(CH1)為模擬通道,通道2(CH2)和通道3(CH3)為數(shù)字通道,輸入信號(hào)為一正弦波,峰一峰值為1.2 V,通道2,設(shè)定輸入信號(hào)信號(hào)電壓大于0為高電平,反之為低電平,故通道2為占空比為50%的矩形波。通道3設(shè)定輸入信號(hào)大于3.3 V為高電平,反之為低電平,故在本圖上通道3為占空比約為25%的矩形波。由圖可知觀察值與計(jì)算值相符。

5 結(jié)語(yǔ)

設(shè)計(jì)實(shí)現(xiàn)了一款基于FPGA的VGA顯示的多通道數(shù)字存儲(chǔ)示波器。FPGA的高速性比其他控制芯片更適合于高速數(shù)據(jù)的采集和處理,另外FPGA內(nèi)部存儲(chǔ)模塊在完成輸入信號(hào)的量化存儲(chǔ)速度上有著外接RAM無(wú)法比擬的優(yōu)勢(shì)。通過(guò)測(cè)試,設(shè)計(jì)系統(tǒng)比較好地完成了各項(xiàng)設(shè)計(jì)要求。