可重構(gòu)技術(shù)是指利用可重用的軟硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計(jì)方法。常規(guī)SRAM工藝的FPGA都可以實(shí)現(xiàn)重構(gòu),利用硬件復(fù)用原理,本文設(shè)計(jì)的可重構(gòu)控制器采用ARM核微控制器作為主控制器,以FPGA芯片作為協(xié)處理器配合主控制器工作。用戶事先根據(jù)需求設(shè)計(jì)出不同的配置方案,并存儲(chǔ)在重構(gòu)控制器內(nèi)部的存儲(chǔ)器中,上電后,重構(gòu)控制器就可以按需求將不同設(shè)計(jì)方案分時(shí)定位到目標(biāo)可編程器件內(nèi),同時(shí)保持其他部分電路功能正常,實(shí)現(xiàn)在系統(tǒng)靈活配置,提高系統(tǒng)工作效率。

1 SVF格式配置文件

很多嵌入式系統(tǒng)中都用到了FPGA/CPLD等可編程器件,在這些系統(tǒng)中利用SVF格式配置文件就可以方便地通過(guò)微控制器對(duì)可編程器件進(jìn)行重新配置。目前可編程芯片廠商的配套軟件都可以生成可編程器件的SVF格式配置文件,串行矢量格式(SVF)是一種用于說(shuō)明高層IEEE 1149.1(JTAG)總線操作的語(yǔ)法規(guī)范。SVF由Texas Instruments開(kāi)發(fā),并已成為數(shù)據(jù)交換標(biāo)準(zhǔn)而被Teradyne,Tektronix等JTAG測(cè)試設(shè)備及軟件制造商采用。Xilinx的 FPGA以及配置PROM可通過(guò)JTAG接口中TAP控制器接收SVF格式的編程指令。由于SVF文件由ASCII語(yǔ)句構(gòu)成,它要求較大的存儲(chǔ)空間,并且存儲(chǔ)效率很低,無(wú)法勝任嵌入式應(yīng)用。為了在嵌入式系統(tǒng)中充分利用其有限的存儲(chǔ)空間,并不直接利用SVF文件對(duì)可編程器件進(jìn)行在系統(tǒng)編程,而是將SVF文件轉(zhuǎn)換成另一種存儲(chǔ)效率比較高的二進(jìn)制格式的文件,把它存儲(chǔ)在數(shù)據(jù)存儲(chǔ)器中。Xilinx公司提供用于創(chuàng)建器件編程文件的iMPACT工具,該工具隨附于標(biāo)準(zhǔn)Xilinx ISETM軟件內(nèi)。iMPACT軟件能自動(dòng)讀取標(biāo)準(zhǔn)的BIT/MCS器件編程文件,并將其轉(zhuǎn)換為緊湊的二進(jìn)制XSVF格式。

本設(shè)計(jì)是基于“ARM處理器+FPGA”結(jié)構(gòu)的重構(gòu)控制器,重構(gòu)控制器中的FPGA能夠根據(jù)ARM處理器傳送來(lái)的命令,對(duì)目標(biāo)可編程器件 JTAG接口進(jìn)行控制,并負(fù)責(zé)解譯XSVF格式的配置文件信息,生成xilinx器件所用的編程指令、數(shù)據(jù)和控制信號(hào)(TMS,TDI,TCK序列)向目標(biāo)可編程器件的JTAG TAP控制器提供所需的激勵(lì),從而執(zhí)行最初在XSVF文件內(nèi)指定的編程和(可選的)測(cè)試操作。使目標(biāo)可編程器件內(nèi)的TAP狀態(tài)機(jī)進(jìn)行狀態(tài)轉(zhuǎn)換,將指令和數(shù)據(jù)掃描到FPGA內(nèi)部邊界掃描電路指令寄存器和數(shù)據(jù)寄存器中。完成一次目標(biāo)可編程器件配置,實(shí)現(xiàn)用戶此時(shí)所要求功能,在下一時(shí)段,可根據(jù)用戶新的要求,調(diào)用重構(gòu)控制器內(nèi)部存儲(chǔ)器中不同方案在系統(tǒng)重新配置目標(biāo)可編程器件,這樣就實(shí)現(xiàn)了硬件復(fù)用,減少成本。

2邊界掃描(JTAG)原理

2.1 JTAG接口基本結(jié)構(gòu)

JTAG(Joint Test,Action Group,聯(lián)合測(cè)試行動(dòng)小組)是一種國(guó)際標(biāo)準(zhǔn)測(cè)試協(xié)議(IEEE 1149.1兼容),其工作原理是在器件內(nèi)部定義一個(gè)測(cè)試訪問(wèn)端口(TestAccess Port,TAP),通過(guò)專用的JTAG測(cè)試工具對(duì)內(nèi)部節(jié)點(diǎn)進(jìn)行測(cè)試和調(diào)試。TAP是一個(gè)通用的端口,外部控制器通過(guò)TAP可以訪問(wèn)芯片提供的所有數(shù)據(jù)寄存器和指令寄存器。現(xiàn)在JTAG接口還常用于芯片的在線配置(In-System Programmable,ISP),對(duì)PLD,F(xiàn)LASH等器件進(jìn)行配置。JTAG允許多個(gè)器件通過(guò)JTAG接口串聯(lián)在一起,形成一個(gè)JTAG鏈,實(shí)現(xiàn)對(duì)各個(gè)器件分別測(cè)試和在系統(tǒng)配置。

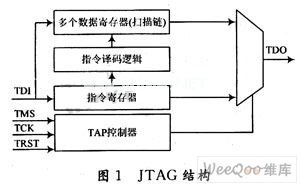

JTAG主要由三部分構(gòu)成:TAP控制器、指令寄存器和數(shù)據(jù)寄存器,如圖1所示。標(biāo)準(zhǔn)的JTAG接口有四組輸出線:TMS,TCK,TDI,TDO,以及1個(gè)可選信號(hào)TRST。

TCK:JTAG測(cè)試時(shí)鐘輸入,當(dāng)TCK保持在零狀態(tài)時(shí),測(cè)試邏輯狀態(tài)應(yīng)保持不變;

TMS:測(cè)試模式選擇,控制JTAG狀態(tài),如選擇寄存器、數(shù)據(jù)加載、測(cè)試結(jié)果輸出等,出現(xiàn)在TMS的信號(hào)在TCK的上升沿由測(cè)試邏輯采樣進(jìn)入TAP控制器;

TDI:測(cè)試數(shù)據(jù)輸入,測(cè)試數(shù)據(jù)在TCK的上升沿采樣進(jìn)入移位寄存器(SR);

TDO:測(cè)試數(shù)據(jù)輸出,測(cè)試結(jié)果在TCK的下降沿從移位寄存器(SR)移出,輸出數(shù)據(jù)與輸入到TDI的數(shù)據(jù)應(yīng)不出現(xiàn)倒置;

TRST:可選復(fù)位信號(hào),低電平有效。

Xilinx器件接受使用JTAG TAP的編程指令和測(cè)試指令。在IEEE 1149.1的標(biāo)準(zhǔn)中,用于CPLD,F(xiàn)PGA以及配置PROM的常見(jiàn)指令有:旁路(BYPASS)指令,通過(guò)用1 b長(zhǎng)的BYPASS寄存器將TDI與TDO直接連接,繞過(guò)(即旁路)邊界掃描鏈中的某個(gè)器件;EXTEST指令,將器件I/O引腳與內(nèi)部器件電路分離,以實(shí)現(xiàn)器件間的連接測(cè)試,它通過(guò)器件引腳應(yīng)用測(cè)試值并捕獲結(jié)果;IDCODE指令,返回用于定義部件類型、制造商和版本編號(hào)的32位硬件級(jí)別的識(shí)別碼; HIGHZ指令,使所有器件引腳懸置為高阻抗?fàn)顟B(tài);CFG_IN/CFG_OUT指令,允許訪問(wèn)配置和讀回所用的配置總線;JSTART,當(dāng)啟動(dòng)時(shí)鐘= JTAGCLK時(shí)為啟動(dòng)時(shí)序提供時(shí)鐘。

2.2 Tap狀態(tài)機(jī)時(shí)序介紹

JTAG邊界掃描測(cè)試由測(cè)試訪問(wèn)端口的TAP控制器管理。TMS,TRST和TCK引腳管理TAP控制器的操作,TDI和TDO位數(shù)據(jù)寄存器提供串行通道。TDI也為指令寄存器提供數(shù)據(jù),然后為數(shù)據(jù)寄存器產(chǎn)生控制邏輯。對(duì)于選擇寄存器、裝載數(shù)據(jù)、檢測(cè)和將結(jié)果移出的控制信號(hào),由測(cè)試時(shí)鐘 (TCK)和測(cè)試模式(TMS)選擇兩個(gè)信號(hào)控制。測(cè)試復(fù)位信號(hào)(TRST,一般以低電平有效)一般作為可選的第五個(gè)端口信號(hào)。

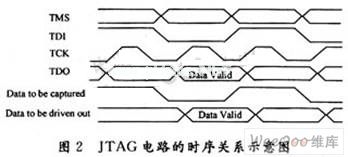

如圖2所示,所有基于JTAG的操作都必須同步于JTAG時(shí)鐘信號(hào)TCK。所有測(cè)試邏輯的變化(例如指令寄存器,數(shù)據(jù)寄存器等)必須出現(xiàn)在 TCK的上升沿或下降沿。關(guān)鍵時(shí)序關(guān)系是:TMS和TDI采樣于TCK的上升邊沿,一個(gè)新的TDO值將于TCK下降邊沿后出現(xiàn),因此一般情況下JTAG的時(shí)鐘不會(huì)太高。

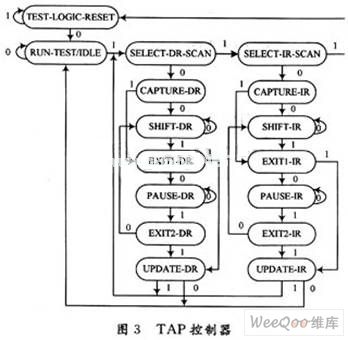

圖3表示了IEEE 1149.1標(biāo)準(zhǔn)定義的TAP控制器的狀態(tài)圖,TAP控制器是16個(gè)狀態(tài)的有限狀態(tài)機(jī),為JTAG接口提供控制邏輯。TAP狀態(tài)轉(zhuǎn)移如圖3所示,箭頭上的 1或0,表示TMS在TCK上升沿的值(高電平TMS=1,低電平TMS=0),同步時(shí)鐘TCK上升沿時(shí)刻TMS的狀態(tài)決定狀態(tài)轉(zhuǎn)移過(guò)程。對(duì)于TDI端輸入到器件的配置數(shù)據(jù)有兩個(gè)狀態(tài)變化路徑:一個(gè)用于移指令到指令寄存器中,另一個(gè)用于移數(shù)據(jù)到有效的數(shù)據(jù)寄存器,該寄存器的值由當(dāng)前執(zhí)行的JTAG指令決定。當(dāng)TAP控制器處于指令寄存器移位(SHIFT-IR)狀態(tài)時(shí),對(duì)于每一個(gè)TCK的上升沿,連接在TDI和TDO之間的指令寄存器組中的移位寄存器向串行輸出方向移一位。

當(dāng)TMS保持為高電平時(shí),在TCK的上升沿TAP控制器進(jìn)入到“EXIT1-IR”狀態(tài);當(dāng)TMS為低電平時(shí),TAP控制器保持在“指令寄存器移位”狀態(tài)。

當(dāng)TMS保持為高電平時(shí),在TCK的上升沿TAP控制器進(jìn)入到“EXIT1-IR”狀態(tài);當(dāng)TMS為低電平時(shí),TAP控制器保持在“指令寄存器移位”狀態(tài)。

3重構(gòu)控制器設(shè)計(jì)

3.1硬件系統(tǒng)組成

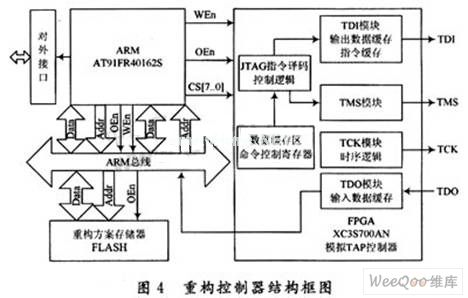

其主要功能是控制按照用戶不同需求控制調(diào)用不同的方案配置目標(biāo)可編程器件。它主要包括ARM處理器、FPGA、FLASH存儲(chǔ)器和對(duì)外總線接口,各功能部件主要功能如下:

(1)ARM處理器選用AT91FR40162S,其主要功能是控制模擬JTAG接口的FPGA讀取FLASH存儲(chǔ)器中的重構(gòu)方案,實(shí)現(xiàn)在系統(tǒng)配置;

(2)FPGA協(xié)處理器選用Xilinx公司SPARTEN3AN系列的XC3S700AN-FGG484,是基于非易失性存儲(chǔ)的FPGA,自身帶有PROM,它作為外部總線和ARM控制器之間的雙端口,主要功能是模擬JTAG接口實(shí)現(xiàn)TAP控制器時(shí)序,完成配置方案數(shù)據(jù)的并串轉(zhuǎn)換并輸出至外部總線;

(3)FLASH存儲(chǔ)器容量為32M×16 b,用于處理器的上電引導(dǎo)、存放多種重構(gòu)配置方案。由于要求的存儲(chǔ)容量較大,采用SPANSION公司S29GL512P(32M×16 b)的存儲(chǔ)空間,訪問(wèn)速度為110 ns,可以達(dá)到25 ns快速頁(yè)存取和相應(yīng)的90 ns隨機(jī)存取時(shí)間,F(xiàn)BGA封裝;

(4)外部總線接口,可采用1路RS 232驅(qū)動(dòng)接收器,實(shí)現(xiàn)和外部通信的接口;

(5)測(cè)試線TCK,TMS,TDI和TDO,是重構(gòu)控制器向目標(biāo)可編程器件提供所需的JTAG TAP激勵(lì),分別控制目標(biāo)多個(gè)FPGA的重構(gòu)配置和反饋重構(gòu)信息。

3.2重構(gòu)控制器工作原理

ARM執(zhí)行的初始化工作包括程序更新加載運(yùn)行,F(xiàn)PGA參數(shù)設(shè)定等;FPGA設(shè)定內(nèi)部寄存器和邏輯狀態(tài)的初始值、內(nèi)部緩沖區(qū)數(shù)據(jù)清零等。

重構(gòu)控制器示意圖如圖4所示。圖中ARM處理器一方面通過(guò)ARM總線讀取外部FLASH中的配置方案,對(duì)其進(jìn)行并串轉(zhuǎn)化操作,將其存儲(chǔ)到 FLASH存儲(chǔ)器中;另一方面重構(gòu)控制器中模擬TAP控制器的FPGA,從ARM內(nèi)置的FLASH存儲(chǔ)器中讀取配置文件,并執(zhí)行ARM處理器發(fā)出的指令解譯該文件,重構(gòu)控制器解釋二進(jìn)制文件方法如下:在ARM處理器的控制下,從裝載配置文件的FLASH中讀出一個(gè)字節(jié),判斷是哪條JTAG指令,然后根據(jù)指令的格式作具體的處理,產(chǎn)生TCK,TMS,TDI和TDO信號(hào),作為目標(biāo)可編程器件的JTAG接口激勵(lì),與目標(biāo)可編程器件的JTAG口串聯(lián)成菊花鏈,在 ARM處理器的控制下,對(duì)目標(biāo)可編程器件進(jìn)行在系統(tǒng)編程。被重構(gòu)的FPGA由支持局部動(dòng)態(tài)重構(gòu)的Xilinx公司的Virtex-4系列FPGA來(lái)實(shí)現(xiàn)。

4 結(jié) 語(yǔ)

本文介紹的重構(gòu)控制器既具有ARM微控制器所擁有的高速處理器核、體積小、集成度高、運(yùn)算速度快、存儲(chǔ)器容量大、功耗低等特點(diǎn),又具有FPGA 強(qiáng)大的并行計(jì)算能力和方便靈活的動(dòng)態(tài)可重構(gòu)性,使硬件信息(可編程器件的配置信息)像軟件程序一樣被動(dòng)態(tài)調(diào)用或修改。對(duì)于特定的目標(biāo)FPGA芯片,在一定控制邏輯的驅(qū)動(dòng)下,對(duì)芯片的全部或部分邏輯資源重新進(jìn)行動(dòng)態(tài)配置,從而實(shí)現(xiàn)硬件的時(shí)分復(fù)用,靈活快速地改變系統(tǒng)功能,節(jié)省邏輯資源,滿足大規(guī)模應(yīng)用需求。