引 言

數(shù)字相關(guān)器作為軟件無線電的典型應(yīng)用,在擴(kuò)頻通信中成為必不可少的技術(shù)。在傳統(tǒng)的擴(kuò)頻通信中,采用模擬器件(如:聲表面波器) 來實(shí)現(xiàn)解擴(kuò)單元,而用數(shù)字相關(guān)器可以增加系統(tǒng)的靈活性和穩(wěn)定性,因此,對數(shù)字相關(guān)器的研究具有較大的意義。本文采用DSP+FPGA 的結(jié)構(gòu),一方面使設(shè)計(jì)更加靈活,同時(shí)也降低了生產(chǎn)的代價(jià)。從通用性上考慮,本文采用零中頻的采樣系統(tǒng)。提出接收端如何正確地把信道中的模擬信號通過正確的零中頻采樣及數(shù)字相關(guān)器后恢復(fù)成數(shù)字信號。本文給出了數(shù)字相關(guān)的算法及仿真結(jié)果,用DSP+FPGA 實(shí)現(xiàn)的算法流程圖,最后給出了系統(tǒng)的實(shí)測結(jié)果。

解擴(kuò)算法簡介

發(fā)端的信號模型

對于數(shù)字信號,將其分別投影到I ,Q 兩路正交信號,其特征相同,因此這里僅對I 路信號進(jìn)行分析,同理可得出Q 路信號。

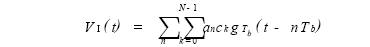

I 路基帶信息經(jīng)信道編碼后,速率為3.103 kb/s ,碼元間隔為323 μs , 然后進(jìn)行PN 碼擴(kuò)頻, PN 碼的長度為1 023 ,速率為3.174 Mcps ,因此,擴(kuò)頻后I 路基帶碼片的速上升為3.174 Mcps ,擴(kuò)頻增益為30 dB。信號可表示為:

其中an=±1 ,n ∈(0 ,∞) 為信息碼, ck 為擴(kuò)頻碼, gTb (t) 為矩形脈沖, Tb = 310 ns (此處未考慮脈沖成型,通常應(yīng)采用升余弦脈沖) 。

相關(guān)峰捕獲及同步判決算法分析及數(shù)學(xué)推導(dǎo)

在收端,先對收到的QPSK 信號進(jìn)行解調(diào),解調(diào)采用相干解調(diào)的方式,首先對模擬基帶波形采樣,對得到的數(shù)據(jù)流進(jìn)行滑動(dòng)相關(guān),得到一個(gè)相關(guān)值。由于PN 碼的固有特性,當(dāng)本地PN 碼與數(shù)據(jù)流中的相關(guān)碼對齊時(shí)(同步) ,便可得到很高的相關(guān)峰,而沒有對齊時(shí)(未同步) ,得到的相關(guān)值很小,這種特性一方面降低了系統(tǒng)誤判的可能性,另一方面也提高了系統(tǒng)的抗干擾性能。解調(diào)解擴(kuò)的相應(yīng)框圖如圖1 所示。

圖1 收端解擴(kuò)解調(diào)模型

假設(shè)信道是高斯白噪聲信道,只存在時(shí)延,高斯白噪聲,沒有多徑擴(kuò)展,則收到的信號r( t) 與發(fā)端的信號s( t)存在以下的關(guān)系:

此處,τ為信道傳播時(shí)延, n( t) 為信道噪聲。經(jīng)過本地載波相乘后,可得r′I ( t) 表達(dá)式如下:

由于本地載波是接收到的信號經(jīng)過鎖相環(huán)提取的,故信道時(shí)延帶來的載波時(shí)延也能被捕獲,故用cos ωc( t - τ)來表示本地載波。

r′I ( t) 經(jīng)過一低通濾波器, 得到r I ( t) , 為討論方便,假設(shè)低通濾波器能濾除二倍頻分量,同時(shí)通帶內(nèi)的相應(yīng)為常數(shù)2 。

由此可見,在理想情況下,可將發(fā)端I 路的信號得到恢復(fù),事實(shí)上已經(jīng)完成了解調(diào)任務(wù)。接下來就是AD 采樣,在這里把AD 采樣的速率設(shè)定為切普碼率的4 倍,相當(dāng)于在做相關(guān)時(shí),有4 路信號可供計(jì)算,這樣做的好處是每次優(yōu)選最好的一路,提高接收性能。事實(shí)上,采樣率越高對于性能的提高越有好處,但是不能無限度地提高,因?yàn)楹蠖说臄?shù)字器件有一個(gè)處理能力的限制。由于4 路采樣信號在數(shù)字解擴(kuò)模塊的處理是相互獨(dú)立的,所以這里只對一路采樣信號進(jìn)行研究。由于只對一路信號進(jìn)行研究,所以采樣率Ts 可等效為切普速率, 本系統(tǒng)中Ts =1/3.1M。

特點(diǎn),互相關(guān)值很小。由上式可見,第二項(xiàng)是影響誤判的主要因素,此處對于誤碼率的討論不同于一般意義的QPSK+擴(kuò)頻方式,因此將采用仿真的方式對誤碼率進(jìn)行討論。

利用計(jì)算機(jī)仿真,可得到高斯噪聲下的誤碼率曲線如圖2 所示。從仿真結(jié)果看,當(dāng)SNR ≥- 20 dB 時(shí),滿足語音通信(BER ≤10-3 ) 的要求;當(dāng)SNR ≥- 14 dB 時(shí),滿足數(shù)據(jù)通信(BER ≤10-6 ) 的要求。

圖2 高斯信道的誤碼性能

算法在DSP+FPGA 系統(tǒng)中的實(shí)現(xiàn)

由于數(shù)字相關(guān)模塊主要由FPGA 和DSP 來完成,因此主要的算法將嵌入進(jìn)這兩個(gè)芯片中。

DSP+FPGA 系統(tǒng)的最大優(yōu)點(diǎn)是結(jié)構(gòu)靈活,有較強(qiáng)的通用性,適合于模塊化設(shè)計(jì),從而能夠提高算法效率;同時(shí)其開發(fā)周期較短,系統(tǒng)容易維護(hù)和擴(kuò)展,適合實(shí)時(shí)信號處理。

實(shí)時(shí)信號處理系統(tǒng)中,低層的信號預(yù)處理的數(shù)據(jù)量大,對處理速度的要求高,但運(yùn)算結(jié)構(gòu)相對比較簡單,適用于FPGA 執(zhí)行硬件實(shí)現(xiàn),這樣能同時(shí)兼顧速度和靈活性。高層處理算法的特點(diǎn)是所處理的數(shù)據(jù)量較低層算法少,但算法的控制結(jié)構(gòu)復(fù)雜,適用于運(yùn)算速度高、尋址方式靈活、選用通信機(jī)制強(qiáng)大的DSP 芯片來實(shí)現(xiàn)。

DSP+FPGA 系統(tǒng)的核心由DSP 芯片和可重構(gòu)器件FPGA 組成。另外還包括一些外圍的輔助電路,如存儲器、先進(jìn)先出( FIFO) 器件及FLASH ROM 等。FPGA 電路與DSP 相連,利用DSP 處理器強(qiáng)大的I/O 功能實(shí)現(xiàn)系統(tǒng)內(nèi)部的通信。從DSP 角度看,F(xiàn)PGA 相當(dāng)于他的宏功能協(xié)處理器。外圍電路輔助核心電路進(jìn)行工作。DSP 和FPGA 各自帶有RAM ,用于存放處理過程所需要的數(shù)據(jù)及中間結(jié)果。FLASH ROM 中存儲了DSP 執(zhí)行程序和FPGA 的配置數(shù)據(jù)。先進(jìn)先出( FIFO) 器件則用于實(shí)現(xiàn)信號處理中常用到的一些操作,如延遲線、順序存儲等。

在本系統(tǒng)的設(shè)計(jì)中,DSP 采用TI 公司的C5409A ,同時(shí)采用SPANSION 公司的AM29LV200BT 作為DSP 的外掛FLASH ,存放相應(yīng)的程序; FPGA 采用的是Xilinx 公司的XCV600E ,同時(shí)采用Xilinx 公司的XC18V00 作為專用配置芯片,存放FPGA 程序;在FPGA 中將進(jìn)行FIFO 的設(shè)計(jì),DSP 通過對FIFO 的讀取來實(shí)現(xiàn)兩塊芯片間的通信。

總體的算法分為FPGA 和DSP 部分: FPGA 的算法主要包含的功能是,產(chǎn)生AD 采樣時(shí)鐘,接收AD 數(shù)據(jù),滑動(dòng)相關(guān),F(xiàn)IFO 構(gòu)成及DSP 中斷產(chǎn)生;DSP 含有:同步算法,判決算法。

以下是算法在各芯片中的嵌入分配示意圖,如圖3所示。

圖3 算法在各芯片中的嵌入示意圖

FPGA 和DSP 兩部分的算法必須協(xié)同運(yùn)行,他們之間的關(guān)系是:FPGA 的算法由時(shí)鐘來驅(qū)動(dòng),每個(gè)時(shí)鐘到來時(shí),他都要進(jìn)行相應(yīng)的數(shù)據(jù)接收,滑動(dòng)相關(guān),將相關(guān)值推入FIFO 的操作,當(dāng)他將FIFO 置到一定程度時(shí),則向DSP 發(fā)中斷信號;DSP 的程序在大部分時(shí)間處于一種循環(huán)等待的狀態(tài),而他一收到FPGA 的中斷,則進(jìn)行響應(yīng),先將FIFO 里面的若干數(shù)據(jù)讀出,然后進(jìn)行相應(yīng)的中斷處理,由DSP 完成同步處理,相關(guān)判決并實(shí)現(xiàn)基帶通信。總的流程圖如圖4 所示。

系統(tǒng)的運(yùn)行的實(shí)測性能

正常通信時(shí),誤碼率穩(wěn)定在1*10-5 。高斯噪聲干擾(未解擴(kuò)解調(diào)前加干擾) ,語音信號正常通信(誤碼率≤1×10-3 ) 的信干比:-17dB。在抗干擾方面,對于非瞄準(zhǔn)式單頻干擾語音信號的正常通信(誤碼率≤1×10-3 ) 的信干比:-14~-2dB(隨頻點(diǎn)有差異) ;而對于瞄準(zhǔn)式單頻干擾當(dāng)達(dá)到- 12 dB 時(shí),仍能繼續(xù)保持語音通信。

圖4 FPGA 及DSP 流程圖