基本框圖

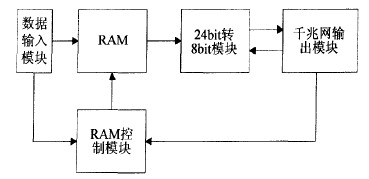

在現(xiàn)有LED顯示屏發(fā)送卡的基礎(chǔ)上,這里設(shè)計了一種無外接存儲體的LED顯示屏發(fā)送卡,,如圖1.

圖1 LED顯示屏發(fā)送卡原理圖

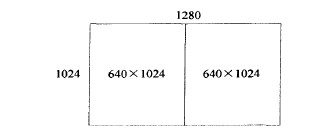

該發(fā)送卡由DVI模塊,、FPGA控制器、兩路千兆網(wǎng)輸出模塊構(gòu)成,。DVl解碼芯片將解碼得到的數(shù)據(jù)和控制信號傳給FPGA控制器,F(xiàn)PGA通過內(nèi)部的RAM 進行緩存,,并做了更換時鐘域和位寬變換的操作,,然后將處理后的數(shù)據(jù)通過千兆網(wǎng)輸出。對分辨率1280×1024,,刷新頻率為60Hz的實時視頻源,,這里采用垂直分區(qū)的方法,即將滿屏數(shù)據(jù)平均分成兩路千兆網(wǎng)輸出,,每一路千兆傳輸640X 1024,,如圖2所示。

圖2視頻數(shù)據(jù)分區(qū)圖

實現(xiàn)方法

由圖1的基本框圖看出,,該發(fā)送卡的設(shè)計除了搭建好硬件平臺外,,最重要的是FPGA控制器內(nèi)部程序的設(shè)計,。發(fā)送卡的FPGA控制器內(nèi)部原理框圖如圖3所示。

圖3 FPGA控制器的內(nèi)部原理框圖

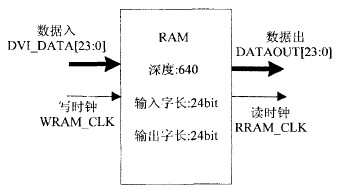

FPGA控制器的內(nèi)部邏輯包括數(shù)據(jù)輸入模塊,、雙口RAM 及其控制模塊,、24bit轉(zhuǎn)8bit模塊、千兆網(wǎng)輸出模塊,。數(shù)據(jù)輸入模塊將輸入的DVI信號(包括數(shù)據(jù),、時鐘、使能,、行場同步信號)分配給后端的RAM 和RAM 控制模塊,,并控制著整個系統(tǒng)的同步;RAM控制模塊控制RAM 的讀寫操作,,尤其是對開始寫,、寫停、開始讀,、讀停這4個狀態(tài)的控制:從RAM 輸出的數(shù)據(jù)經(jīng)過并串轉(zhuǎn)換后傳輸給千兆網(wǎng)輸出模塊,,千兆網(wǎng)輸出模塊則按照一定的網(wǎng)絡(luò)格式將接收到的數(shù)據(jù)進行打包輸出 。圖2提到的將數(shù)據(jù)分區(qū)發(fā)送,,該方法能夠?qū)M屏數(shù)據(jù)平均分成兩路千兆網(wǎng)輸出,。以下就以垂直分區(qū)的方法分析其數(shù)據(jù)流向、時鐘變化和傳輸時間差,。對于一路千兆網(wǎng)數(shù)據(jù)而言,,采用1個雙口RAM設(shè)計,RAM 的深度設(shè)置為640,,輸入和輸出字長均設(shè)置為24bit,,讀寫時鐘和使能分別獨立,如圖4所示,。

圖4一路千兆網(wǎng)數(shù)據(jù)傳輸?shù)碾p口RAM 配置

其中,,數(shù)據(jù)輸入和寫時鐘分別為DVI解碼芯片解碼后的24bit圖像數(shù)據(jù)DVI-DATA [23:0]和時鐘WRAM_CLK,讀RAM 的時鐘為千兆網(wǎng)時鐘RMll-CLK (125M) 三分頻后得到的時鐘RRAM-CLK(41.66MHz),,這樣,,后端再通過一個24bit轉(zhuǎn)8bit模塊即可將數(shù)據(jù)進行實時傳輸。

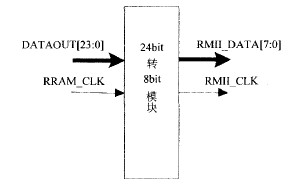

圖5 24bit轉(zhuǎn)8bit模塊

如圖5所示,,通過RRAM-CLK(41.66MHz)時鐘從RAM 中讀出一個像素的數(shù)據(jù),,然后再通過3個RMIl-CLK(125M)傳輸給千兆網(wǎng),即做了一個實時的并串轉(zhuǎn)化,。如此流水操作下去,,當從RAM 中讀完640個像素時,千兆網(wǎng)控制模塊將停止讀RAM操作,,等待下一行數(shù)據(jù)的到來,。當DVI解碼后的下一行數(shù)據(jù)一旦往RAM 中存儲的時候(至少已經(jīng)往其中存儲了1個像素),,千兆網(wǎng)控制模塊又開始從RAM 中讀取數(shù)據(jù),如此循環(huán),,直到第1024行數(shù)據(jù)的640個像素數(shù)據(jù)被傳輸完,。

在這里,實時傳輸具有如下特點:(1)往RAM中存數(shù)據(jù)和從RAM 中取數(shù)據(jù)同時進行,;(2)存RAM 的速度快,,讀RAM 的速度慢;(3)對寫RAM操作,,先把規(guī)定的數(shù)據(jù)存完,,用時為t ,然后進入等待階段 (t=t1-t2為行周期),;對讀RAM 操作,,把存好數(shù)通過 的時間傳輸出去,必須滿足t3

標準的分辨率1280 X 1024,刷新頻率為60Hz的行時鐘為64KHz,,周期為t=15.625微秒,;而從RAM 中讀完半行像素(640個)數(shù)據(jù)的時間是:t3=(1/41.66MHz)X640=15.36微秒。顯然,,在一個行周期里,,只往外傳出半行的數(shù)據(jù),傳輸時間差t-t3=265ns>0,,且該時間差滿足千兆網(wǎng)傳輸所必需數(shù)據(jù)包間隔,。由于寫RAM 的時鐘(108MHz)比讀RAM 的時鐘(41.66MHz)快得多,所以在寫RAM 的同時可以對RAM 進行讀操作(至少已經(jīng)往RAM 存儲了1個像素),,邊寫邊讀,,實現(xiàn)了視頻數(shù)據(jù)的實時傳輸。同理,,另外一路的千兆網(wǎng)設(shè)計與此相同,。