摘要:基于提高速度和減少面積的理念,對(duì)傳統(tǒng)的FIR數(shù)字濾波器進(jìn)行改良。考慮到FPGA的實(shí)現(xiàn)特點(diǎn),研究并設(shè)計(jì)了采用Radix-2的Booth算法乘法器以及結(jié)合了CSA加法器和樹型結(jié)構(gòu)的快速加法器,并成功應(yīng)用于FIR數(shù)字濾波器的設(shè)計(jì)中。濾波器的系數(shù)由Matlab設(shè)計(jì)產(chǎn)生。仿真和綜合結(jié)果表明,Booth算法乘法器和CSA算法加法器樹,在滿足FIR數(shù)字濾波器的性能要求的同時(shí),在電路實(shí)現(xiàn)面積上、尤其是速度上有明顯的優(yōu)化;并且當(dāng)數(shù)據(jù)量越多時(shí),優(yōu)化也越明顯。

關(guān)鍵詞:Matlab;Booth算法;CSA算法;ISE

研究數(shù)字濾波器的意義就在于它們正日益成為一種主要的DSP(DigitaI Signal Processing)運(yùn)算,并正在逐漸代替?zhèn)鹘y(tǒng)的模擬濾波器。它可以保證任意幅頻特性的同時(shí)具有嚴(yán)格的線性相頻特性。而現(xiàn)場可編程門陣列(Field Programmable Gate Array,F(xiàn)PGA)可并行執(zhí)行的特點(diǎn)決定它更加廣泛地應(yīng)用于實(shí)時(shí)數(shù)字信號(hào)處理領(lǐng)域。不能想象今天的生活如果沒有音頻;視頻和言語交際的樣子,而這些都要應(yīng)用數(shù)字信號(hào)處理技術(shù)。并且在任何時(shí)候,高性能,低規(guī)模,低成本都是設(shè)計(jì)的目標(biāo)。濾波器(Finite Impulse Response,F(xiàn)IR)的實(shí)現(xiàn)方法有很多種,最常見的有串行結(jié)構(gòu)和并行結(jié)構(gòu)方法。前者根據(jù)FIR濾波器的實(shí)現(xiàn)表達(dá)式,將濾波器實(shí)質(zhì)看作是做一個(gè)乘累加運(yùn)算。一次乘累加運(yùn)算的次數(shù)由濾波器的階數(shù)來決定。這種方法使用硬件資源相對(duì)較少,但速度較慢。并行結(jié)構(gòu)的方法,將濾波器的串行實(shí)現(xiàn)展開,就可以直接用多個(gè)乘法器和加法器并行實(shí)現(xiàn),其可以在一個(gè)時(shí)鐘周期內(nèi)完成一次濾波,但要占用大量的乘累加器,器件延遲比較大。目前為了滿足面積和速度的需要,人們通常采用Booth算法、CSD算法,分布式算法等技術(shù)對(duì)FIR設(shè)計(jì)進(jìn)行優(yōu)化,優(yōu)化效果各有利弊。本文針對(duì)串行結(jié)構(gòu)對(duì)乘累加運(yùn)算的乘和加分

別進(jìn)行優(yōu)化設(shè)計(jì)。分析了提高乘法器速度的途徑;針對(duì)多數(shù)據(jù)量的運(yùn)算,提出了一種新型的快速加法器的解決方案。體現(xiàn)了優(yōu)化設(shè)計(jì)中提高速度和減小面積的設(shè)計(jì)理念。同時(shí)給出并實(shí)現(xiàn)了一個(gè)16階FIR的設(shè)計(jì)實(shí)例。

1 用Matlab設(shè)計(jì)濾波器系數(shù)

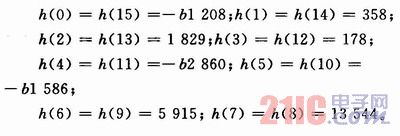

利用Matlab軟件的FDATool模塊,選擇濾波器類型為低通FIR,設(shè)計(jì)方法為窗口法,階數(shù)為16,窗口類型為Kaiser,數(shù)據(jù)采樣頻率fs為4.8 kHz,濾波器的截止頻率fc為1.08 kHz,導(dǎo)出的濾波器系數(shù)為16個(gè)15位的小數(shù)。將每一個(gè)系數(shù)擴(kuò)大相同的倍數(shù),最后四舍五人得到一系列整數(shù)系數(shù)。如下:

2 優(yōu)化FIR濾波器在FPGA中的實(shí)現(xiàn)結(jié)構(gòu)

2.1 FIR濾波器的基本算法原理

本文采用濾波器實(shí)現(xiàn)的基本的串行乘累加結(jié)構(gòu)。FIR濾波器的差分方程可表示為:

![]()

式中:t為濾波器的階數(shù)。

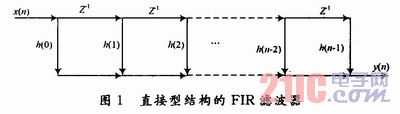

其直接運(yùn)算結(jié)構(gòu)如圖1所示。

從公式(1)中可知FIR濾波器在硬件上的設(shè)計(jì)主要是完成乘累加功能,實(shí)現(xiàn)的一種方法是直接相乘累加。在實(shí)際應(yīng)用中,當(dāng)濾波器設(shè)計(jì)對(duì)濾波速度要求不高時(shí),可采用串行結(jié)構(gòu)或改進(jìn)串行結(jié)構(gòu)來實(shí)現(xiàn),這樣可以選取資源較少的器件,降低設(shè)計(jì)成本;當(dāng)對(duì)濾波速度有較高要求時(shí),可以考慮采用并行或DA來實(shí)現(xiàn)。但要進(jìn)行FIR運(yùn)算,尤其在階數(shù)較高時(shí),幾乎無法在FPGA內(nèi)實(shí)現(xiàn)并行結(jié)構(gòu),所以這里采用串行運(yùn)算的結(jié)構(gòu),僅使用一個(gè)乘加器。所以本文的設(shè)計(jì)著重于提高串行結(jié)構(gòu)FIR的速度。下面將介紹一種高速的Booth算法乘法器和高速的加法器。

2.2 乘法器設(shè)計(jì)

乘法器是數(shù)字信號(hào)處理電路中最常用的單元,20年前就已經(jīng)研究的非常成熟。高性能乘法器是實(shí)現(xiàn)高性能的FIR運(yùn)算的關(guān)鍵,乘法器的運(yùn)算過程可以分解為部分積的產(chǎn)生和部分積的相加2個(gè)步驟。部分積的產(chǎn)生非常簡單,實(shí)現(xiàn)速度較快;而部分積相加的過程是多個(gè)二進(jìn)制數(shù)的相加,實(shí)現(xiàn)速度通常較慢。解決乘法器速度問題,需要減小部分積的個(gè)數(shù)、提高部分積相加運(yùn)算的速度。在乘法器設(shè)計(jì)上這里著重研究能夠減少部分積的Booth算法。

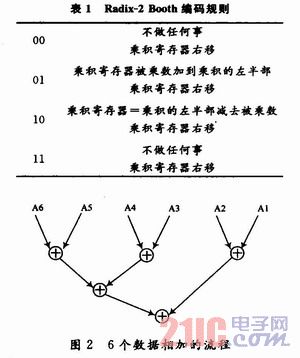

Booth算法乘法器可以減少乘法運(yùn)算部分積個(gè)數(shù),提高乘法運(yùn)算的速度。本文討論Radix-2的Booth算法,其基本算法思想是,一次看乘數(shù)的兩個(gè)位,依照當(dāng)前與前一位的不同,執(zhí)行不同的操作。總結(jié)出Radix-2 Booth算法的編碼規(guī)則如表1所示。

2.3 累加器設(shè)計(jì)

對(duì)于乘累加運(yùn)算的加法,傳統(tǒng)的算法將使多個(gè)乘法器的結(jié)果逐一累加,效率低、運(yùn)算時(shí)延大。本文提出了一種結(jié)合了CSA算法加法器和樹型結(jié)構(gòu)的新型加法器結(jié)構(gòu),對(duì)乘法器的結(jié)果一次性相加。

圖2為6個(gè)數(shù)相加的實(shí)例。如果不用其他加法器的話,6個(gè)數(shù)據(jù)的相加將耗去5個(gè)加法器,其關(guān)鍵路徑總共經(jīng)過三級(jí)的加法電路延遲,有必要對(duì)電路的面積和延遲進(jìn)行改進(jìn)。因此在多個(gè)數(shù)據(jù)相加的情況下,CSA(Carry Save Adder)加法器是很好的選擇。

CSA加法器仍然保留原有的全加器架構(gòu),一個(gè)n-bit的CSA器件如圖3所示。

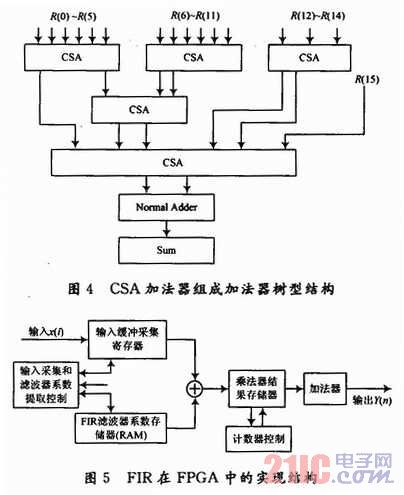

如果只有個(gè)數(shù)不多的數(shù)據(jù)相加時(shí),采用CSA器件不管是在電路面積和時(shí)序特性上都沒有優(yōu)勢(shì)。但當(dāng)多個(gè)數(shù)據(jù)相加時(shí),CSA加法器就能在電路面積和時(shí)序特性上體現(xiàn)出它的優(yōu)越性。樹型加法器結(jié)構(gòu)的關(guān)鍵特性在于利用不規(guī)則的樹形結(jié)構(gòu)對(duì)所有的準(zhǔn)備好輸入數(shù)據(jù)的運(yùn)算及時(shí)并行處理,大大節(jié)省了計(jì)算延時(shí),尤其是在多個(gè)數(shù)相加的情況下;缺點(diǎn)是其邏輯結(jié)構(gòu)形式不規(guī)整,在VLSI設(shè)計(jì)中對(duì)布局布線的影響較大。本文用CSA加法器為單元組成樹型結(jié)構(gòu),設(shè)計(jì)出一種如圖4所示的快速加法器結(jié)構(gòu)。由CSA加法器樹組成的樹型加法器中調(diào)用5個(gè)CSA加法器和一個(gè)普通加法器。R(0)~R(15)為前一級(jí)乘法器的16個(gè)輸出。在整個(gè)加法過程中,CSA加法器在電路實(shí)現(xiàn)上本身就具備快速、面積小的特點(diǎn),再加上樹型結(jié)構(gòu)的特點(diǎn),使整個(gè)加法器在實(shí)現(xiàn)速度上進(jìn)一步提升。同時(shí)整個(gè)加法過程能夠滿足最嚴(yán)格的時(shí)序要求,因?yàn)镃SA電路只在最后的時(shí)間內(nèi)執(zhí)行進(jìn)位加法,也就是由構(gòu)成樹的最后一級(jí)的Normal Adder(進(jìn)位加法器)執(zhí)行進(jìn)位加法。通常在大部分的應(yīng)用上會(huì)有一段足夠的時(shí)間允許執(zhí)行進(jìn)位加法的時(shí)間延遲。

2.4 FIR在FPGA中的實(shí)現(xiàn)結(jié)構(gòu)

本文設(shè)計(jì)的FIR在FPGA中的實(shí)現(xiàn)結(jié)構(gòu)如圖5所示,除了必須的乘法器和加法器外,還需要一個(gè)寬度為15、深度為16的濾波器系數(shù)存儲(chǔ)器(ROM)和一個(gè)寬度為30、深度為16的乘結(jié)果存儲(chǔ)器(RAM)。分別由相應(yīng)的計(jì)數(shù)器控制模塊控制,配合計(jì)數(shù)的值,執(zhí)行相應(yīng)的動(dòng)作。針對(duì)輸入的數(shù)據(jù)提取相應(yīng)的濾波器參數(shù),送入乘法器相乘,每得到一個(gè)結(jié)果送入下一級(jí)RAM中存儲(chǔ)起來,最后統(tǒng)一送入加法器,一次性執(zhí)行加運(yùn)算并輸出,最后得到濾波的結(jié)果。其中乘法器和加法器處理的都為符號(hào)數(shù)。

3 16階FIR的設(shè)計(jì)及仿真結(jié)果

設(shè)計(jì)一個(gè)16階的15位FIR濾波器。設(shè)計(jì)語言使用Verilog。設(shè)計(jì)工具使用Xilinx ISE平臺(tái)。FIR的輸入和系數(shù)都為15位有符號(hào)數(shù),乘法器的位數(shù)為30位,經(jīng)加法器后得到的濾波器輸出為38位有符號(hào)數(shù)。編寫testbench對(duì)設(shè)計(jì)進(jìn)行邏輯仿真,隨機(jī)選取16個(gè)輸入數(shù)據(jù)。配合前面有量化后的濾波器系數(shù),即可進(jìn)行行為級(jí)仿真。圖6中,rst為復(fù)位信號(hào),clk為系統(tǒng)時(shí)鐘信號(hào),din為輸入數(shù)據(jù),coe為濾波器系數(shù),dout為輸出信號(hào),control為輸出同步信號(hào)。由仿真結(jié)果看出最終濾波器的輸出結(jié)果和預(yù)期的結(jié)果相一致。同時(shí)利用ISE自帶的綜合器SXT進(jìn)行綜合,器件選用Xilinx公司的3s400pq208—4。綜合報(bào)告顯示,濾波器最大的頻率可達(dá)到143.328 MHz,達(dá)到高速目的。報(bào)告顯現(xiàn)資源的使用相對(duì)較大,沒有預(yù)期的理想。從RTL電路分析出在CSA構(gòu)成的加法器樹部分在面積上的優(yōu)化還不夠明顯,這個(gè)問題將在以后的研究中進(jìn)一步解決。

4 結(jié)語

本文以FIR在FPGA中的實(shí)現(xiàn)結(jié)構(gòu)為基礎(chǔ),研究了提高乘法器性能的途徑,并實(shí)現(xiàn)了Booth算法的乘法器,此算法保證高速的前提下,縮小了硬件規(guī)模,使得該乘法器的設(shè)計(jì)適合工程應(yīng)用及科學(xué)計(jì)算,在加法器實(shí)現(xiàn)上提出了一種結(jié)合了CSA加法器和樹型結(jié)構(gòu)的新型實(shí)現(xiàn)結(jié)構(gòu)。利用以上兩部分,成功設(shè)計(jì)了一個(gè)16階FIR濾波器,并且達(dá)到了高速的目的,但在實(shí)現(xiàn)面積上還有待優(yōu)化。