P89C669是PHILIPS半導體一款51MX(存儲器擴展)內(nèi)核的微處理器,,其指令執(zhí)行速度2倍于標準的80C51器件,線性地址經(jīng)擴展后可支持高達8 MB的程序存儲器和8 MB的數(shù)據(jù)存儲器,,這是他相對于標準51內(nèi)核的最大優(yōu)點,。目前的單片系統(tǒng)越來越復雜,,擴展的外部設備也更多,如果能充分利用P89C669的豐富的線性地址資源,,將能大大增強系統(tǒng)能力,。在一個嵌入式系統(tǒng)開發(fā)中,筆者采用ALTERA公司的CPLD芯片EPM7032利用這款單片機的線性地址擴展了豐富的外部設備資源,。

1 P89C669的存儲器結構

1.1 存儲結構

-

P89C669的存儲器結構為哈佛結構,,地址分配如表1所示。

從表1可見,,P89C669對傳統(tǒng)的51內(nèi)核的3部分存儲結構進行了相應的擴展,,各個部分的片內(nèi)存儲空間也增加了,如內(nèi)部數(shù)據(jù)空間有1 280 B在片內(nèi),,外部數(shù)據(jù)空間有768 B在片內(nèi),,有96 kB的片內(nèi)程序存儲空間等。

尋址指令除了傳統(tǒng)的MOV,,MOVX,,MOVC外,EMOV指令與24位的通用指針寄存器EPTR可尋址16MB的全部空間,,但是所占用的指令周期也較長,。

擴展外部數(shù)據(jù)存儲空問HDATA除了768 B在片內(nèi)外,其余地址空間可以用來擴展外部設備(其實只要把片內(nèi)的768 B通過指令將其屏蔽,,也可以用來擴展外部設備),。

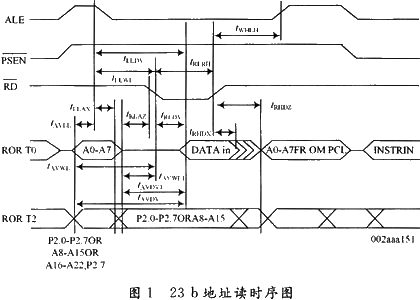

1.2 P2口的讀寫時序分析

尋址8 MB的數(shù)據(jù)存儲空間,需要有23 b的地址尋址能力,,P89C669將傳統(tǒng)51內(nèi)核的P2高位地址時分復用,,從而得到23 b地址尋址能力,時序圖如圖1所示,,即當使用23 b地址時,,ALE為高時,地址位A16~A22輸出到P2.0~P2.6,;ALE為低時,,地址位A8~A14輸出到P2.0~P2.6。無論ALE為何值,,位地址A15都從P2.7輸出,。

2 系統(tǒng)外部設備擴展需求

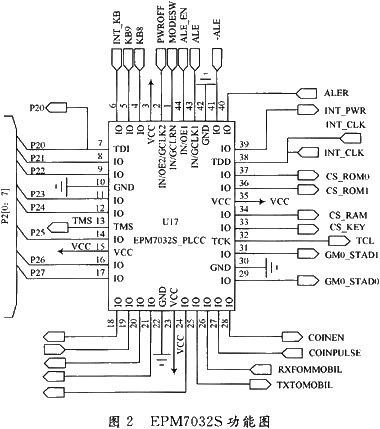

在某產(chǎn)品的控制系統(tǒng)中,擴展的外部設備比較豐富,,利用P89c669的23 b地址尋址能力進行設備地址編碼,,所以需要對23 b地址的時序邏輯進行處理,處理單元交給一塊ALTERA公司的CPLD(EPM7032),。

EPM7032具有32個邏輯單元,,約600個門級單元,,可用IO口36個,內(nèi)置IEEE std.1149.1 JTAG,,方便可編程下載,。

在滿足系統(tǒng)資源的前提下,選用EPM7032,,將P89C669的P2口作為處理單元輸入信號,,經(jīng)過CPLD的內(nèi)部邏輯進行譯碼或數(shù)據(jù)鎖存,以獲得各個外部設備資源的選擇信號及少量的控制信號,,如圖2所示,。

在本設計中,共需要得到設備選擇信號如SRAM芯片M68AF127B的片選CS_RAM,,2個FLASH ROM芯片SST29SF040的片選CS_ROM0,,CS_ROM1,模擬多路選擇器SN74LV4052的使能信號線CS_4052,,另外還有一些控制信號線,,這里就不一一介紹。

實際上,,P2口引入CPLD,,就P89C669的23 b地址線而言,用來地址譯碼和少量的控制信號等主要是利用最高的幾位,,在本設計中,,由于SST29SF040用到地址線A0~A18,所以CPLD的地址譯碼處理只能是利用剩下的A19~A22,,這將在下文的CPLD的譯碼單元可以看到,。

A0~A7低地址采用74HC573進行鎖存,A16~A18地址內(nèi)容采用74HC574進行鎖存,,如圖3所示,。

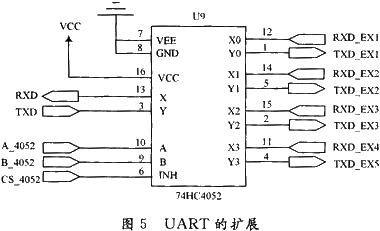

M68AF127B,SST29SF040,,74HCA052的功能連接圖如圖4所示,,74HC4052用于UART口的擴展,如圖5所示,。

3 EPM7032S的邏輯設計

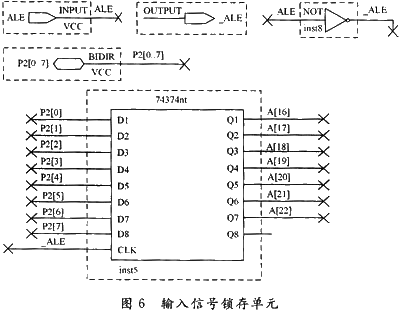

CPLD的設計采用原理圖的方法進行設計,,簡便快捷,,如圖6所示,,采用74374模塊鎖存P2口的輸入信號,ALE反向后得到_ALE作為74374的鎖存時鐘線輸入,。

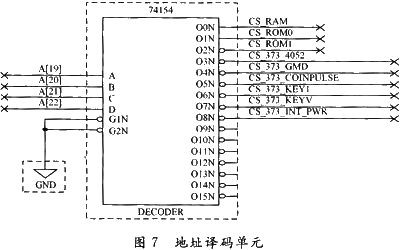

對高位的地址線A19~A22進行地址譯碼,,獲得各芯片的片選線,,如圖7所示。

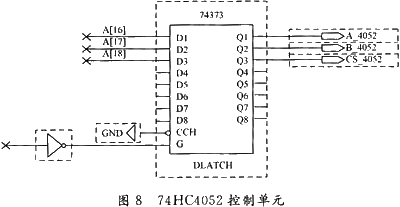

如果不是對SST29SF040進行讀寫,,則高位地址線A16~A18仍然可以利用,,這里將其作為74HC4052的3個輸入控制線A,B,,INH,,即圖8中的A_4052,B_4052,,CS_4052,。

4 KeilC51平臺的外部設備測試

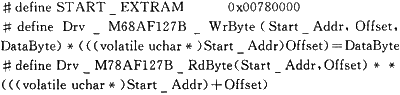

編寫設備驅動程序是在KeilC51的平臺上,由于利用了P89C669的23 b地址線,,在C51的平臺上采用指針讀寫設備很方便,,這里給出讀寫SRAM芯片M68AF127B的C源代碼例子,以供參考,。

以上3句為測試SRAM的測試代碼,,START_EX-TRAM為SRAM芯片的起始地址(可根據(jù)CPLD的內(nèi)部設計進行相應的修改),第2,,3句分別是寫,、讀數(shù)據(jù)的宏。

5 結 語

利用P89C669的23 b的線性地址并采用CPLD擴展外部設備資源可以說是不錯的一個方法,,對外部設備的訪問將顯得更加簡便,,當然,在成本方面系統(tǒng)設計工程師也要加以考慮,,并最終尋找一個性價比最高的方案,。