關(guān)鍵字:FPGA" title="FPGA">FPGA 8PSK" title="8PSK">8PSK 軟解調(diào)" title="軟解調(diào)">軟解調(diào)

0 引言

隨著衛(wèi)星通信服務(wù)業(yè)的發(fā)展,人們對(duì)服務(wù)質(zhì)量的要求越來越高。2003 年,衛(wèi)星數(shù)字視頻廣播(DVB-S2)系統(tǒng)采用了高效的低密度奇偶校驗(yàn)碼(LDPC),提高了大約30%的帶寬效率。眾所周知,衛(wèi)星通信系統(tǒng)中常用LDPC 與BCH 級(jí)聯(lián)的前向糾錯(cuò)編碼來獲得較高的性能,為了達(dá)到這種性能要求,接收信號(hào)在解調(diào)部分需要使用軟解調(diào),因此在高階調(diào)制系統(tǒng)(例如8PSK)中,需要一種合適的,簡(jiǎn)單易實(shí)現(xiàn)的軟解調(diào)技術(shù)來對(duì)接收信號(hào)進(jìn)行解映射。在傳統(tǒng)的無線通信系統(tǒng)設(shè)計(jì)中,對(duì)數(shù)似然比(LLR)算法作為性能最優(yōu)算法常被用于軟判決技術(shù)中,然而由于該算法的復(fù)雜度過高,涉及到多次對(duì)數(shù)與指數(shù)運(yùn)算,不適合于硬件實(shí)現(xiàn),因此,很多簡(jiǎn)化軟判算法相繼出現(xiàn)。其中最大值(MAX)算法在LLR 算法的基礎(chǔ)上簡(jiǎn)化了指數(shù)和對(duì)數(shù)運(yùn)算,其硬件實(shí)現(xiàn)復(fù)雜度與LLR 相比大大降低,同時(shí)相比LLR 算法性能損失較小。因此,在通信系統(tǒng)硬件設(shè)計(jì)中,通常選用MAX 算法作為一種合適的軟解調(diào)算法對(duì)接收信號(hào)進(jìn)行軟解調(diào)。

這里首先分析了8PSK 軟解調(diào)算法的復(fù)雜度以及MAX算法的基本原理,并在Altera 公司的Stratix II 系列FPGA芯片上實(shí)現(xiàn)了此軟解調(diào)硬件模塊,同時(shí)與LDPC 譯碼模塊進(jìn)行了聯(lián)合驗(yàn)證。通過軟硬件驗(yàn)證和分析表明,此設(shè)計(jì)在運(yùn)算復(fù)雜度、吞吐量、最終誤碼性能上取得很好的折中。

1 8PSK 軟解調(diào)原理

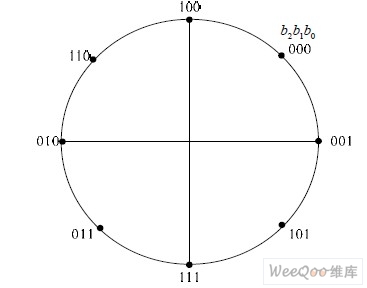

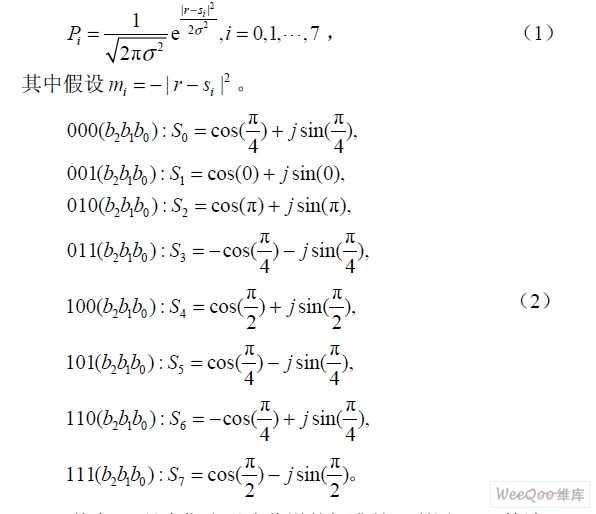

8PSK 的調(diào)制星座圖如圖1 所示,每個(gè)符號(hào)代表三個(gè)比特, 式(1)表示經(jīng)過高斯白噪聲信道后接收信號(hào)的概率密度函數(shù),式(2)描述了星座圖上每個(gè)星座點(diǎn)的值,Si 代表該星座圖上1 到8 個(gè)星座點(diǎn)。

圖1 8PSK 調(diào)制星座

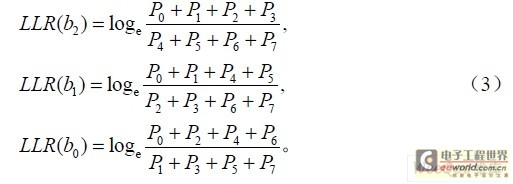

其中σ 是高斯白噪聲信道的標(biāo)準(zhǔn)差。利用LLR 算法,軟判決如式(3)所示,其中分子上的各項(xiàng)表示此比特為0的概率之和,分母各項(xiàng)表示此比特為1 的概率之和。

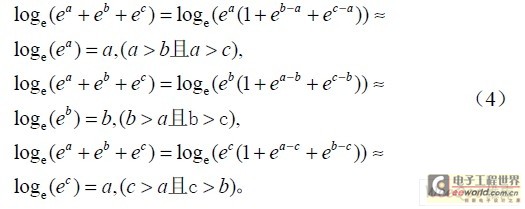

從式(2)和式(3)可以看出,每計(jì)算一比特的LLR,都需要平方、指數(shù)和對(duì)數(shù)運(yùn)算,因此LLR 算法具有較高的運(yùn)算復(fù)雜度和較大的資源開銷,尤其是硬件實(shí)現(xiàn)指數(shù)、對(duì)數(shù)復(fù)雜度高,所以LLR 算法不適合FPGA 實(shí)現(xiàn)。而最大值(MAX)算法能有效避免計(jì)算每比特對(duì)數(shù)似然值的指數(shù)和對(duì)數(shù)運(yùn)算,其原理如式(4)所示。

由式(3)和式(4)可知,簡(jiǎn)化以后的MAX 算法如下式(5)所示,對(duì)于式(3)和式(5)可知,LLR 算法在硬件上很難實(shí)現(xiàn)指數(shù)和對(duì)數(shù)運(yùn)算,而MAX 算法只需要簡(jiǎn)單的加減運(yùn)算和少數(shù)乘法運(yùn)算,易于工程硬件實(shí)現(xiàn),因此選取MAX 算法作為硬件實(shí)現(xiàn)的最終方案。

2 算法性能分析

通過MATLAB 仿真平臺(tái),做了如下性能仿真對(duì)比分析。

由MATLAB 產(chǎn)生一組隨機(jī)序列,長(zhǎng)度為10 萬個(gè)編碼塊,每個(gè)編碼塊為4 032 bit,再經(jīng)過碼率為1/2 的LDPC 編碼模塊,通過對(duì)應(yīng)的8PSK 調(diào)制,在Eb/N0 為4 dB 到7 dB 的區(qū)間內(nèi),分別經(jīng)過LLR 最優(yōu)算法、浮點(diǎn)MAX 算法、定點(diǎn)MAX 算法算出對(duì)數(shù)似然比,最后分別經(jīng)過LDPC 譯碼模塊,得出誤碼性能。

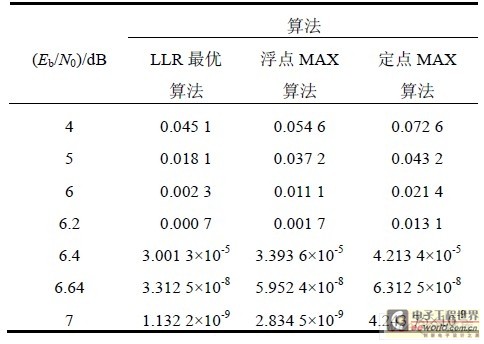

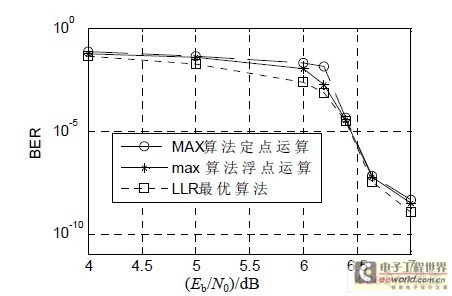

表1 是通過MATLAB 仿真平臺(tái)計(jì)算出來的每個(gè)Eb/N0所對(duì)應(yīng)的誤碼率,圖2 是與之相對(duì)應(yīng)的誤碼率曲線圖。由圖2 可知,對(duì)于Eb/N0 測(cè)試區(qū)間為4 dB 到7 dB 的任意一個(gè)測(cè)試點(diǎn),LLR 最優(yōu)算法的誤碼率總比定點(diǎn)MAX 算法和浮點(diǎn)MAX 算法要小,其中浮點(diǎn)MAX 算法誤碼性能居中,定點(diǎn)MAX 算法最差。MAX 算法是通過降低誤碼性能來換取運(yùn)算復(fù)雜度的降低,其誤碼性能要比LLR 最優(yōu)算法差。與浮點(diǎn)MAX 算法相比,定點(diǎn)MAX 算法對(duì)輸入軟解調(diào)模塊的I、Q兩路信號(hào)和輸出的似然比分別進(jìn)行了截位和限幅,如圖2 所示,定點(diǎn)MAX 算法相對(duì)于浮點(diǎn)MAX 算法損失了一定的誤碼性能。由表可知,定點(diǎn)MAX 算法在Eb/N0 為6.64 dB 時(shí),其誤碼率為6.5125×10-8,驗(yàn)證了該定點(diǎn)方案能夠滿足系統(tǒng)設(shè)計(jì)要求。

表 1 MATLAB 誤碼率仿真表

圖2 MATLAB 誤碼率仿真

3 MAX 算法硬件實(shí)現(xiàn)

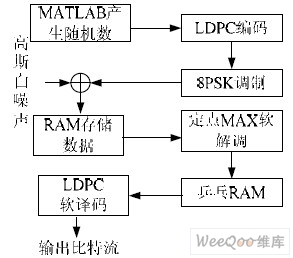

由于硬件實(shí)現(xiàn)都是定點(diǎn)運(yùn)算,所以MAX 算法的實(shí)現(xiàn)是針對(duì)定點(diǎn)的MAX 算法進(jìn)行硬件設(shè)計(jì)的。硬件仿真流圖如圖3 所示,首先利用MATLAB 產(chǎn)生隨機(jī)序列,假設(shè)每一編碼塊為4032 bit,LDPC 編碼效率為1/2 碼率,則經(jīng)過LDPC 編碼后,每一編碼塊為8 064 bit,經(jīng)8PSK 調(diào)制成符號(hào)后,每一個(gè)編碼塊被調(diào)制成2 688 個(gè)符號(hào),實(shí)部虛部分為I、Q 兩路,再疊加信噪比為SNR 的高斯白噪聲,最后把數(shù)據(jù)文件存儲(chǔ)在RAM 中。在硬件實(shí)現(xiàn)上,定點(diǎn)MAX 軟解調(diào)模塊以一定速率從RAM 讀取數(shù)據(jù)并進(jìn)行軟解調(diào),軟解調(diào)輸出的對(duì)數(shù)似然比存儲(chǔ)在乒乓RAM 中,每存滿一個(gè)編碼塊就向LDPC 譯碼器發(fā)出一個(gè)讀有效信號(hào),LDPC 譯碼器在接收到該有效信號(hào)的下一個(gè)時(shí)鐘周期就開始以一定速率讀取整個(gè)編碼塊的對(duì)數(shù)似然值,接著開始進(jìn)行LDPC 譯碼,最后以一定速率輸出最終的譯碼結(jié)果。

圖3 硬件設(shè)計(jì)仿真

4 硬件設(shè)計(jì)結(jié)果分析

驗(yàn)證一個(gè)軟解調(diào)模塊性能的好壞,需要級(jí)聯(lián)譯碼模塊進(jìn)行仿真綜合驗(yàn)證。在硬件設(shè)計(jì)中,通過在Stratix II FPGA 硬件平臺(tái)上級(jí)聯(lián)MAX 定點(diǎn)算法模塊與LDPC 譯碼算法模塊,然后進(jìn)行綜合布線,最后下載到硬件平臺(tái)進(jìn)行測(cè)試。

將仿真通過的工程文件使用Chipscope 添加觀察采樣信號(hào),觸發(fā)信號(hào)和待觀察信號(hào)后重新綜合、布局布線生成bit文件,下載到目標(biāo)板后用Chipscope 進(jìn)行在線測(cè)試,通過將輸出結(jié)果與輸入比特流進(jìn)行比較,驗(yàn)證設(shè)計(jì)正確性。分析QUARTUS II 綜合報(bào)告,該設(shè)計(jì)模塊只需加減法器,部分寄存器和16 個(gè)乘法模塊,使用資源較少,能滿足低復(fù)雜度、高吞吐量的設(shè)計(jì)要求。

5 結(jié)語

由于LLR 算法具有較高的運(yùn)算復(fù)雜度,不易于硬件實(shí)現(xiàn),而經(jīng)過簡(jiǎn)化的MAX 算法由于避免了指數(shù)和對(duì)數(shù)運(yùn)算,大大降低運(yùn)算復(fù)雜度,只需進(jìn)行加減法和少數(shù)乘法運(yùn)算,適合于硬件實(shí)現(xiàn)。該設(shè)計(jì)通過MATLAB 與VHDL 仿真對(duì)照,驗(yàn)證了MAX 軟解調(diào)算法硬件設(shè)計(jì)的準(zhǔn)確性,同時(shí)將該模塊與LDPC 譯碼模塊級(jí)聯(lián),在具體的FPGA 芯片上運(yùn)行,利用片上分析儀Chipscope 進(jìn)一步驗(yàn)證設(shè)計(jì)的可行性。