摘要:為進(jìn)行高精度信號(hào)源的設(shè)計(jì),同時(shí)降低設(shè)計(jì)成本,以Cyclone II系列低端FPGA為核心,利用直接頻率合成技術(shù),對(duì)正弦信號(hào)等數(shù)據(jù)進(jìn)行1/4周期壓縮存儲(chǔ)到ROM中,在外部時(shí)鐘頻率為50 MHz,實(shí)現(xiàn)了正弦信號(hào)源的設(shè)計(jì),同時(shí),實(shí)現(xiàn)三角波、鋸齒波、矩形脈沖及2-ASK、2-PSK和2-FSK等數(shù)字調(diào)制信號(hào),系統(tǒng)還具有掃頻、指定波形次數(shù)等功能。仿真結(jié)果表明,信號(hào)源精度高,頻率調(diào)整步進(jìn)可達(dá)0.034 92 Hz,頻率范圍為0.034 92 Hz~9.375 MHz,制作成本低,功能豐富。

0 引言

近年來電子信息技術(shù)飛速發(fā)展,使得各領(lǐng)域?qū)π盘?hào)源的要求不斷提高,不但要求其頻率穩(wěn)定度和準(zhǔn)確度高,頻率改變方便,而且還要求可以產(chǎn)生任意波形,輸出不同幅度的信號(hào)等。DDFS技術(shù)是自上世紀(jì)70年代出現(xiàn)的一種新型的直接頻率合成技術(shù)。DDFS技術(shù)是在信號(hào)的采樣定理的基礎(chǔ)上提出來的,從“相位”的概念出發(fā),進(jìn)行頻率合成,不但可利用晶體振蕩的高頻率穩(wěn)定度、高準(zhǔn)確度,且頻率改變方便,轉(zhuǎn)換速度快,便于產(chǎn)生任意波形等,因此,DDFS技術(shù)是目前高精密度信號(hào)源的核心技術(shù)。

1 DDFS技術(shù)原理及相關(guān)參數(shù)計(jì)算

DDFS技術(shù)的原理:將對(duì)正弦信號(hào)(或其他信號(hào))的采樣量化數(shù)據(jù)存入ROM存儲(chǔ)器中,在時(shí)鐘的控制下,依次或隔一定步進(jìn)讀取ROM中的數(shù)據(jù),再通過D/A轉(zhuǎn)換芯片轉(zhuǎn)換成模擬信號(hào),進(jìn)一步經(jīng)后級(jí)的低通濾波器、功率放大電路等來實(shí)現(xiàn)頻率合成。其主要的組成部分包括相位累加器、數(shù)據(jù)存儲(chǔ)ROM表、D/A轉(zhuǎn)換、低通濾波器及功率放大電路等。

根據(jù)DDFS原理,DDFS主要參數(shù)包括正弦信號(hào)的采樣點(diǎn)數(shù)N,最高輸出頻率fomax,最低輸出頻率fomin及頻率分辨率△fo等。本設(shè)計(jì)要產(chǎn)生1 Hz~10 MHz范圍內(nèi),步進(jìn)為1 Hz的正弦信號(hào),參數(shù)計(jì)算如下:

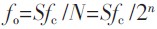

1)輸出頻率通式fo  ,N為采樣點(diǎn)個(gè)數(shù),S為步進(jìn)長(zhǎng)度。

,N為采樣點(diǎn)個(gè)數(shù),S為步進(jìn)長(zhǎng)度。

2)輸出最高頻率fomax  ;根據(jù)奈奎斯特采樣定理,1個(gè)周期至少采樣兩個(gè)點(diǎn)才能保證原信號(hào)的頻率信息。而實(shí)現(xiàn)工程應(yīng)用中一個(gè)周期至少采樣16個(gè)點(diǎn)或更多點(diǎn),以保證輸出信號(hào)的質(zhì)量。輸出最高頻率要達(dá)10 MHz,所需的系統(tǒng)時(shí)鐘信號(hào)頻率fc為160 MHz。由于本文使用的外接晶振為50 MHz,則必須使用CycloneII系列FPGA自帶的數(shù)字鎖相環(huán)(PLL)對(duì)輸入時(shí)鐘進(jìn)行倍頻,以達(dá)到所需的時(shí)鐘頻率160 MHz。可取3倍頻到150 MHz。此時(shí)系統(tǒng)輸出的最高頻率為:fomax=150 MHz/16=9.375 MHz。雖然通過提高鎖相環(huán)的倍頻數(shù),可進(jìn)一步提高工作頻率,從而可以產(chǎn)生更高的輸出信號(hào)頻率,但由于在進(jìn)行DDFS模塊設(shè)計(jì)時(shí),其所能工作的最高頻率將制約著倍頻數(shù)。

;根據(jù)奈奎斯特采樣定理,1個(gè)周期至少采樣兩個(gè)點(diǎn)才能保證原信號(hào)的頻率信息。而實(shí)現(xiàn)工程應(yīng)用中一個(gè)周期至少采樣16個(gè)點(diǎn)或更多點(diǎn),以保證輸出信號(hào)的質(zhì)量。輸出最高頻率要達(dá)10 MHz,所需的系統(tǒng)時(shí)鐘信號(hào)頻率fc為160 MHz。由于本文使用的外接晶振為50 MHz,則必須使用CycloneII系列FPGA自帶的數(shù)字鎖相環(huán)(PLL)對(duì)輸入時(shí)鐘進(jìn)行倍頻,以達(dá)到所需的時(shí)鐘頻率160 MHz。可取3倍頻到150 MHz。此時(shí)系統(tǒng)輸出的最高頻率為:fomax=150 MHz/16=9.375 MHz。雖然通過提高鎖相環(huán)的倍頻數(shù),可進(jìn)一步提高工作頻率,從而可以產(chǎn)生更高的輸出信號(hào)頻率,但由于在進(jìn)行DDFS模塊設(shè)計(jì)時(shí),其所能工作的最高頻率將制約著倍頻數(shù)。

3)輸出最低頻率fomin  要做到fc/N=1 Hz,則N=2n=150M,n=log2(150 M)=[27.16]=28。即ROM中的采樣數(shù)據(jù)為150M點(diǎn),對(duì)應(yīng)的尋址ROM的地址位數(shù)據(jù)長(zhǎng)度為28位。

要做到fc/N=1 Hz,則N=2n=150M,n=log2(150 M)=[27.16]=28。即ROM中的采樣數(shù)據(jù)為150M點(diǎn),對(duì)應(yīng)的尋址ROM的地址位數(shù)據(jù)長(zhǎng)度為28位。

4)頻率分辨率△fo △fo=fc/2n,已知ROM的地址位至少為28位,本設(shè)計(jì)中取32位,這樣所得的fomin及△fo為150M/232=0.03492 Hz。

5)ROM數(shù)據(jù)1/4周期壓縮 ROM的尋址地址位長(zhǎng)度為32位,即所需的ROM單元數(shù)將為232個(gè)。但ROM中并不需要存儲(chǔ)這么多數(shù)據(jù)點(diǎn),因?yàn)閿?shù)據(jù)重復(fù)量非常大,只需存入一定量的點(diǎn)即可。本設(shè)計(jì)中,根據(jù)正弦信號(hào)周期內(nèi)的數(shù)據(jù)特點(diǎn),對(duì)周期正弦信號(hào)的(0,π/2)區(qū)間進(jìn)行1 024點(diǎn)的采樣,進(jìn)行12位的量化并存入ROM。這相當(dāng)于對(duì)(0,2π)區(qū)間進(jìn)行了4 096個(gè)點(diǎn)的采樣,ROM數(shù)據(jù)量壓縮為1/4。此時(shí),相位累加器輸出地址位相應(yīng)修改為30位。這樣以來,在進(jìn)行數(shù)據(jù)輸出時(shí),對(duì)(π,2π)區(qū)間的數(shù)據(jù)要做取補(bǔ)的運(yùn)算。因?yàn)樵谶@個(gè)區(qū)間上正弦信號(hào)數(shù)據(jù)為負(fù)值。

6)ROM地址位長(zhǎng)度 通過數(shù)據(jù)壓縮,ROM的地址只需10位,此時(shí),只需要對(duì)相位累加器的30位地址位輸出值,取高10位用于ROM尋址即可。

7)步進(jìn)位長(zhǎng)度 步進(jìn)最大應(yīng)為232/24=228,即為28位的二進(jìn)制數(shù)。

2 DDFS的FPGA實(shí)現(xiàn)

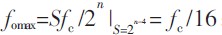

本設(shè)計(jì)中DDFS模塊的設(shè)計(jì)原理圖如圖1所示。主要包括地址發(fā)生單元(相位累加器)、ROM存儲(chǔ)單元、補(bǔ)碼轉(zhuǎn)換電路及一些數(shù)據(jù)延時(shí)單元組成。工作每一個(gè)部分均采用VHDL語言進(jìn)行描述并生成模塊以便在頂層文件中進(jìn)行調(diào)用。

圖1 DDFS的FPGA實(shí)現(xiàn)

1)相位累加器(地址發(fā)生單元) 設(shè)計(jì)思路為根據(jù)輸入的STep值,計(jì)算出1/4周期采樣的點(diǎn)數(shù)m,然后在時(shí)鐘作用下進(jìn)行計(jì)數(shù),當(dāng)計(jì)數(shù)值達(dá)m個(gè)時(shí),說明一個(gè)象限內(nèi)已經(jīng)取完點(diǎn),此時(shí)象限控制字自加1,計(jì)數(shù)變量重新置零,此時(shí)依次產(chǎn)生了如下(0,Step,…,(m-1)Step)的30位二進(jìn)制地址。截取此地址位的高10位即可用于對(duì)ROM空間的尋址。根據(jù)正弦信號(hào)的特點(diǎn),下一象限產(chǎn)生的地址應(yīng)該為:((m-1)Step,(m-2)Ste-p,…,0),依此類推。且象限控制字自加。

2)ROM存儲(chǔ)單元 ROM存儲(chǔ)單元的數(shù)據(jù)可以通過Matlab進(jìn)行計(jì)算獲得,并將其存儲(chǔ)為dds_sin.mif。也可采用其他高級(jí)語言來獲得ROM存儲(chǔ)數(shù)據(jù)。

3)補(bǔ)碼轉(zhuǎn)換電路 (0,π)數(shù)據(jù)直接輸出,(π,2π)象限的數(shù)據(jù)應(yīng)進(jìn)補(bǔ)碼運(yùn)算。對(duì)此補(bǔ)碼電路稍作修改,即可同時(shí)輸出相位正好相反的兩路正弦信號(hào)。

4)數(shù)據(jù)延時(shí)單元 為了使地址單元輸出的象限控制字等與異步ROM配合工作,應(yīng)對(duì)相應(yīng)的數(shù)據(jù)進(jìn)行延時(shí),以保證輸出數(shù)據(jù)的正確。本設(shè)計(jì)中對(duì)相位控制字延了一個(gè)時(shí)鐘周期。

3 DDFS設(shè)計(jì)模塊性能及所占資源分析

1)DDFS模塊時(shí)序分析 首先應(yīng)當(dāng)分析DDFS模塊的最大時(shí)鐘頻率fmax,因?yàn)樗鼪Q定著系統(tǒng)能否工作在150 MHz或更高的時(shí)鐘頻率。通過Qu-artusII6.0自帶的Timing Analyzer Tools時(shí)序分析,本設(shè)計(jì)中的DDFS模塊的fmax=179.18 MHz,高于150 MHz。故本設(shè)計(jì)理論上可輸出的正弦信號(hào)的最高頻率可達(dá)11.198 MHz。

2)DDFS模塊資源分析 本設(shè)計(jì)使用的是FPGA為Ahem公司的CycloneⅡ系列芯片EP2C5Q208C8,所設(shè)計(jì)的DDFS模塊所占片上資源邏輯單元僅為2%,所占的數(shù)據(jù)存儲(chǔ)空間為12 288 bits,約占總的數(shù)據(jù)存儲(chǔ)空間119 808 bits的10%。可見,通過對(duì)ROM存儲(chǔ)表進(jìn)行數(shù)據(jù)后,DDFS模塊所占片存儲(chǔ)資源較少。因此,F(xiàn)PGA上ROM資源允許調(diào)用若干DDFS模塊來完成各種功能模塊,如2-PSK、2-FSK、2-ASK等數(shù)字調(diào)制。

4 系統(tǒng)性能仿真與測(cè)試

以DDFS模塊為基礎(chǔ),本設(shè)計(jì)實(shí)現(xiàn)了兩組反相的正弦信號(hào)、余弦信號(hào)、三角波信號(hào)、鋸齒波、2-PSK、2-FSK、2-ASK等數(shù)字調(diào)制信號(hào)、掃頻及任意次波形輸出等功能。

在本設(shè)計(jì)中,仿真主要通過QuartusII6.0自帶的Simulator Tool來進(jìn)行數(shù)據(jù)仿真。從仿真圖上可驗(yàn)證該設(shè)計(jì)的正確性。同時(shí),通過Qu-artusII6.0自帶的Signal TapⅡ邏輯分析儀來進(jìn)行邏輯功能的硬件驗(yàn)證。

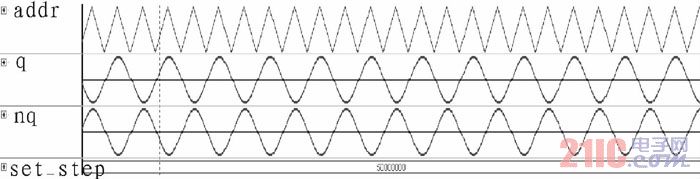

1)基本正弦信號(hào)輸出 在本設(shè)計(jì)中同時(shí)產(chǎn)生兩組信號(hào),一組為正弦信號(hào),另一組與之反相。圖2是步進(jìn)長(zhǎng)度設(shè)定為(50 000 000)10時(shí)的正弦信號(hào)Signal Tap II采樣圖,其頻率分別為fo=582.076 6 kHz。此時(shí)輸出信號(hào)為可產(chǎn)生的最高頻率。從所獲得的輸出信號(hào)的波形上看,頻率較低時(shí),曲線穩(wěn)定且光滑;頻率較高時(shí),波形失真也并不大,可以通過后級(jí)濾波網(wǎng)絡(luò)進(jìn)行波形的進(jìn)一步平滑。且頻率穩(wěn)定度相當(dāng)高。

圖2 S= (50 000 000)10時(shí)的正弦信號(hào)Signal Tap II采樣圖

在外部時(shí)鐘50 MHz的頻率下,可以獲得的最高頻率約為3.125 MHz,最低頻率及頻率步進(jìn)可以低至11.64 MHz。當(dāng)對(duì)外部時(shí)鐘信號(hào)倍頻至150 MHz后,最高輸出頻率可以達(dá)到9.375 MHz,最低頻率及頻率步進(jìn)可以低至34.925 MHz。進(jìn)一步提高頻率及模塊性能,能獲得更大頻率范圍的信號(hào)。

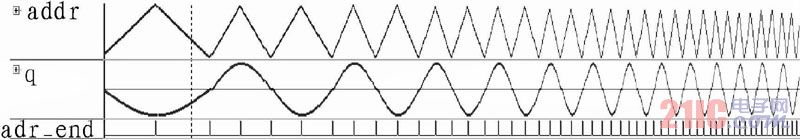

另外,從圖中可以看出,實(shí)際上地址輸出信號(hào)是一組頻率為正弦信號(hào)頻率兩倍的三角波信號(hào)。可見,在產(chǎn)生正弦信號(hào)輸出的同時(shí),還可以產(chǎn)生一組2倍頻的三角波輸出信號(hào),只需取地址位的高12位作為輸出即可。

2)2-ASK、2-FSK、2-PSK數(shù)字調(diào)制信號(hào) 要產(chǎn)生2-ASK、2-FSK、2-PSK等數(shù)字調(diào)制信號(hào)比較容易。只需將數(shù)字基帶信號(hào)在其傳輸時(shí)鐘信號(hào)的作用下,逐位輸入模塊,用基帶數(shù)字信號(hào)的‘1’和‘0’來選擇不同幅度、頻率或相位的正弦信號(hào)輸出即可。

2-ASK信號(hào):用3.125 MHz的信號(hào)表示數(shù)字信號(hào)的‘1’,用輸出幅度為0表示數(shù)字信號(hào)的‘0’。

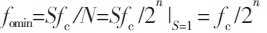

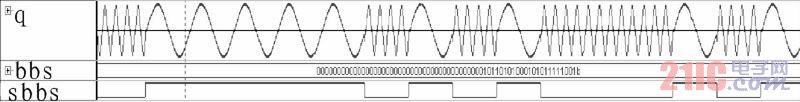

2-FSK信號(hào):用3.125 MHz的信號(hào)表示數(shù)字信號(hào)的‘0’,用582.077 kHz的信號(hào)表示數(shù)字信號(hào)的‘1’,如圖3所示。

圖3 2-FSK信號(hào)字調(diào)制信號(hào)

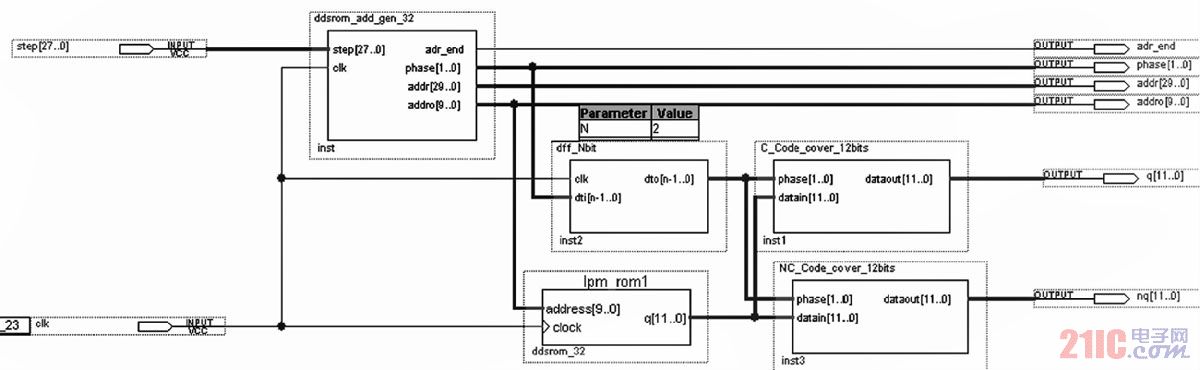

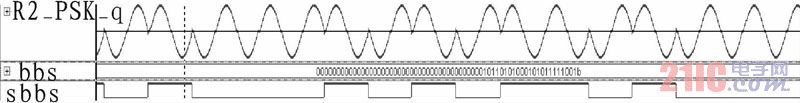

2-PSK信號(hào):用初始相位為0的正弦信號(hào)的‘1’,用初始相位為180°的信號(hào)表示數(shù)字信號(hào)的‘0’。如圖4所示。

圖4 2-PSK信號(hào)字調(diào)制信號(hào)

3)掃頻功能 掃頻功能的實(shí)現(xiàn)是通過改變步進(jìn)來實(shí)現(xiàn)的。每產(chǎn)生一個(gè)周期的正弦信號(hào)以后,將步進(jìn)遞加,為便于觀測(cè),設(shè)計(jì)中設(shè)置S初始值為(50 000 000)10,步進(jìn)遞增幅度為(10000000)10,實(shí)現(xiàn)了掃頻功能,掃頻起始頻率為582.077 kHz。掃頻步進(jìn)約11*15 kHz,掃頻信號(hào)如圖5所示,同時(shí)可以提供各頻率信號(hào)的同步信息。只要改變步進(jìn)初始值及遞增幅度即可完成更寬掃頻范圍及掃頻步進(jìn)更佳的掃頻信號(hào)。事實(shí)上,F(xiàn)M信號(hào)也可以通過對(duì)輸出信號(hào)的步進(jìn)的控制來加以實(shí)現(xiàn)。

圖5 掃頻信號(hào)

5 硬件電路的實(shí)現(xiàn)

設(shè)計(jì)的最終目的是為了用硬件實(shí)現(xiàn)電路,因此,還要設(shè)計(jì)輸入步進(jìn)設(shè)置及模式選擇的鍵盤模塊、頻率設(shè)置數(shù)據(jù)顯示模塊等VHDL程序模塊;后級(jí)的低通濾波網(wǎng)絡(luò),功率放大電路等等。完成這些工作,即可完成一個(gè)完整的DDFS信號(hào)源的設(shè)計(jì)與制作。

6 結(jié)束語

本文的創(chuàng)新點(diǎn)為對(duì)DDFS設(shè)計(jì)進(jìn)行優(yōu)化,充分利用Cyclone II系列FPGA的片上資源,產(chǎn)生了最高頻率可達(dá)9.312 5 MHz.最低頻率分量及頻率分辨率低至MHz量級(jí)的正弦信號(hào)。通過進(jìn)一步優(yōu)化DDFS各模塊的性能,如減少相位累加器、數(shù)據(jù)取補(bǔ)碼等模塊的運(yùn)算時(shí)間,進(jìn)一步提高系統(tǒng)工作的最高頻率;進(jìn)一步優(yōu)化后級(jí)濾波網(wǎng)絡(luò)的特性等,就可以獲得性能曲線更平滑,輸出頻率更高,帶負(fù)載能力更強(qiáng)的優(yōu)質(zhì)的信號(hào)源。同時(shí)還可以增加FFT算法模塊,對(duì)信號(hào)進(jìn)行頻譜分析等其他功能。