隨著數(shù)字信號(hào)處理和集成電路的發(fā)展,要求數(shù)據(jù)處理速度越來越高,基于單片機(jī)+DDS(直接數(shù)字頻率合成)的頻率合成技術(shù)已不能滿足目前數(shù)據(jù)處理速度需求。針對(duì)這一現(xiàn)狀,本文提出了基于FPGA+DDS的控制設(shè)計(jì),能夠快速實(shí)現(xiàn)復(fù)雜數(shù)字系統(tǒng)的功能。

1 AD9910的硬件電路設(shè)計(jì)

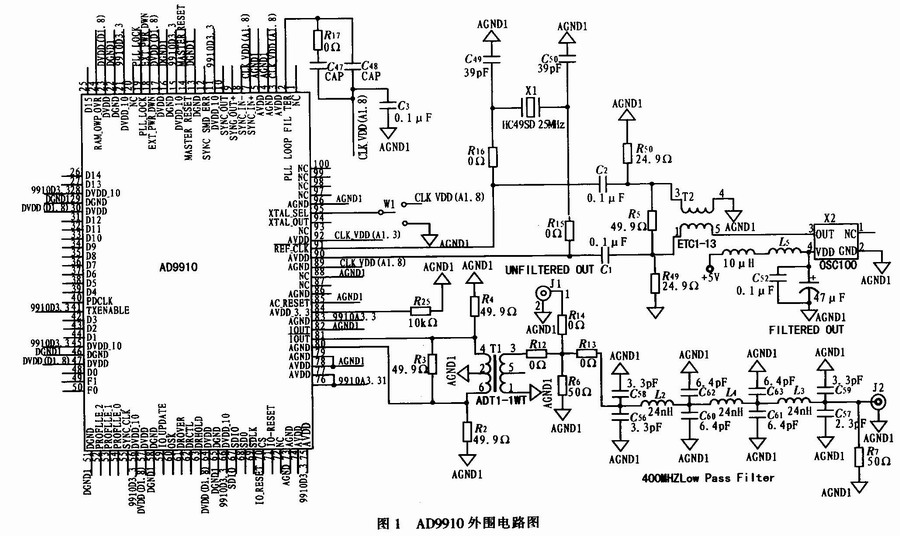

AD9910是ADI公司推出的一款單片DDS器件,內(nèi)部時(shí)鐘頻率高達(dá)1GHz,模擬輸出頻率高達(dá)400 MHz,14-bit的DAC,最小頻率分辨率為0.23 Hz,相位噪聲小于-125 dBc/Hz@1 kHz(400 MHz),窄帶無雜散動(dòng)態(tài)范圍大于80 dB,串行I/O控制,具有自動(dòng)線性和隨機(jī)的頻率、相位和幅度掃描功能,1 024 32位RAM,具有調(diào)幅、調(diào)相的功能,1.8 V和3.3 V供電,可實(shí)現(xiàn)多片同步。應(yīng)用在高靈敏度的頻率合成器、可編程信號(hào)發(fā)生器、雷達(dá)和掃描系統(tǒng)的FM調(diào)制源、測(cè)試與測(cè)量裝置以及高速跳頻系統(tǒng)AD9910芯片的主要外圍電路為:參考信號(hào)源、控制、環(huán)路濾波器和輸出低通濾波器等電路。參考信號(hào)源為AD9910提供基準(zhǔn)頻率,參考信號(hào)輸入芯片后,內(nèi)部的倍頻器和鎖相環(huán)起作用產(chǎn)生1GSPS的系統(tǒng)時(shí)鐘;控制電路通過芯片的I/O給內(nèi)部寄存器寫入內(nèi)容,寄存器內(nèi)容不同,芯片工作狀態(tài)不同,控制芯片可以是單片、FPGA或DSP,本設(shè)計(jì)采用FPGA;

AD9910提供專門的管腳外接環(huán)路濾波器,以優(yōu)化內(nèi)部PLL的性能,環(huán)路濾波器為簡(jiǎn)單的低通濾波器;AD9910輸出高達(dá)400 MHz的模擬信號(hào),為了減少噪聲,在它的輸出端口設(shè)計(jì)了400MHz的低通濾波器。

圖1為實(shí)際設(shè)計(jì)的AD9910外圍連接圖。

在AD9910的電路設(shè)計(jì)中,應(yīng)注意以下幾個(gè)問題:

1)AD9910電源和地設(shè)計(jì)。AD9910需要4組電源,AVDD(1.8 V)、DVDD(1.8 V)、AVDD(3.3 V)和DVDD(3.3 V),模擬電源和數(shù)字電源需要隔離,電源管腳的濾波最好采用鉭電容和陶瓷電容。在PCB設(shè)計(jì)中,數(shù)字地和模擬地分開,用磁珠單點(diǎn)連接,減少干擾。

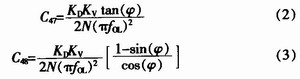

2)AD9910環(huán)路濾波器設(shè)計(jì)。當(dāng)外部的時(shí)鐘較低時(shí),例如100 MHz,系統(tǒng)時(shí)鐘1 GHz,芯片內(nèi)部的鎖相電路起作用,這時(shí)需要在外部設(shè)計(jì)環(huán)路濾波器,如圖1中R17、C47和C48構(gòu)成的RC濾波器,電容電阻值用如下公式計(jì)算。

![]()

其中:N為分頻比,KD為鑒相器的增益,KV是VCO的增益,fOL是環(huán)路帶寬。

3)晶振電路的設(shè)計(jì)。AD9910需要外部提供參考信號(hào)源,它的質(zhì)量直接決定了模擬輸出信號(hào)的質(zhì)量(頻率精度和相位噪聲),本設(shè)計(jì)采用高精度的溫補(bǔ)晶振,頻率100 MHz。在PCB設(shè)計(jì)時(shí)盡量靠近時(shí)鐘管腳。

2 FPGA控制AD9910的軟件實(shí)現(xiàn)

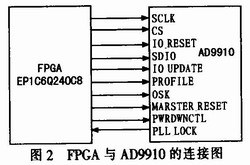

采用ALTERA公司的EP1C6Q240C8控制AD9910,該器件的外部時(shí)鐘頻率為50 MHz,20個(gè)128?36 bit的RAM塊,5980個(gè)邏輯單元(LE),240個(gè)管腳,屬表貼器件。

FPGA與AD9910的外圍電路簡(jiǎn)單,無需外加任何驅(qū)動(dòng)電路,從而節(jié)省了硬件電路設(shè)計(jì)和調(diào)試的時(shí)間,F(xiàn)PGA與AD9910的連接框圖如圖2所示。

其中,SCLK用于輸出數(shù)據(jù)交換的控制時(shí)鐘,CS為片選信號(hào),IO_RFSET控制DDS的系統(tǒng)復(fù)位,SDIO是數(shù)據(jù)傳輸線,IO_UPDATE使能DDS內(nèi)部各寄存器數(shù)據(jù)更新,PROFILE用來選擇八個(gè)相位/頻率寄存器中的一個(gè),OSK用來選擇DDS的輸出鍵控模式,MASTER_RESET用來清除所有存儲(chǔ)單元,并且把寄存器設(shè)為默認(rèn)值,PWRDWNCTL用來選擇是否使用外部使能控制,不使用時(shí)置為0,這里設(shè)置為0,PLL_LOCK用來指示鎖相環(huán)的鎖定狀態(tài)。另外,由于未采用多芯片數(shù)據(jù)通信,所以需將AD9910與同步信號(hào)相關(guān)的引腳懸空,例如7、8、9、10和53引腳。

根據(jù)需要AD9910有4種工作模式可供選擇,分別是單音模式、RAM調(diào)制模式、Digital ramp modulation模式和并行數(shù)據(jù)端口調(diào)制模式。這里選用最基礎(chǔ)的signal-tone單音工作模式。

對(duì)AD9910的17個(gè)寄存器進(jìn)行設(shè)置,這里使用了AD9910的評(píng)估軟件對(duì)寄存器參數(shù)進(jìn)行設(shè)置,只需要在評(píng)估軟件中輸入目標(biāo)參數(shù),軟件將自動(dòng)給出寄存器中的值,這樣減小了工作量。根據(jù)需要,這里僅對(duì)其中的3個(gè)寄存器進(jìn)行設(shè)置,分別是地址為0X01、0X02的控制寄存器和地址為

0X0E的單音模式profile。而其他的寄存器均使用默認(rèn)值,因此無需設(shè)置。

FPGA對(duì)AD9910的軟件控制流程圖如圖3所示。

首先,對(duì)系統(tǒng)進(jìn)行初始化,對(duì)FPCA的各控制信號(hào)進(jìn)行復(fù)位操作,使能CS信號(hào)。

其次,對(duì)3個(gè)主要的寄存器進(jìn)行設(shè)置。設(shè)置地址為0X01的寄存器CFR2,共32位,這里只需要使能第24位單音模式profile的幅度值,默認(rèn)值為0,這里設(shè)為1,其余均使用默認(rèn)值,因此地址為0X01寄存器的內(nèi)容為0X01_40_08_20。

地址為0X02的寄存器CFR3主要用來設(shè)置PLL和VCO的參數(shù)。其中,第26位到第24位用來選擇PLL VCO參考時(shí)鐘的頻帶,這里選擇820~1 150 MHz的VC05,因此為101;第8位是PLL使能的選擇,默認(rèn)值為0,這里選擇使能1;第7位到第1位這7 bit數(shù)據(jù)是PLL倍頻器的倍頻系數(shù),默認(rèn)值

為0000000b,這里對(duì)外部時(shí)鐘進(jìn)行40倍頻,因此,設(shè)置為0101000b。其余各位均使用默認(rèn)值。所以,地址為0X02寄存器的內(nèi)容為0X1D_3F_41_ 50。

對(duì)地址為0X0E的單音模式profile進(jìn)行設(shè)置,它是用來控制DDS的幅度、相位和頻率。其中第61位到第48位這14位用來設(shè)置幅度值,根據(jù)需要在評(píng)估軟件中輸入所需幅度值可以直接查看寄存器中相應(yīng)位的值,這里使用默認(rèn)值00_1000_1011_0101b;第47位到第32位這16位用來設(shè)置相位偏移量,這里仍舊使用默認(rèn)值0X0000;低32位是用來設(shè)置頻率控制字的值,頻率控制字![]() ,其中,fout為輸出頻率,N為頻率控制字的位數(shù),位數(shù)越大輸出頻率的分辨率越高,fc為系統(tǒng)時(shí)鐘1 GHz,這里輸出頻率為50 MHz,對(duì)應(yīng)的頻率控制字為214748365,因此對(duì)應(yīng)位的值設(shè)置為0X0CCC_CCCD。地址為0X0E寄存器的內(nèi)容為0X0885_0000_0CCC_CCCD。

,其中,fout為輸出頻率,N為頻率控制字的位數(shù),位數(shù)越大輸出頻率的分辨率越高,fc為系統(tǒng)時(shí)鐘1 GHz,這里輸出頻率為50 MHz,對(duì)應(yīng)的頻率控制字為214748365,因此對(duì)應(yīng)位的值設(shè)置為0X0CCC_CCCD。地址為0X0E寄存器的內(nèi)容為0X0885_0000_0CCC_CCCD。

最后,結(jié)束IO_UPDATE的操作動(dòng)作,完成一次完整的設(shè)置過程。

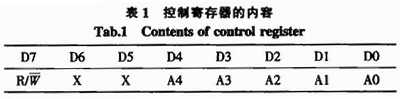

對(duì)寄存器的讀寫操作是通過向輸入端口SDIO發(fā)送8位指令來實(shí)現(xiàn)的,這8位中,最高位為讀寫指令,1為讀操作,0為寫操作,低5位用來選擇在通信周期時(shí)選通哪個(gè)寄存器進(jìn)行數(shù)據(jù)的傳輸,控制寄存器的內(nèi)容,如表1所示。

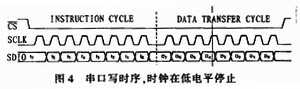

對(duì)AD9910讀寫操作時(shí),需要注意AD9910的時(shí)序要求。對(duì)于串行I/O端口的各種控制信號(hào)之間的有4種基本的時(shí)序關(guān)系,分別是串口寫時(shí)序,時(shí)鐘在低電平停止;三線串口讀時(shí)序,時(shí)鐘在低電平停止;串口寫時(shí)序,時(shí)鐘在高電平停止;兩線串口讀時(shí)序,時(shí)鐘在高電平停止。這里采用第一種時(shí)序關(guān)系,時(shí)序圖如圖4所示。

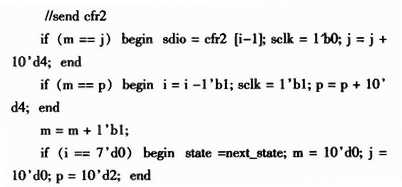

在SCLK上升沿,寫入數(shù)據(jù)有效,F(xiàn)PGA控制SCLK信號(hào)的產(chǎn)生。具體寫入數(shù)據(jù)的程序代碼(使用Vefilog HDL編寫)如下所示:

該指令用于對(duì)地址為0X01的控制寄存器CFR2進(jìn)行寫操作。鑒于FPGA的高速處理能力,在程序設(shè)計(jì)時(shí)需要注意一些特殊的時(shí)序要求,如以下幾個(gè)方面。

1)AD9910開始工作時(shí)必須先將其復(fù)位,復(fù)位時(shí)間保持1 000個(gè)系統(tǒng)工作周期。

2)如果系統(tǒng)工作需要多次使用I/O_UPDATE,要注意I/O_UPDATE引腳置1的時(shí)間控制,這關(guān)系到系統(tǒng)能否順利設(shè)置各個(gè)寄存器。

為了更好的說明FPGA對(duì)AD9910的控制,以下給出相關(guān)例程:

例程中,將update信號(hào)設(shè)置為手動(dòng),通過頻率控制singletone profile0寫入頻率控制字0X0CCC_CCCD,此數(shù)字轉(zhuǎn)換成十進(jìn)制為21474836 5,代入頻率控制字的公式,計(jì)算出頻率為50 MHZ。使用示波器測(cè)量觀察,如圖5所示。

圖中,橫坐標(biāo)為時(shí)間t,單位為納秒(ns),縱坐標(biāo)為電壓幅度(A),單位為毫伏(mv)。可以看出,輸出波形的頻率為50 MHz,與初始設(shè)定值一致。由此可見,程序符合設(shè)計(jì)要求。

3 結(jié)束語

FPGA對(duì)AD9910的控制是通過對(duì)其各個(gè)控制寄存器進(jìn)行相關(guān)設(shè)置來實(shí)現(xiàn)的。隨著FPGA的廣泛應(yīng)用,以及更快的數(shù)據(jù)處理速度,基于FPGA+DDS的方案對(duì)于頻率源的設(shè)計(jì)與實(shí)現(xiàn)具有工程實(shí)踐意義,而且還將在更多的領(lǐng)域得到應(yīng)用。