1 引言

FPGA" title="FPGA">FPGA 是現(xiàn)場可編程門陣列(Field ProgrammingGate Array)的縮寫,用戶可以編寫程序?qū)PGA內(nèi)部的邏輯模塊和I/O模塊重新配置,以實(shí)現(xiàn)芯片的邏輯功能。近年來,F(xiàn)PGA芯片以其大規(guī)模、高集成度、高可靠性、投資少、保密性好、開發(fā)方便、使用靈活、可在線編程等優(yōu)點(diǎn)得到了廣泛的應(yīng)用。隨著FPGA電路在軍工和航空航天領(lǐng)域的應(yīng)用,其高可靠性尤為重要,為了提高電路的可靠性,最好的方法是對電路進(jìn)行篩選,其中老化" title="老化">老化試驗(yàn)就是篩選過程中最為重要的環(huán)節(jié)之一。

考慮到FPGA 電路的工作模式比較復(fù)雜,外部需要存儲器或者FLASH 對其進(jìn)行配置,F(xiàn)PGA 才能動(dòng)態(tài)工作,因此國內(nèi)一般的FPGA老化技術(shù)都采用了靜態(tài)老化試驗(yàn)方法。這種靜態(tài)老化試驗(yàn)方法存在著一定的缺陷,電路在老化過程中并沒有受到真正的應(yīng)力,因此并不能真正剔除掉早期失效的產(chǎn)品,其可靠性得不到保證。對FPGA 電路動(dòng)態(tài)老化的研究,提高老化試驗(yàn)條件的嚴(yán)酷度,即可保證電路的高可靠性要求。

2 動(dòng)態(tài)老化試驗(yàn)

集成電路的動(dòng)態(tài)老化理論上要求電路在其最高溫度工作條件下完全模擬實(shí)際工作狀態(tài),電路內(nèi)部的邏輯單元都有機(jī)會(huì)得到翻轉(zhuǎn),對于一般數(shù)字集成電路都需要外部提供功能測試碼來驅(qū)動(dòng)電路工作。

對于FPGA 電路的動(dòng)態(tài)老化試驗(yàn)來說,功能測試碼是存儲在外部存儲器中的配置程序,將程序配置到FPGA 電路內(nèi)部,使內(nèi)部的門陣列全部工作起來,實(shí)現(xiàn)高覆蓋率的邏輯節(jié)點(diǎn)的翻轉(zhuǎn),讓其按照規(guī)定的功能工作。因此本研究工作的關(guān)鍵在如何進(jìn)行FPGA電路的程序配置。

3 FPGA設(shè)計(jì)流程

完整的FPGA 設(shè)計(jì)流程包括邏輯電路設(shè)計(jì)輸入、功能仿真、綜合及時(shí)序分析、實(shí)現(xiàn)、加載配置、調(diào)試。FPGA配置就是將特定的應(yīng)用程序設(shè)計(jì)按FPGA設(shè)計(jì)流程轉(zhuǎn)化為數(shù)據(jù)位流加載到FPGA 的內(nèi)部存儲器中,實(shí)現(xiàn)特定邏輯功能的過程。由于FPGA電路的內(nèi)部存儲器都是基于RAM 工藝的,所以當(dāng)FPGA電路電源掉電后,內(nèi)部存儲器中已加載的位流數(shù)據(jù)將隨之丟失。所以,通常將設(shè)計(jì)完成的FPGA位流數(shù)據(jù)存于外部存儲器中,每次上電自動(dòng)進(jìn)行FPGA電路配置加載。

4 FPGA配置原理

以Xilinx公司的Qpro Virtex" title="Virtex">VirtexHi-Rel系列XQV100" title="XQV100">XQV100電路為例,F(xiàn)PGA的配置模式有四種方案可選擇:MasterSerial Mode,Slave SerialMode,Master selectMAPMode,Slave selectMAP Mode。配置是通過芯片上的一組專/復(fù)用引腳信號完成的,主要配置功能信號如下:

(1)M0、M1、M2:下載配置模式選擇;

(2)CLK:配置時(shí)鐘信號;

(3)DONE:顯示配置狀態(tài)、控制器件啟動(dòng);

(4)PROG_B:初始化引出端;

(5)INT_B:配置延遲控制,配置錯(cuò)誤顯示;

(6)DOUT:菊花鏈中的配置數(shù)據(jù)輸出。

(7)DIN:串行數(shù)據(jù)輸入;

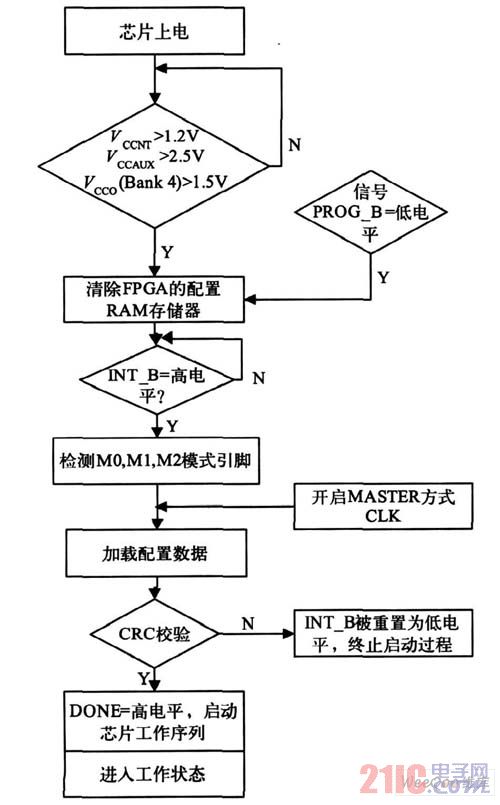

FPGA 電路在選定模式下的配置過程包括四個(gè)主要階段:

(1)清除FPGA 電路內(nèi)部配置存儲器;

(2)初始化FPGA 電路配置邏輯功能;

(3)加載FPGA 電路配置數(shù)據(jù)流;

(4)FPGA 電路配置完成,啟動(dòng)電路就緒序列。

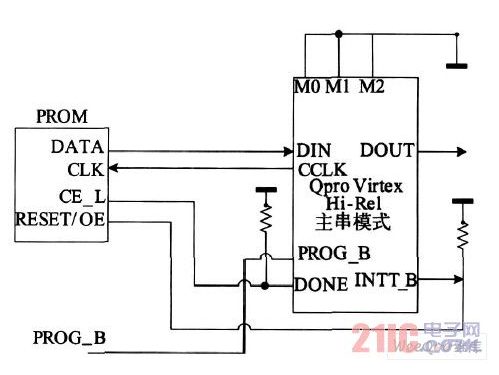

主串模式電路連接圖見圖1。

系統(tǒng)或芯片上電后,信號引腳PROG_B被拉低,F(xiàn)PGA的配置RAM存儲器清空;同樣,PROG_B上的邏輯低電平將會(huì)復(fù)位配置邏輯,并使FPGA 保持在清空配置存儲器狀態(tài)。只要PROG_B 引腳保持低電平,則FPGA 將繼續(xù)清空它的配置RAM存儲器,并使INIT_B信號保持為低電平以表明配置在被清空。

當(dāng)PROG_B被釋放時(shí),F(xiàn)PGA將繼續(xù)使INIT_B保持低電平,直到完成清空所有的配置存儲器。FPGA 在INIT_B信號的上升沿檢測其模式引腳M0、M1、M2。

INIT_B 信號變?yōu)楦唠娖胶螅渲镁涂梢蚤_始了,不需要額外的暫停或等待周期。但是,配置過程不必在INIT_B變化之后就立即開始。配置邏輯只有當(dāng)位流的同步字被載入時(shí)才開始處理數(shù)據(jù)。當(dāng)上電清除配置RAM存儲器后,INIT_B信號引腳變高電平,可以開始載入配置數(shù)據(jù):標(biāo)準(zhǔn)的位流首先是引入空閑字FFFFFFFFh,其次是同步字AA995566h,然后是一些配置控制信息,緊跟其后的才是真正的位流數(shù)據(jù)幀和相關(guān)的CRC;位流的最后是CRC 校驗(yàn)和啟動(dòng)芯片進(jìn)入工作態(tài)。FPGA 電路配置流程圖如圖2 所示。

5 FPGA動(dòng)態(tài)老化板的設(shè)計(jì)

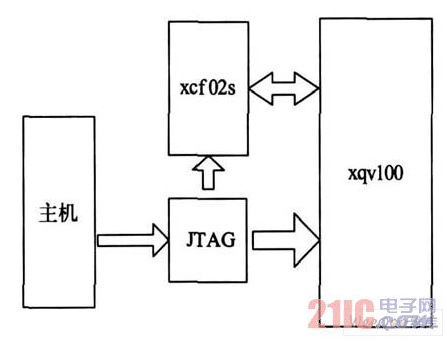

根據(jù)以上討論的配置原理,我們設(shè)計(jì)了XQV100型FPGA 電路動(dòng)態(tài)老化板,如圖3 所示。配置模式采用主串方式(Master SerialMode),這種配置模式有利于簡化PCB的設(shè)計(jì),并且主串模式的配置時(shí)鐘源于FPGA內(nèi)部,不需要外部另外再提供。為了使FPGA電路工作在主串模式,電路的M1、M2、M3引腳都應(yīng)接地。同時(shí),該模式下的外部配置存儲器需要選用串行數(shù)據(jù)傳輸?shù)拇鎯ζ鳎谶@里我們選用Xilinx公司的xcf02s存儲器,內(nèi)部存儲容量最大可達(dá)2 Mbit。

FPGA電路動(dòng)態(tài)老化板采用400mm×400mm的雙層PCB板,在設(shè)計(jì)老化板時(shí)采用去耦及高、低頻RC濾波,對直流電源和信號源采取限流措施。每塊老化板上設(shè)計(jì)4個(gè)老化工位,為了便于在線調(diào)試電路,每個(gè)工位由一個(gè)XCF02S、一個(gè)JTAG 接口、一個(gè)XQV100 組成。FPGA芯片動(dòng)態(tài)配置的邏輯程序放置于xcf02s Flash存儲器中。FPGA動(dòng)態(tài)老化的配置程序采用VHDL語言編寫,采用ISE(V9.1)工具進(jìn)行綜合,利用ModelSim(V6.0)進(jìn)行功能模擬,其具體功能是把全部輸入、輸出管腳分五組,每組都實(shí)現(xiàn)32 分頻功能,每組由外部提供一個(gè)1MHz 的方波信號作為輸入。計(jì)算機(jī)通過Xilinx 專用的JATG下載線將編譯過的配置程序下載到xcf02s 電路中。當(dāng)FPGA電路上電時(shí),xcf02s 中的配置程序自動(dòng)按照串行的方式下載到FPGA的內(nèi)部RAM存儲器中,F(xiàn)PGA 按照程序的功能運(yùn)行。每個(gè)電路選擇一個(gè)輸出端口,輸出頻率在1Hz 左右,在外部連接一個(gè)LED燈作為輸出監(jiān)控,在老化的過程中可通過該燈觀察電路是否正常工作。

6 結(jié)果與分析

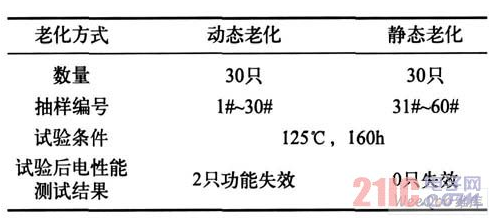

我們以XQV100 型FPGA電路為例,進(jìn)行動(dòng)態(tài)老化和靜態(tài)老化對比試驗(yàn),試驗(yàn)條件選擇溫度為125℃,時(shí)間160h。隨機(jī)抽樣60只常溫測試合格電路,各取30只分別按照動(dòng)態(tài)老化試驗(yàn)方法和靜態(tài)老化試驗(yàn)方法進(jìn)行老化。在動(dòng)態(tài)老化通電時(shí),確保每只電路都有輸出;靜態(tài)老化試驗(yàn)時(shí),確保電源電壓輸入正確。每1h記錄一次,確認(rèn)是否有老化異常情況。

電路在經(jīng)過26h 后,其中有1 只(6#)電路LED不閃爍,初步懷疑已經(jīng)失效,但并沒有立即取出,和其他電路一樣經(jīng)過160h老化,經(jīng)過126h 后21# 電路的LED 不閃爍,同樣繼續(xù)陪試。在老化試驗(yàn)結(jié)束后96h內(nèi)完成了所有電路的常溫電測試,發(fā)現(xiàn)6# 和21#電路功能失效,其余電路都合格,具體情況詳見表1。

表1 動(dòng)態(tài)老化和靜態(tài)老化比對試驗(yàn)結(jié)果

動(dòng)態(tài)老化試驗(yàn)方法和靜態(tài)老化試驗(yàn)方法相比,動(dòng)態(tài)老化試驗(yàn)在通過外圍配置電路的程序驅(qū)動(dòng),使電路的內(nèi)部功能模塊一直處于高速的工作狀態(tài),相反靜態(tài)老化時(shí)雖然有電壓加載,但沒有配置程序驅(qū)動(dòng)電路工作,內(nèi)部模塊并一直處于空閑狀態(tài),因此FPGA電路在動(dòng)態(tài)老化時(shí),所受到的應(yīng)力條件更加嚴(yán)酷,更容易暴露電路本身潛在的缺陷,從而提高了電路本身的可靠性。

7 結(jié)束語

目前,國內(nèi)進(jìn)行FPGA電路的老化大部分還是采用靜態(tài)老化試驗(yàn)方法。特點(diǎn)是電路老化時(shí)不工作,內(nèi)部門陣列不翻轉(zhuǎn),老化過程中無法判斷電路是否有異常。FPGA電路動(dòng)態(tài)老化試驗(yàn)方法的實(shí)現(xiàn)解決了這些問題,增加了輸出監(jiān)測點(diǎn),保證了電路老化過程無異常,從而提高了電路的可靠性。

本文通過對FPGA 電路加載配置過程的流程和原理進(jìn)行研討,設(shè)計(jì)了FPGA 電路動(dòng)態(tài)老化的試驗(yàn)方法,并在工程實(shí)踐中得到了成功的實(shí)現(xiàn)和運(yùn)用。

雖然這里設(shè)計(jì)的電路和配置過程針對Xilinx 公司的Qpro Virtex Hi-Rel系列XQV100電路,但是對其他系列和其他公司FPGA的動(dòng)態(tài)配置也有參考作用。本方法雖然實(shí)現(xiàn)了動(dòng)態(tài)老化的目的,但還是存在著缺陷:現(xiàn)有FPGA電路的內(nèi)部門數(shù)已經(jīng)超過了100萬門,一般的配置程序只能占用FPGA 電路的部分內(nèi)部資源,并且用到的D 觸發(fā)器多了,則移位寄存器就少,通常是顧此失彼,因此要做到100%的動(dòng)態(tài)老化試驗(yàn)還存在著一定的困難。