首先根據(jù)設計要求用MATLAB產(chǎn)生相應的濾波器系數(shù),用CSD碼對系數(shù)進行優(yōu)化,然后采用折疊結構" title="折疊結構">折疊結構,通過代碼實現(xiàn)。設計過程當中還用到分時復用和重定時技術。相比其它半帶濾波器" title="半帶濾波器">半帶濾波器的設計,本設計具有耗費的資源少,整個抽取、濾波過程包括系數(shù)產(chǎn)生始終沒有用到乘法器,而且延遲小、功耗低、面積小、單一時鐘控制有很高的穩(wěn)定性。

作為軟件無線電" title="軟件無線電">軟件無線電的核心技術———上下變頻技術可以通過專用芯片來實現(xiàn)。目前市場上的DDC、DUC品種很多,盡管這些專業(yè)芯片的功能強大但其價格昂貴,工作參數(shù)配置非常的復雜,且由于當前的通信制式多種多樣,專用芯片無法完全滿足軟件無線電系統(tǒng)的性能指標。而FPGA,即現(xiàn)場可編程門陣列,擁有豐富的邏輯資源,可編程性強,可以用于復雜的數(shù)字信號處理比如卷積、相關和濾波等等,為此采用FPGA來實現(xiàn)數(shù)字上下變頻是目前軟件無線電通信系統(tǒng)的主要實現(xiàn)方案。

數(shù)字上下變頻由各種多采樣率數(shù)字濾波器組成,常見的濾波器有C IC濾波器、半帶濾波器、FIR整形濾波器等。半帶濾波器(Half2Band)是一種特殊的F IR濾波器,由于其系數(shù)的對稱性以及將近一半系數(shù)為零值,這使得其濾波運算過程中乘法次數(shù)減少近3 /4,加法次數(shù)減少近一半,同時用于存儲系數(shù)的存儲器也減少了一半,因此半帶濾波器是個高效的數(shù)字濾波器,特別適合實現(xiàn)2的冪次方倍的抽取或者內(nèi)插,有計算效率高,實時性強等特點。流行的半帶濾波器系統(tǒng)級設計方法主要是在MATLAB環(huán)境下根據(jù)設計要求搭建系統(tǒng),用sySTem generator系統(tǒng)設計工具,將模型直接轉化成代碼,然后進行調(diào)用,此方法實現(xiàn)起來比較簡單,一般能夠滿足要求但其存在著功耗高、面積大、資源耗費代價高等不足之處。為了彌補上述不足,本設計首先根據(jù)設計要求用MATLAB產(chǎn)生相應的濾波器系數(shù),然后采用折疊結構,通過代碼編寫來實現(xiàn)。

1 半帶濾波器的設計原理

半帶濾波器(HB)是一種特殊的F IR濾波器,其頻率響應滿足公式1的FIR濾波器。

F IR濾波器可以表示為:

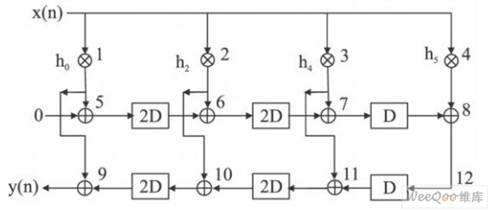

根據(jù)公式2,通常半帶濾波器可以采用直接型或者轉置型結構來實現(xiàn)。由于h ( k ) = h (N - 1 - k) ,采用轉置型結構可以減少乘法器以及加法器的使用,其結構圖如圖1所示。

圖1 轉置型FIR濾波器的結構圖

2 基于折疊結構的半帶濾波器的設計

2. 1 折疊技術的原理

半帶濾波器用作抽取器使用時,其輸出速率為輸入速率的一半,即輸出速率與系統(tǒng)時鐘頻率是1∶2的關系,因此可以把轉置型的半帶濾波器進行折疊,折疊因子為2。為了使得折疊后時序不會出錯,我們首先得算出折疊后各結點之間的延遲值, 延遲可按照公式3進行計算。

其中DF ( u→v)指折疊后功能單元u的輸出到功能單元v的輸入所經(jīng)過的延時數(shù), N 為折疊因子即折疊后功能單元迭代的次數(shù), w ( e)是折疊前功能單元u和功能單元v之間的延時數(shù), Pu 是功能單元u的流水級數(shù), v和u分別是功能單元v和u的編號。計算出各個結點延遲值后我們就可以得到相應的結構圖,然后根據(jù)結構圖編寫代碼。在下采樣當中采用折疊技術,可以大大減少乘法器的使用,減少大量的乘法運算,減少了面積和功耗。

2. 2 基于折疊結構的半帶濾波器的設計

下面以一個基于折疊結構的11階半帶濾波器的設計為例來說明設計的可行性及優(yōu)越性。

2. 2. 1 設計指標

設計指標:系統(tǒng)時鐘為61. 44MHz,半帶濾波器的階數(shù)11 階,系數(shù)為定點18 位,濾波器通帶要求1. 23M,阻帶位置要求為30. 72 - 1. 75 = 28. 97M。

2. 2. 2 下采樣數(shù)據(jù)率變換

半帶濾波器作為抽取器使用時,其抽取因子為2,即輸出速率為輸入速率的一半,也就是說輸出速率與系統(tǒng)時鐘頻率是1: 2的關系。為了采用折疊技術,同時也方便整個濾波過程的時序控制,首先我們利用系統(tǒng)時鐘產(chǎn)生一個同步控制信號cONtr_ rw。

同步控制信號contr_ rw的初始值為1,在每個系統(tǒng)時鐘上升沿到來時,其值在0與1之間進行跳變,其它時候數(shù)值保持不變,也就是說在第一個系統(tǒng)時鐘上升沿到來時, contr_ rw的值由1跳變?yōu)?,此值一直保持著,直到第二個系統(tǒng)時鐘上升沿到來時, contr_rw的值才由0跳變?yōu)?,同樣此值也一直保持到第三個系統(tǒng)時鐘上升沿到來時才發(fā)生跳變。由此可見contr_rw的值只有在系統(tǒng)時鐘上升沿到來時才發(fā)生跳變,為此我們可以用此同步控制信號作為分路器(DEMUX)的選通開關把輸入數(shù)據(jù)分成奇、偶2個通道,以此達到下采樣數(shù)據(jù)率變換。當系統(tǒng)時鐘上升沿到來時,如果同步控制信號contr_ rw的值為0,則把輸入數(shù)據(jù)送入奇通道,此時偶通道送入的是0值;如果contr_rw的值為1,則把輸入數(shù)據(jù)送入偶通道,此時奇通道送入的是0值;緊接著在經(jīng)過兩級的數(shù)據(jù)率穩(wěn)定之后,奇、偶2個通道的數(shù)據(jù)率均為系統(tǒng)時鐘頻率的一半,也就是說此時奇、偶通道均為每兩個時鐘變化一次數(shù)據(jù)。根據(jù)公式2,我們知道此11階半帶濾波器的輸出為:

由此表達式我們知道x ( n) h0、x ( n - 2) h2、x ( n - 4) h4、x (n - 6) h4、x (n - 8) h2、x (n - 10) h0 是根據(jù)奇通道數(shù)據(jù)產(chǎn)生的, x (n - 5) h5 是根據(jù)偶通道數(shù)據(jù)產(chǎn)生的。為了節(jié)約資源同時也為后續(xù)的折疊技術的應用,系數(shù)h2、h4 采用分時復用技術,當同步控制信號contr_rw的值為0時產(chǎn)生系數(shù)h4、contr_rw的值為1時產(chǎn)生系數(shù)h2。

2. 2. 3 各結點延時單元計算

首先我們把設計當中用到的每個乘法器和加法器都當成一個結點,在應用折疊技術之前我們必須先知道各結點之間的延時值。如圖1所示我們標注好每個結點的編號,為了讓其結構具有對稱性,我們把圖1當中的結點12當成是一個加法器,此加法器的輸入分別為: 0值和結點8的輸出值。由于時鐘頻率是輸出速率的2倍,因此折疊因子N = 2, 此時所有編號為奇數(shù)的結點其u或者v值均為0,所有編號為偶數(shù)的結點其u或者v值均為1,根據(jù)公式3我們可以算出各個關鍵結點之間的延遲值為:DF ( 5→6) = 5、DF (6→7) = 3、DF ( 7→8) = 3、DF ( 8→12) =0、DF (12→11) = 1、DF ( 11→10) = 5、DF ( 10→9) =3。根據(jù)這些延遲值,我們知道完成一次的濾波工作需要22個系統(tǒng)時鐘和20個D觸發(fā)器。為了能夠以最快的速度完成濾波功能,這時可以引入重定時技術對D觸發(fā)器進行分配,在滿足時序的情況下減少D觸發(fā)器的使用, 從而減少延遲。重定時后各結點的延遲值為: DF ( 5→6) = 3、DF ( 6→7) = 1、DF ( 7→8) = 1、DF ( 8 →12) = 0、DF ( 12 →11) = 1、DF ( 11 →10) = 3、DF ( 10→9) = 1,也就是說采用重定時以后完成一次的濾波工作只需11個系統(tǒng)時鐘和10個D觸發(fā)器。于是根據(jù)這些延遲值我們便得到了折疊結構的結構圖,如圖2所示。

圖2 基于折疊結構的半帶濾波器的結構圖

2. 2. 4 時序分析

圖2當中的0表示同步控制信號contr_rw的值為0, 1表示同步控制信號contr_rw的值為1,為了方便分析,我們把圖2當中的加法器按照從左到右,從上到下的順序依次編號為加法器1、加法器2、加法器3、加法器4,用fm0mul_w表示通道送給加法器1的輸入, 用fm0add _ r 表示加法器1 的輸出; 用fm1mul_w表示通道送給加法器2的輸入,用fm1add_r表示加法器2的輸出,其它類推。接下來簡要的分析下該設計是如何工作的。

第一個時鐘Clock1:同步控制信號contr_ rw的值為0,通道送入加法器1 的數(shù)據(jù)為x ( 0) h0 , 加法器1的另一個輸入值為0,此時加法器1的輸出值為x (0) h0 ;通道送入加法器2的數(shù)據(jù)為x ( 0) h4 ; 通道送入加法器3的數(shù)據(jù)為x ( 0) h0 ;通道送入加法器4的數(shù)據(jù)為x (0) h4。

第二個時鐘Clock2:同步控制信號contr_ rw的值為1,通道送入加法器1的數(shù)據(jù)為x (0) h2 ;通道送入加法器2的數(shù)據(jù)為x (1) h5 ;通道送入加法器3的數(shù)據(jù)為x (0) h2 ;送入加法器4的數(shù)據(jù)為0。

第三個時鐘Clock3、第四個時鐘Clock4、第五個時鐘Clock5、第六個時鐘Clock6可按照此方法依此類推,具體時序參見表1。

第七個時鐘Clock7:同步控制信號contr_ rw的值為0,通道送入加法器1的數(shù)據(jù)為x (6) h0 ,加法器1的另一個輸入值為0, 此時加法器1 的輸出值為x (6) h0 ;通道送入加法器2 的數(shù)據(jù)為x ( 6 ) h4 , 在Clock6產(chǎn)生的fm0add_ r經(jīng)過1個時鐘延時成為此時刻加法器2的另外一個輸入值,于是此時加法器2的輸出值為x (2) h0 + x (4) h2 + x (6) h4 ;通道送入加法器3的數(shù)據(jù)為x (6) h0 ;通道送入加法器4的數(shù)據(jù)為x ( 6) h4 ,在Clock6產(chǎn)生的fm3add_ r經(jīng)過1個時鐘延時成為此時刻加法器4的另外一個輸入值,于是此時加法器4的輸出值為x ( 0) h0 + x ( 2) h2 +x (4) h4 + x (5) h5 + x (6) h4。

第八個時鐘Clock8、第九個時鐘Clock9、第十個時鐘Clock10 可以按此方法類推, 具體時序參見表1。

第十一個時鐘Clock11: 同步控制信號contr_rw的值為0,通道送入加法器1 的數(shù)據(jù)為x ( 10 )h0 ,加法器1 的另一個輸入值為0, 此時加法器1的輸出值為x ( 10) h0 ;通道送入加法器2的數(shù)據(jù)為x ( 10) h4 ,在Clock10產(chǎn)生的fm0add_ r經(jīng)過1個時鐘延時成為此時刻加法器2 的另外一個輸入值,于是此時加法器2的輸出值為x ( 6) h0 + x ( 8) h2 +x (10) h4 ;通道送入加法器4的數(shù)據(jù)為x ( 10) h4 ,在Clock10產(chǎn)生的fm3add_r經(jīng)過1個時鐘延時成為此時刻加法器4的另外一個輸入值,于是此時加法器4的輸出值為x ( 4) h0 + x ( 6) h2 + x ( 8) h4 + x ( 9) h5+ x (10) h4。通道送入加法器3的數(shù)據(jù)為x ( 10) h0 ,在Clock10產(chǎn)生的fm2add_r經(jīng)過1個時鐘延時成為此時刻加法器3的另外一個輸入值,于是此時加法器3的輸出值為x ( 0 ) h0 + x ( 2 ) h2 + x ( 4 ) h4 +x (5) h5 + x (6) h4 + x (8) h2 + x (10) h0。

以上是基于折疊結構的11階半帶濾波器一個完整的濾波過程。具體的各個結點的時序如表1所示。

表1 時序表

3 仿真與實現(xiàn)

本設計采用Verilog語言編寫,所采用的芯片是Xilinx公司的xc4vsx35 - 10ff668,用ISE10. 1和Modelsim進行仿真驗證。仿真結果、綜合報告圖如圖3、圖4所示。從圖3我們可以看出采用折疊技術的半帶濾波器,其系數(shù)的產(chǎn)生以及最終濾波器的輸出完全正確,完全滿足我們的設計要求。

傳統(tǒng)的直接型半帶濾波器的設計單單濾波過程,不包括系數(shù)的產(chǎn)生和抽取過程,需要10個D觸發(fā)器、7個乘法器、6個加法器,而轉置型半帶濾波器則需要10個D 觸發(fā)器、4 個乘法器、7 個加法器。

然而從圖4我們可以看到整個半帶濾波器耗費的資源相當?shù)纳伲偣灿昧?3 個加法器, 16 個寄存器。而由此可見采用折疊結構實現(xiàn)半帶濾波器的設計能夠大大減少資源的耗費,而且整個過程沒有用到乘法器只是用到少量的加法器和寄存器,減少了大量的乘法帶來的額外的面積和功耗。同時本設計還經(jīng)過硬件電路的驗證,工作正常穩(wěn)定,符合設計要求。

圖3 基于折疊結構的11階半帶濾波器仿真圖

圖4 基于折疊結構的11階半帶濾波器綜合報告圖

4 結論

本文以11階半帶濾波器的設計為例,介紹了折疊技術在半帶濾波器上的應用。與傳統(tǒng)的設計相比其有很大的優(yōu)越性和突破,單一時鐘控制,并且設計過程當中沒用到乘法器,大大減少了硬件資源,同時也使設計面積和功耗大為減少,穩(wěn)定性高!