提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設(shè)計(jì)方案,并給出了PCI總線接口芯片寄存器配置實(shí)例,介紹了軟件包WinDriver開發(fā)設(shè)備驅(qū)動程序的具體過程。

隨著計(jì)算機(jī)技術(shù)的不斷發(fā)展,為滿足外設(shè)間以及外設(shè)與主機(jī)間的高速數(shù)據(jù)傳輸,Intel公司于1991年提出了PCI總線概念。PCI總線是一種能為主CPU及外設(shè)提供高性能數(shù)據(jù)通訊的總線,其局部總線在33MHz總線時鐘、32位數(shù)據(jù)通路時,數(shù)據(jù)傳輸速率最高可達(dá)133Mbps。實(shí)際應(yīng)用中,可通過PCI總線實(shí)現(xiàn)主機(jī)與外部設(shè)備的高速數(shù)據(jù)傳輸,有效解決數(shù)據(jù)的實(shí)時傳輸和存儲問題,為信號的實(shí)時處理打下良好基礎(chǔ)。

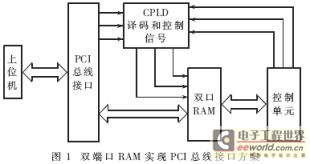

本文主要提供一種基于PCI總線的數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)方案,其中雙口RAM起橋梁作用,完成上位機(jī)與外圍主控單元之間的數(shù)據(jù)握手。

1 雙端口RAM實(shí)現(xiàn)PCI總線接口方案

本系統(tǒng)主要用于解決上位機(jī)與外圍控制單元的數(shù)據(jù)傳輸問題。上位機(jī)運(yùn)行信息診斷程序,通過PCI總線與外圍控制單元以一定速率傳輸數(shù)據(jù),在主機(jī)中實(shí)時監(jiān)控并保存數(shù)據(jù)。由于實(shí)現(xiàn)高速實(shí)時數(shù)據(jù)傳輸,數(shù)據(jù)量大,所以在PCI局部總線上插入一個高速雙端口RAM。雙端口RAM一端作為PCI總線接口的本地端存儲器,一端作為DSP目標(biāo)存儲器。需要傳輸保存的數(shù)據(jù)經(jīng)DSP處理后借助雙端口RAM和PCI總線接口完成了上位機(jī)與DSP的數(shù)據(jù)握手。本文提出的雙端口RAM實(shí)現(xiàn)PCI總線接口方案如圖1。

考慮到PCI總線接口對局部總線的控制時序比較復(fù)雜,需要譯碼和控制電路來實(shí)現(xiàn)局部總線的訪問及控制。本系統(tǒng)使用CPLD解決雙口RAM的地址訪問競爭沖突問題。需解決的主要問題有:①PCI接口電路設(shè)計(jì);②CPLD地址譯碼和總線仲裁;③PCI總線驅(qū)動程序開發(fā)。

2 PCI接口電路設(shè)計(jì)

PCI卡的設(shè)計(jì)一般采用兩種方案。一種是根據(jù)PCI協(xié)議在FPGA或CPLD中實(shí)現(xiàn)PCI總線接口控制器,但是由于PCI協(xié)議的復(fù)雜性,使得開發(fā)難度大、周期長;另一種使用現(xiàn)成的PCI接口芯片,用戶開發(fā)難度降低,只把重點(diǎn)放在PCI接口芯片局部總線的接口設(shè)計(jì)和PCI總線配置空間的初始化,而不用速度考慮PCI總線規(guī)范上眾多的協(xié)議規(guī)范,加快了開發(fā)時間。

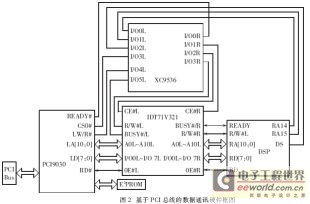

本數(shù)據(jù)傳輸系統(tǒng)使用PLX公司的PCI9030總線接口芯片,以CPLD完成邏輯控制及與外設(shè)的連接,整個系統(tǒng)的硬件框圖如圖2。其中雙端口RAM采用IDT71V321,CPLD選用XILINX公司的XC9536CPLD芯片,EEPROM選用NS公司的93CS56,控制單元DSP選用TMS320LF2407A。

<Script type=text/javascript>function ImgZoom(Id)//重新設(shè)置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w< m){return;} else{ var h = $(Id).height; $(Id).height = parseInt(h*m/w); $(Id).width = m; } } window.onload = function() { var Imgs = $("content").getElementsByTagName("img"); var i=0; for(;i

<Script type=text/javascript>function ImgZoom(Id)//重新設(shè)置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w< m){return;} else{ var h = $(Id).height; $(Id).height = parseInt(h*m/w); $(Id).width = m; } } window.onload = function() { var Imgs = $("content").getElementsByTagName("img"); var i=0; for(;i

2.1PCI9030內(nèi)部結(jié)構(gòu)及其數(shù)據(jù)傳輸

PCI9030是PLX公司開發(fā)的PCI總線目標(biāo)接口芯片。其特點(diǎn):低功耗,PQFP176針封裝,符合PCIV2.2規(guī)范;在PCI總線上是從設(shè)備,但在局部總線上是主設(shè)備;PCI9030支持突發(fā)傳輸,有5個PCI總線到局部總線地址空間,9個可編程的通用I/O,4個可編程的片選,支持熱插拔。PCI 9030主要由PCI總線接口邏輯、局部總線接口邏輯、串行E2PROM接口邏輯和內(nèi)部邏輯組成,結(jié)構(gòu)框圖見圖3。

PCI9030支持PCI主設(shè)備直接訪問局部總線上的設(shè)備,數(shù)據(jù)傳輸方式分為內(nèi)存映射的突發(fā)傳輸和I/O映射的單次傳輸,并且由PCI基址寄存器設(shè)置在PCI內(nèi)存和I/O空間中的合適位置,另外局部映射寄存器允許PCI地址空間轉(zhuǎn)換到局部地址空間。

2.2配置實(shí)例

系統(tǒng)訪問的雙口RAM存儲空間為2KB,要求將這個存儲器空間映射到局部地址空間0,采用內(nèi)存方式映射,存儲器的數(shù)據(jù)寬度為8位,并且不采用突發(fā)傳輸,讀寫時不可預(yù)取。下面介紹這個地址空間各個寄存器的具體配置過程。

(1)配置地址范圍寄存器

根據(jù)PCI配置寄存器與LAS0RR的對應(yīng)關(guān)系以及雙口RAM的地址空間800H,取7FFH的補(bǔ)碼得到FFFFF800H。又因?yàn)榘凑赵O(shè)計(jì)要求,要映射到內(nèi)存空間的任何位置并且設(shè)置為不可預(yù)取的,這樣LASORR寄存器后3位應(yīng)該為000H。所以LAS0RR的值應(yīng)該最終確定為FFFFF800H。

(2)配置基址寄存器

該寄存器的基址必須是地址空間范圍的整數(shù)倍,在本例中必須是2K的整數(shù)倍,可將基地址定為00004000H,又由于基址寄存器位0為空間使能位,所以應(yīng)將這一位設(shè)置1;至于位2、位3,由于是映射到內(nèi)存空間,設(shè)為00H即可。所以LAS0BA的值最終被確定為00004001H。

(3)配置片選信號控制寄存器

該寄存器的地址范圍和基地址必須與LAS0RR或LAS0BA所定義的范圍和空間相對應(yīng)。可根據(jù)PCI9030提供的配置寄存器的方法確定CS0BASE的數(shù)值:板卡的2KB空間可以用十六進(jìn)制表示為800H,將800H右移一位得到400H,然后將基地址加到400H左邊的任何一位中。因?yàn)樗捎玫幕刂窞?0004000H,所以得到的值為00004400H;又因?yàn)榈?位為片選使能位,應(yīng)該設(shè)置為1。所以最終確定的數(shù)值為00004401H。

由于局部總線采用8位的寬度,將工作方式定義在不使能突發(fā),不預(yù)取,配置總線區(qū)域描述寄存器的數(shù)值確定為400140A2H。另外,還要根據(jù)要求設(shè)置CNTRL寄存器控制PCI9030的工作狀態(tài),確定為18784500H。當(dāng)所有這些數(shù)據(jù)都配置完成后,便可將這些數(shù)據(jù)按照加載順序?qū)懭氪蠩2PROM中,從而完成整個系統(tǒng)的配置。

通過這幾個寄存器的配置,一個局部地址空間便可以確定下來。在系統(tǒng)上電后,系統(tǒng)BIOS根據(jù)這幾個寄存器的內(nèi)容將板卡上2KB的RAM空間重映射到PCI空間中,使主機(jī)可以像訪問自己的地址空間一樣訪問板卡上的RAM。

2.3CPLD控制邏輯

對于雙口RAM同一個地址單元,不能同時進(jìn)行讀或?qū)懖僮鳎珒蛇呥B接的主控芯片,都可以對其進(jìn)行讀、寫操作,因此必須解決地址競爭問題。本系統(tǒng)中,使用XILINX公司的XC9536CPLD芯片完成PCI局部總線的譯碼和控制電路。由于系統(tǒng)控制計(jì)算主要在DSP中完成,上位機(jī)只起監(jiān)控和數(shù)據(jù)保存作用,因此規(guī)定對雙口RAM的操作DSP優(yōu)先于PCI9030;同時CPLD也參與了DSP片外程序存儲器Flash和數(shù)據(jù)存儲器RAM的地址譯碼,控制邏輯用公式表示為:

3設(shè)備驅(qū)動程序設(shè)計(jì)

設(shè)備驅(qū)動程序開發(fā)工具通常有DDK、VtoolsD、WinDrvr等。為加快開發(fā)速度,采用JUNDO公司的WinDrvr開發(fā)設(shè)備驅(qū)動程序。其使用簡單,支持多種操作系統(tǒng)。

采用Windrvr開發(fā)PCI橋接設(shè)備的驅(qū)動程序有兩種方法。一種Wizard開發(fā)向?qū)亲詣由沈?qū)動程序框架代碼,然后根據(jù)實(shí)際需要,加入定制功能。這種方法生成的代碼較多,程序較復(fù)雜。另一種是在Vc++創(chuàng)建工程中直接利用Windrvr的API函數(shù)生成驅(qū)動程序,比在Wizard生成的框架代碼上修改更為靈活。本文采用后一種方法。以下是用Windrvr開發(fā)PCI9030橋芯片的驅(qū)動代碼,只要稍加改動就可以作為其他PCI芯片驅(qū)動程序的一部分,例如PCI9050、PCI9052等。程序中出現(xiàn)的變量名都由其名稱反映含義,具體可以參見Windrvr設(shè)計(jì)文檔說明。

至此獲得了本地端映射到用戶的內(nèi)存地址,調(diào)用讀寫函數(shù)就可以對本地芯片進(jìn)行操作。