摘 要: 提出一種基于時間測量" title="時間測量">時間測量的BPSK信號非相干解調(diào)方法,,給出了信號解調(diào),、同步時鐘" title="同步時鐘">同步時鐘提取的原理和實驗驗證結(jié)果。該方法可以軟件實現(xiàn),亦可硬件實現(xiàn),,并可同時輸出與解調(diào)數(shù)據(jù)同步的時鐘,為使用單片機或可編程器件" title="可編程器件">可編程器件實現(xiàn)BPSK信號解調(diào)提供了一個有效的低成本方案,。

關(guān)鍵詞: BPSK 非相干 解調(diào)

二進制移相鍵控(BPSK)是一種常用的數(shù)字信號調(diào)制方式,,廣泛用于衛(wèi)星、微波通信,、廣播電視等諸多領(lǐng)域,。BPSK信號是抑制載波的雙邊帶信號,信號中不存在載頻分量,,因而BPSK信號的相干解調(diào)需要通過非線性變換,,如Costas環(huán)、平方環(huán)電路,、數(shù)字鎖相環(huán)(DPLL)技術(shù)等方法提取載頻信號[1],,需要較為復(fù)雜的載波恢復(fù)電路。近年來,,隨著智能卡,、RFID、BlueTooth等相關(guān)技術(shù)的發(fā)展,,較低碼率的BPSK在近距離無線產(chǎn)品中也得到了越來越廣泛的應(yīng)用,,因而成本較低的BPSK非相干解調(diào)越來越受重視。在BPSK的非相干解調(diào)方法中,,比較重要的是移相鍵控信號的非相干反饋判決接收機[2]和多符號最大" title="最大">最大似然接收機[3],。文獻[4]針對文獻[2]中的部分電路用最大似然方法進行了結(jié)構(gòu)分析,指出這兩種接收機是相互關(guān)聯(lián)的,。文獻[5]對反饋判決接收機和多符號最大似然接收機的性能進行了分析,,指出兩者性能相近,而反饋判決接收機結(jié)構(gòu)要簡單些,,因而在實現(xiàn)上更有吸引力,。文獻[6]提出了基于知識優(yōu)化的PSK信號的非相干解調(diào),并介紹了一種反饋判決式的延遲遞歸解調(diào)結(jié)構(gòu),。上述文獻均從模擬信號處理的角度給出了移相鍵控信號的非相干解調(diào)方案,,其結(jié)構(gòu)比相干方式有所簡化,但是仍然需要較多的硬件電路,。此外,,還有一類較為實用的中低速BPSK信號的非相干解調(diào)方法:文獻[7]給出了一種精巧的BPSK解調(diào)電路,該電路通過引入一個窄帶振蕩器,使其中心頻率與BPSK信號的載波頻率相等,,當(dāng)BPSK信號通過該振蕩器時,,因其通頻帶太窄,信號在碼元交替時刻的相移不能突變,,使得BPSK的頻率發(fā)生偏移,,導(dǎo)致振蕩器失諧和輸出電壓下降,利用這種電壓下降實現(xiàn)BPSK信號的非相干解調(diào),。文獻[8]是利用BPSK信號在相位突變點有兩個半余弦周期的特點實現(xiàn)的,,實現(xiàn)中亦額外使用了模數(shù)轉(zhuǎn)換器。針對中低速BPSK的低成本解調(diào)需求,,本文提出了一種基于時間測量的BPSK非相干解調(diào)方法,。該方法將BPSK波形量化成數(shù)字脈沖串后,通過測量碼元交替時不同的時間間隔" title="時間間隔">時間間隔判決對應(yīng)的碼元類型,,以達到非相干解調(diào)的目的,。該方法可以采用軟件解調(diào),只需要很少的硬件電路進行信號整形,,同時還可以輸出與解調(diào)數(shù)據(jù)同步的時鐘,。對于較高的碼率,該方法也可以用FPGA等可編程器件硬件實現(xiàn),,因而為使用單片機或可編程器件實現(xiàn)BPSK信號解調(diào)提供了一個有效的低成本方案,。

1 BPSK信號特點及其波形變換

二進制相移鍵控中,載波的相位隨調(diào)制信號1或0而改變,。通常用相位0和π來分別表示1或0,,則已調(diào)信號的時域表達式為:

x(t)=A·cos(2πf·t+Φi)??????????? (1)

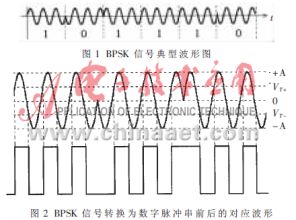

式(1)中,,A為信號幅值,、f為載波頻率、φi=0或π,,分別對應(yīng)于調(diào)制數(shù)據(jù)1或0,。圖1給出了BPSK信號的時域波形圖,設(shè)每個碼元對應(yīng)三個完整的載波周期,。

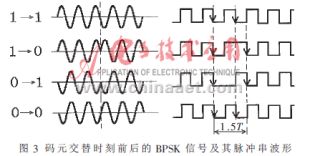

本文中,,解調(diào)過程將基于對時間的測量。為準確計時,,時間測量所用的觸發(fā)信號采用脈沖信號,,因而在解調(diào)前,首先需要將圖1所示的模擬波形轉(zhuǎn)換為數(shù)字脈沖,。圖2是BPSK信號轉(zhuǎn)換前后的對應(yīng)波形,,其中VT+、VT-為轉(zhuǎn)換門限電平。為了減少誤碼率,,應(yīng)盡量使VT+與VT-相等,,從而使得脈沖的正負跳變沿對應(yīng)BPSK信號相位做整體平移,以減少相位噪聲,。上述脈沖形成電路可以通過施密特觸發(fā)器(帶正反饋的遲滯比較器)實現(xiàn),。

2 解調(diào)原理

圖2輸出的脈沖串將作為本文方法的輸入,用以提取二進制碼流及其同步時鐘,。討論解調(diào)方法之前,,首先觀察兩個碼元交替時刻的BPSK信號及其對應(yīng)脈沖串之間的時序關(guān)系,如圖3,。設(shè)BPSK的載頻周期為T,。從圖3可以看出,在兩個碼元交替時刻,,從前一個下降沿(或上升沿)開始計時,,如果在時刻T又出現(xiàn)了新的下降沿,對應(yīng)的碼元值不變(即0-0或1-1),。而在1.5T時刻出現(xiàn)新的下降沿時,,對應(yīng)的碼元值有變化(即0-1或1-0)。根據(jù)圖3,,如設(shè)置一計時器,,當(dāng)兩個相鄰脈沖下降沿之間的時間間隔為T時,對應(yīng)數(shù)據(jù)沒有發(fā)生翻轉(zhuǎn),;而當(dāng)兩個下降沿之間的時間間隔為1.5T時,,則對應(yīng)數(shù)據(jù)必然發(fā)生翻轉(zhuǎn)。是否發(fā)生碼元電平翻轉(zhuǎn),,明確對應(yīng)于兩個不同的時間間隔,。據(jù)此,即可實現(xiàn)BPSK信號的非相干解調(diào),。

下面討論如何生成數(shù)據(jù)的同步時鐘,。在上述解調(diào)過程中,如果相鄰數(shù)據(jù)電平發(fā)生了翻轉(zhuǎn),,即可從該解調(diào)數(shù)據(jù)得到一個同步時鐘沿,;而當(dāng)相鄰數(shù)據(jù)沒有翻轉(zhuǎn)時,是無法直接生成相應(yīng)的時鐘跳變的,。圖4所示是一串比較長的BPSK脈沖序列,,其中每個碼元對應(yīng)的載波周期數(shù)為K(為簡便起見,圖4中每個碼元對應(yīng)的載波周期數(shù)仍為3),。由圖4可見,,如前后兩個碼元值有變化,從上一個碼元結(jié)束到下一個碼元開始,中間持續(xù)的時間可能為K-1個或者K個載波周期,;如果前后兩個碼元值沒有變化,,那么一個碼元的持續(xù)時間可用K+1個載波周期表示。根據(jù)上述特點,,如果在解調(diào)流程中再設(shè)置一個值為K+1的計數(shù)器,,根據(jù)以上對T、K兩個參數(shù)的研究,,信息碼流的解調(diào)用一個定時器即可實現(xiàn),;如需要同時得到同步時鐘,則必須結(jié)合定時器和計數(shù)器實現(xiàn),,如圖5,。

根據(jù)圖4和圖5,如果前后兩個碼元值有變化,,計數(shù)器計到K-1個或者K個載波脈沖后,,定時器發(fā)出定時溢出信號Over,由該信號觸發(fā)產(chǎn)生同步時鐘Clock和信息碼流Data,,同時清零并重啟計數(shù)器和定時器,。在此過程中,計數(shù)器因為一直沒有計滿K+1個脈沖,,它不發(fā)出任何信號,;如前后兩個碼元值沒有變化,定時器始終不會產(chǎn)生溢出信號,,此時應(yīng)在第K+1個載波脈沖到來時由計數(shù)器生成一個同步脈沖Clock,,同時清零并重啟計數(shù)器和定時器。通過對上述定時器和計數(shù)器的輸出作適當(dāng)?shù)碾娐方M合,,即可得到所需的解調(diào)碼流Data和同步時鐘Clock,。圖5中,定時器定時長度為T+ΔT,,ΔT∈[0,,T/2]。顯然,,當(dāng)ΔT=T/4時,系統(tǒng)的噪聲性能最好,。

3 實驗驗證

下面通過一個實際電路對上述解調(diào)方法進行驗證,,如圖6所示。其中,,脈沖形成電路由一個帶正反饋電路的運算放大器組成,,實現(xiàn)圖2所示的功能。解調(diào)部分完成圖5所示的功能,由單片機內(nèi)固化的軟件來實現(xiàn),。

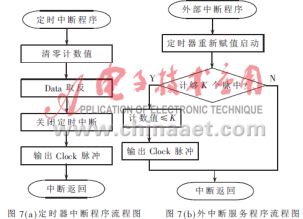

圖6中,,解調(diào)的實際操作由單片機AT89C2051完成。在具體的解調(diào)過程中,,為保證速度,,定時器和計數(shù)器都工作在中斷方式,所有的解調(diào)操作也完全由兩個中斷服務(wù)子程序完成,。圖7給出了定時中斷和計數(shù)中斷的程序流程圖,。

由簡單計算可知,如果AT89C2051采用12MHz晶振,,該驗證方案能夠解調(diào)的BPSK信號的最大載頻約為25kHz,。圖8給出了從示波器上輸出的解調(diào)波形圖。實驗中,,BPSK模擬信號由信號發(fā)生器產(chǎn)生,,信號載頻為16kHz,對應(yīng)T=62.5μs,;為了能在示波器上看清各路信號的對應(yīng)關(guān)系,,采取了較大的二進制碼流速率,這里取5.33kbps,,對應(yīng)K=3,。

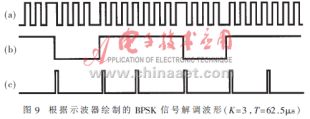

圖8中,上部為解調(diào)前的脈沖波形,,下部為解調(diào)出來的數(shù)據(jù)碼流,。圖8解調(diào)出的數(shù)據(jù)為100101,可以清楚地看出信號的對應(yīng)關(guān)系,。從圖8可以發(fā)現(xiàn),,輸入脈沖與解調(diào)碼流之間有信號滯后現(xiàn)象,且0,、1碼的碼元寬度也不完全一致,。但是,數(shù)據(jù)碼流與同步時鐘的關(guān)系卻始終是嚴格對應(yīng)的,。因為本設(shè)計中同步時鐘的脈沖寬度設(shè)為2μs,,相對信號的寬度來說太窄,無法通過示波器拍照來觀察,。筆者根據(jù)從示波器上的觀察,,繪制了解調(diào)前的脈沖波形與解調(diào)后的數(shù)據(jù)碼流及其同步時鐘的對應(yīng)關(guān)系,如圖9,。其中波形(a)為解調(diào)前的BPSK脈沖信號,,(b)為解調(diào)后的數(shù)據(jù)碼流Data,,(c)為同步時鐘Clock??梢悦黠@地看到,,同步時鐘不是等周期的,但是它與數(shù)據(jù)碼流的對應(yīng)關(guān)系是確定的,,因而不會影響到數(shù)據(jù)的正確解釋,。

本文提出了一種基于時間測量的BPSK信號的解調(diào)方法,并通過實際電路進行了驗證,。該電路已成功地用于實驗皮衛(wèi)星的低碼率BPSK指令信號的解調(diào)中,。本文方法結(jié)構(gòu)簡潔,系統(tǒng)開銷小,,解調(diào)參數(shù)T,、K調(diào)整方便(只需修改兩個中斷程序的相應(yīng)參數(shù)即可),是一種實用,、低成本的中低速BPSK解調(diào)方法,。如需對更高載頻的BPSK信號進行解調(diào),則可采用具有更短指令周期的單片機,,或采用CPLD,、FPGA硬件實現(xiàn)。

參考文獻

1 曹志剛,,錢亞生. 現(xiàn)代通信原理[M]. 北京:清華大學(xué)出版社,,1992

2 H.Leib,S.Pasupathy. The phase of a vector perturbed by Gaussian noise and differentially coherent receivers[J]. IEEE Trans. Inf. Theory,1988,;34(6):1491~1500

3 D.Divsalar,M.K.Simon. Multiple-symbol differential detection of MPSK[J]. IEEE Trans. Commu,,1990;38(3):300~308,

4 H.Leib,S.Pasupathy. Optimal noncoherent block demodulation of differential phase shift keying(DPSK)[J]. Archiv fur Elec-tronic and UbertragungstechniK(AEU),1991;45(5):299~305

5 F.Edbauer. Bit error rate of binary and quaternary DPSK signals with multiple differential feedback detection[J]. IEEE Trans. Commu,1992;40(3):457~460

6 Leib Harry.Data-aided noncoherent demodulation of DPSK [J]. IEEE Transactions on Communications,1995;43(2~4):722~725

7 Marschner Claudia,Rehfuss Sven,Peters Dagmar,et al.A novel circuit concept for PSK-demodulation in passive telemetric systems[J]. Microelectronics Journal,2002;33(1~2): 69~75

8 呂貴洲,,張馳,,譚業(yè)雙. 相移鍵控(PSK)信號軟件檢測的實現(xiàn)[J]. 現(xiàn)代電子技術(shù),2001;(11):53~55