摘 要: 一種基于嵌入式系統(tǒng)" title="嵌入式系統(tǒng)">嵌入式系統(tǒng)和Internet的FPGA動態(tài)配置方案。詳細介紹了該方案的設(shè)計思想,并給出了設(shè)計實例。與傳統(tǒng)的FPGA配置方案相比,該方案具有靈活、高效等突出優(yōu)勢。該方案的可行性和實用性已在實際系統(tǒng)中得到驗證。

關(guān)鍵詞: 嵌入式系統(tǒng) Internet? FPGA? TCP/IP? TFTP

在現(xiàn)今的數(shù)字系統(tǒng)" title="數(shù)字系統(tǒng)">數(shù)字系統(tǒng)設(shè)計中,以“微控制器" title="微控制器">微控制器" title="嵌入式微控制器" title="嵌入式微控制器">嵌入式微控制器">嵌入式微控制器+FPGA”為核心的體系結(jié)構(gòu)因其強大的處理能力和靈活的工作方式而被廣泛采用。嵌入式微控制器的優(yōu)勢在于將微處理器內(nèi)核與豐富多樣的外圍接口設(shè)備緊密結(jié)合,在提供強大的運算、控制功能的同時,降低了系統(tǒng)成本和功耗,因而適合作為數(shù)字系統(tǒng)的控制核心;FPGA的優(yōu)勢在于超高速、豐富的邏輯資源以及用戶可靈活配置的邏輯功能,適用于邏輯接口功能多種多樣、靈活可變的場合。將二者結(jié)合形成優(yōu)勢互補,如有需要,再配以適當?shù)膶S眯酒ɡ缫粢曨l編解碼器、數(shù)字調(diào)制解調(diào)器等)。這種體系結(jié)構(gòu)適用于大多數(shù)復(fù)雜數(shù)字系統(tǒng)的設(shè)計。

如系統(tǒng)中包含可編程器件,就必須考慮其功能配置的問題。然而,傳統(tǒng)的FPGA配置方案(例如調(diào)試階段的專用下載電纜方式、成品階段的專用存儲器方式)在成本、效率、靈活性等方面都存在著明顯的不足。針對這樣的實際問題,基于嵌入式微控制器與FPGA廣泛共存于復(fù)雜數(shù)字系統(tǒng)的背景,考慮到大量數(shù)字系統(tǒng)要求接入Internet的現(xiàn)狀,借鑒軟件無線電“一機多能”的思想,提出了一種基于嵌入式系統(tǒng)和Internet的FPGA動態(tài)配置方案。該方案的提出,旨在基于系統(tǒng)現(xiàn)有的、通用的軟硬件資源,盡可能地提高FPGA配置的效率和靈活性。實踐證明,該方案可行、實用,達到了設(shè)計目的。

1 FPGA配置的基本問題及現(xiàn)有的解決方案

為論述方便,將基于SRAM工藝的FPGA的配置流程用圖1所示的模型表示。從圖1中可以看到,F(xiàn)PGA的配置過程實質(zhì)上是兩次數(shù)據(jù)的傳輸過程(分別由配置數(shù)據(jù)源到時序控制器和由時序控制器到目標FPGA)。因此,將這兩次關(guān)鍵的數(shù)據(jù)傳輸作為FPGA配置的兩個基本問題,并在下文中針對不同的傳輸方式討論各自的優(yōu)缺點,從而尋求合理的解決方案。

傳統(tǒng)的配置方式包括應(yīng)用于調(diào)試階段的專用下載電纜方式和應(yīng)用于成品階段的專用非易失性存儲器" title="非易失性存儲器">非易失性存儲器方式。在這兩種方式中,上文所提到的兩次數(shù)據(jù)傳輸完全由FPGA廠商所提供的軟硬件完成。這樣的解決方案確實方便了一般的FPGA用戶,因為他們不必花費精力關(guān)心配置的細節(jié),但同時也不得不面對不少的缺陷:首先,專用下載電纜和專用非易失性存儲器的成本非常高,雖然用戶可以根據(jù)FPGA廠商提供的原理圖自制下載電纜,但專用非易失性存儲器是肯定無法自制的,而且有些不支持ISP(在系統(tǒng)可編程)的器件還必須配以合適的編程器,進一步增加了開發(fā)的成本;第二,常見的專用下載電纜都是使用計算機并口產(chǎn)生串行的配置信號,而以并口線作為傳輸媒介,注定其有效傳輸距離非常有限;第三,專用非易失性存儲器的配置方式?jīng)Q定了目標FPGA只能接收單一配置文件,即在系統(tǒng)運行過程中,F(xiàn)PGA不可能根據(jù)不同情況動態(tài)調(diào)整邏輯功能,這樣的設(shè)計無法滿足某些應(yīng)用中對于系統(tǒng)靈活性的要求。

針對上述各種缺陷,有人提出了改進方案,例如在系統(tǒng)中存在微控制器的前提下,用通用異步串口RS232替代專用的配置電纜、用通用的非易失性存儲器替代專用的非易失性存儲器。這些改進方案在一定程度上彌補了傳統(tǒng)配置方案的不足,但也存在一些新的缺陷:通用異步串口的傳輸速率很有限,無法滿足目前一些超大規(guī)模FPGA的配置要求;傳輸距離雖有明顯提高,但仍然無法滿足某些用戶對于遠程、跨區(qū)域的測試、維護和更新的需要。

2 基于嵌入式微控制器和Internet的解決方案

2.1 方案綜述

本設(shè)計的目標是基于系統(tǒng)中已有的軟硬件資源,盡可能提高FPGA配置的效率和靈活性。考慮到相當多的復(fù)雜數(shù)字系統(tǒng):(1)包含微控制器(具有多個通用I/O)及其程序存儲器;(2)具有接入Internet的能力(例如系統(tǒng)硬件中包含以太網(wǎng)接口,軟件中移植了TCP/IP協(xié)議),提出一種新的FPGA配置方案,如圖2所示。從圖2中可以看出,這種方案的實質(zhì)是將Internet作為傳輸配置數(shù)據(jù)的媒體,并用嵌入式微控制器的程序存儲器存儲這些數(shù)據(jù),從而完成第一節(jié)中提到的第一次數(shù)據(jù)傳輸;在嵌入式微控制器的通用I/O上實現(xiàn)FPGA配置時序,從而完成第二次數(shù)據(jù)傳輸。

為驗證這種方案的可行性和有效性,在船載自動識別系統(tǒng)(AIS)的設(shè)計中實現(xiàn)了該方案。相關(guān)的主要器件包括:CPU采用SAMSUNG公司的S3C44B0X;程序存儲器采用MACRONIX公司的MX29LV160ABTC;FPGA采用XILINX公司的XC2S200PQ208;以太網(wǎng)控制器采用REALTEK公司的RTL8019AS。上述器件均具有同類產(chǎn)品的一般特性,因而這一設(shè)計實例并不失驗證的一般性。

2.2 配置文件的傳輸協(xié)議TFTP

在方案的驗證實例中,使用基于UDP的TFTP協(xié)議在以太網(wǎng)內(nèi)傳輸配置文件,協(xié)議棧如圖3所示。由于UDP屬于不可靠的面向無連接的傳輸協(xié)議,因此在網(wǎng)絡(luò)結(jié)構(gòu)復(fù)雜的廣域網(wǎng)上傳輸FPGA配置數(shù)據(jù)并不適合采用TFTP協(xié)議,而必須采用可靠的、基于TCP的應(yīng)用層協(xié)議(例如FTP協(xié)議)。此處采用TFTP,完全是出于適應(yīng)AIS的運行環(huán)境、簡化性能測試的考慮,而且在應(yīng)用層實現(xiàn)了部分TCP的功能(例如偽連接、簡單的應(yīng)答和重發(fā)、數(shù)據(jù)包排序等功能),可以保證數(shù)據(jù)傳輸?shù)馁|(zhì)量。

標準的TFTP(Trivial File Transfer Protocol)是一種基于UDP的、簡單的文件傳輸協(xié)議。TFTP的設(shè)計目標是簡單小巧且易于實現(xiàn),因此遠不如采用多重并發(fā)TCP 連接的FTP功能強大(例如TFTP不支持目錄列表和用戶權(quán)限驗證,而且傳輸效率比較低)。

TFTP的基本通信過程為:客戶端向服務(wù)器發(fā)出讀或?qū)懻埱螅蝗绻?wù)器接收讀寫請求,正式的數(shù)據(jù)傳輸開始,每段數(shù)據(jù)長度固定為512字節(jié);長度小于512字節(jié)的數(shù)據(jù)段標志傳輸結(jié)束。此外,協(xié)議中還規(guī)定了超時、重發(fā)等異常處理機制。

在具體實現(xiàn)中,將TFTP服務(wù)器(待配置FPGA所在的目標系統(tǒng))設(shè)計成具有三個狀態(tài)的狀態(tài)機,其邏輯狀態(tài)轉(zhuǎn)移圖如圖4所示。PC機一端直接使用DOS下的TFTP命令。

2.3 FPGA配置文件及配置流程

用微控制器的通用I/O實現(xiàn)FPGA配置必須準確掌握:(1)配置文件的格式;(2)配置信號的時序。

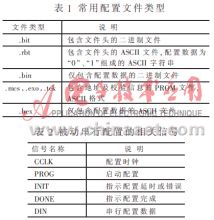

一般來說,F(xiàn)PGA開發(fā)軟件可以生成多種不同類型的配置文件,用戶可以根據(jù)不同的應(yīng)用環(huán)境選用這些配置文件。表1列舉了XILINX的ISE 6.2i可以生成的常用的配置文件類型及其說明。本設(shè)計采用.bin文件。值得注意的是,對于某一特定的芯片,無論設(shè)計簡單或是復(fù)雜,其配置數(shù)據(jù)的長度是固定的,但配置文件大小卻因類型的不同而有所差異。

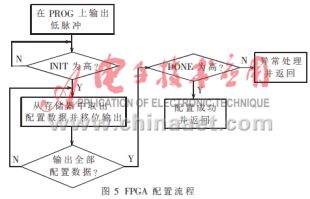

常見的FPGA配置模式包括主動串行模式、被動串行模式、被動并行模式和邊界掃描模式等。為與常見的下載電纜兼容并節(jié)約微控制器的I/O口線,本實例采用被動串行模式。相關(guān)的信號線如表2所示,圖5為配置子程序的流程圖。

將新的配置方案與已有的配置方案的各項指標列于表3。通過表3中的比較可以看出,基于微控制器和互聯(lián)網(wǎng)的配置方案在傳輸速率、傳輸距離上較其他方案均有明顯優(yōu)勢,同時又符合軟件無線電“一機多能”的設(shè)計思想,并能滿足某些用戶對于在線調(diào)試、更新和維護的需求。此外,必須看到,新方案在具備種種優(yōu)勢的同時,對用戶設(shè)計的軟硬件提出了一定的要求。事實上,完全具備這些軟硬件條件(例如移植TCP/IP協(xié)議、使用嵌入式微控制器)符合現(xiàn)今數(shù)字系統(tǒng)設(shè)計的趨勢,設(shè)計該配置方案的初衷正是基于這種設(shè)計理念,具有相當?shù)膶嵱眯浴?/P>

參考文獻

1 Mark Ng, Mike Peattie. Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode. 2002

2 K. Sollins. THE TFTP PROTOCOL (REVISION 2). 1992

3 ITU-R. Technical characteristics for a universal shipborne automatic identification system using time division multiple? access in the VHF maritime mobile baud. 2001

4 王田苗. 嵌入式系統(tǒng)設(shè)計與實例開發(fā)——基于ARM微處理器與μC/OS-II實時操作系統(tǒng).第二版.北京:清華大學(xué)出版社, 2003

5 Andrew S. Tanenbaum著. 熊桂喜,王小虎譯.計算機網(wǎng)絡(luò).第三版.北京:清華大學(xué)出版社,1998

6 楊小牛,樓才義,徐建良. 軟件無線電原理與應(yīng)用.北京:電子工業(yè)出版社, 2001