本文主要介紹MAX1032" title="MAX1032">MAX1032采樣芯片以及使用CPLD" title="CPLD">CPLD對MAX1032采樣進行控制的方法。事實上,雖然微控制器也能對MAX1032進行方便的控制,但使用CPLD來控制系統(tǒng)外圍設備,可以節(jié)省微控制器的資源,減輕其負擔,同時可以讓其處理更復雜的信息,而利用CPLD對時序進行控制則更精確。

1 MAX1032的主要功能

MAX1032是美信公司推出的AD采樣芯片MAX1030-MAX1033系列中一款。該系列是采樣范圍可達±12 V的多量程、低功耗、14位逐次逼近型串行輸出模數(shù)轉(zhuǎn)換器(ADC),數(shù)據(jù)傳輸符合SPI協(xié)議。當采用+5 V單電源供電時,其轉(zhuǎn)換速率高達115 ksps。

MAX1032內(nèi)部主要由模擬輸入復用器及多通道電路、控制邏輯和寄存器、可編程增益放大器(PGA)逐次逼近數(shù)模轉(zhuǎn)換器(SAR ADC)、串行I/O(Serial I/O)以及先進先出寄存器(FIFO)等主要模塊構(gòu)成。

MAX1032的各引腳功能如下:

CH0~CH7:模擬信號輸入端。單端輸入范圍為:O~+6 V、-6 V~0、0~+12 V、-12 V~0和±3V;

±6 V,±12 V,差分輸入,范圍為:±6 V、±12V和±24V;

![]() :片選輸入,低電平有效。只有該端置低,數(shù)據(jù)才可同步輸入(DIN)或輸出(DOUT);

:片選輸入,低電平有效。只有該端置低,數(shù)據(jù)才可同步輸入(DIN)或輸出(DOUT);

DIN:串行數(shù)據(jù)輸入。![]() 為低時,DIN上的數(shù)據(jù)在SCLK的上升沿輸入片內(nèi);

為低時,DIN上的數(shù)據(jù)在SCLK的上升沿輸入片內(nèi);

SSTRB:串行觸發(fā)輸出。在內(nèi)部時鐘模式下,SSTRB的上升沿跳變表明轉(zhuǎn)換完成;在外部時鐘模式下,SSTRB一直為低電平;

SCLK:串行時鐘輸入;

DOUT:串行數(shù)據(jù)輸出。在![]() 為低時,DOUT上的數(shù)據(jù)在SCLK的下降沿輸出;

為低時,DOUT上的數(shù)據(jù)在SCLK的下降沿輸出;![]() 置高時,DOUT為高阻狀態(tài);

置高時,DOUT為高阻狀態(tài);

REFCAP:參考電壓旁路端。對于外部參考電壓模式。REFCAP連到AVDD;對于內(nèi)部參考電壓模式,通過一個0.01μf的電容連到AGNDl;

REF:內(nèi)部基準電壓輸出或外部基準電壓輸入。在外部參考電壓模式下,REF端可接由外部電路提供的3.800-4.0136 V的基準電壓;在內(nèi)部參考電壓模式下。REF端與AGNDl端之間必須連接容量為1μF的濾波電容,該端由芯片內(nèi)部提供4.096 V參考電壓:

DGNDO:數(shù)字I/O地;

DGND:數(shù)字地;

DVDDO:數(shù)字I/O電源輸入。輸入范圍為+2.7~+5.25 V:

DVDD:數(shù)字電源輸入;

AVDDl:模擬輸入電源1,輸入范圍為+4.75~+5.25 V:

AVDD2:模擬輸入電源2,輸入范圍為+4.75~+5.25 V:

AGNDl:模擬地1;

AGND2:模擬地2;

AGND3:模擬地3。

設計時,AGNDl,AGND2,AGND3,DGNDO,DGND必須接到一起。

2 MAX1032的工作原理

在使用MAX1032進行采樣前,通常需要確認信號的輸入阻抗在17 kΩ以內(nèi)。

MAX1032總共有三種工作模式:外部時鐘模式,外部采樣模式和內(nèi)部時鐘模式。本文將針對。MAX1032的外部時鐘模式并結(jié)合CPLD給出實際的應用方案。

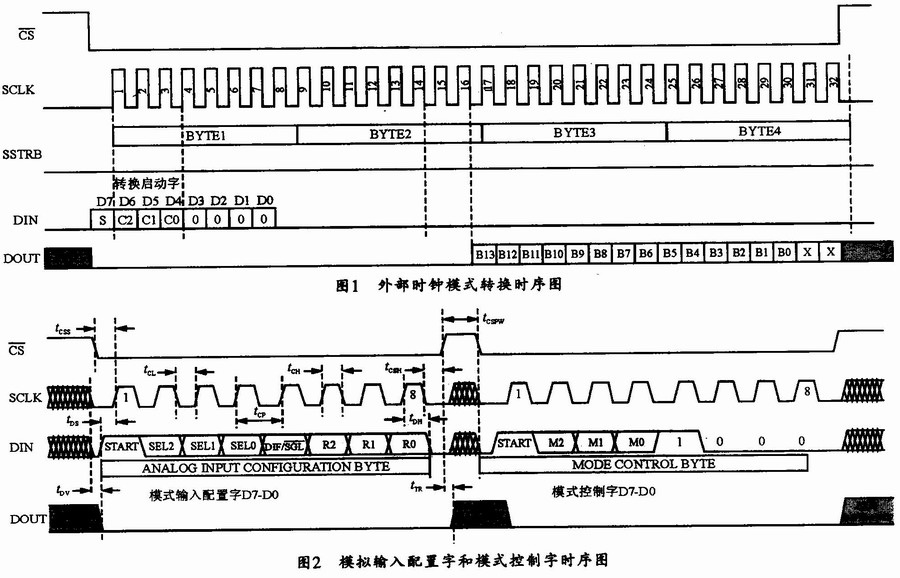

外部時鐘模式:以最快的轉(zhuǎn)換速率達到最大的吞吐量,由用戶直接控制采樣時,CSn在轉(zhuǎn)換過程中始終為低,這時,用戶可通過SCLK控制A/D的轉(zhuǎn)換并對結(jié)果讀取。SSTRB始終為低,其轉(zhuǎn)換時序圖如圖1所示。SCLK的周期(tCP)必須在272 ns~62 us之間。其中高低電平寬度均需大于109 ns(tCL,tCH)。在CSn由高變低后的40 ns(tCSS),可以開始對SCLK上跳沿計數(shù),DIN的輸入建立時間至少40 ns (tDS),DIN將在SCLK上跳沿時同步輸入(tDH),SCLK上跳沿之后,將忽略DIN。在CSn變低之后40 ns(tDV)內(nèi),DOUT開始有效,而在CSn拉高后40 ns(tTR)內(nèi),DOUT將輸出保持高阻態(tài),其時序描述如圖2所示。

在內(nèi)部時鐘模式,系統(tǒng)將以較快的速率達到最大的吞吐量,并由內(nèi)部時鐘控制采樣,用戶只需提供一個字節(jié)的SCLK,再拉高CSn,即可啟動轉(zhuǎn)換。和外部采樣模式相同,SSTRB上跳變表示轉(zhuǎn)換完成,此時,用戶便可提供兩個字節(jié)的SCLK來讀取轉(zhuǎn)換結(jié)果。

在外部采樣模式,系統(tǒng)將以最慢的轉(zhuǎn)換速率達到最大的吞吐量,并由用戶直接控制采樣,用戶可提供兩個字節(jié)的SCLK,再將CSn拉高,以啟動轉(zhuǎn)換。SSTRB上跳變表示轉(zhuǎn)換完成,用戶提供兩個字節(jié)的SCLK可讀取轉(zhuǎn)換結(jié)果。

MAX1032總共有三個控制字:模擬輸入配置字、模式控制字和轉(zhuǎn)換啟動字。圖2所示是模擬輸入控制字和模式控制字的工作時序圖。三個控制字均為8位。

對于模擬輸入配置字,DO~D2是選擇量程的,MAX1032總共有10種量程可以選擇;D3是差分/單端選擇位,為低表示采樣信號為單端輸入.為高表示差分輸入。D4~D6是輸入通道選擇,總共有8個采樣通道。D7是字開始位,置高表示字輸入開始。

對于模式控制字,D0~D2必須為低,D3必須為高。D4~D6用于工作狀態(tài)選擇,總共有6種工作狀態(tài)。D7是字開始位,同樣,置高表示字輸入啟動。

轉(zhuǎn)換啟動字D7是字開始位,D4~D2是輸入通道選擇。用法和模擬輸入配置字相同,操作時DO~D3必須為低。

三個控制字的輸入順序是模擬輸入配置字,模式控制字,轉(zhuǎn)換啟動字。

3 硬件設計

圖3所示是本系統(tǒng)的結(jié)構(gòu)框圖。由圖3可見,模擬采樣信號先經(jīng)過一個運放。運放的作用是降低輸入阻抗。以達到MAX1032輸入阻抗小于17kΩ的要求。之后,再將利用CPLD控制MAX1032進行采樣,采樣結(jié)果回送至CPLD,之后經(jīng)過處理后的數(shù)據(jù)傳到系統(tǒng),由系統(tǒng)再將一系列二進制數(shù)換算成最終的結(jié)果。框圖里的系統(tǒng)可以是嵌入式微控制器,也可以是數(shù)字輸入輸出卡等控制系統(tǒng)。

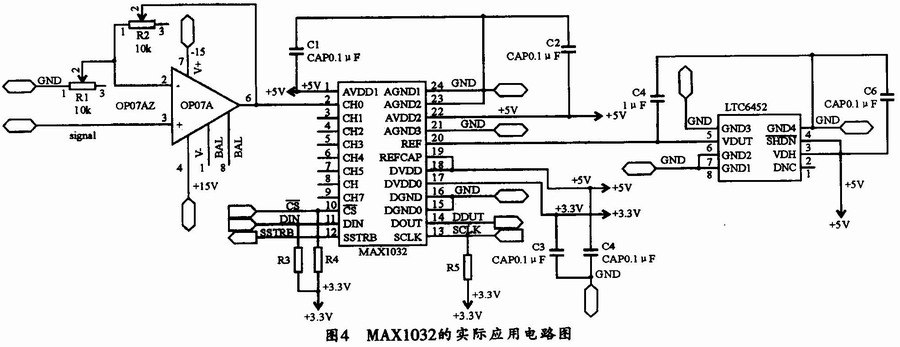

圖4所示是MAX1032的應用電路圖。由于MAX1032只允許輸入阻抗小于17 kΩ,而有的采樣信號不一定能滿足這一要求,故需要對采樣信

號進行一定處理,以降低信號的輸出阻抗。由于射極跟隨器的輸出阻抗趨于零,故將待采樣信號連到射極跟隨器上可以有效降低其輸出阻抗。本文選用的運放為OP07,該運放具有很低的輸入失調(diào)電壓和漂移,而且精度相當高,適合作為模擬信號前置運放。如將OP07接成負反饋模式,使輸出等于1+R1/R2,并將滑動變阻器R1調(diào)至0Ω,那么它就可以當做電壓跟隨器使用。

圖4中,MAX1032的外部參考電壓由LTC6652提供。LTC6652是高精度電位參考芯片,本文使用4.096 V作為MAX1032外部參考電壓。REFCAP在此模式下可接到5 V電源。由于MAX1032是由CPLD控制,故將DVDDO連到3.3 V。

4 CPLD邏輯設計

CPLD和MAX1032的連接圖如圖5所示。其中,CPLD可以選用Ahera公司的MAXII系列器件EPM240或EPM570。

CPID的程序設計主要由兩部分組成,第一部分是產(chǎn)生MAX1032的控制信號,第二部分是對MAX1032的輸出結(jié)果進行處理。

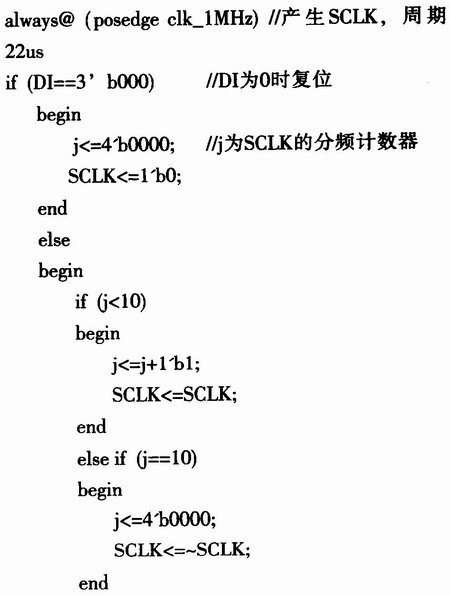

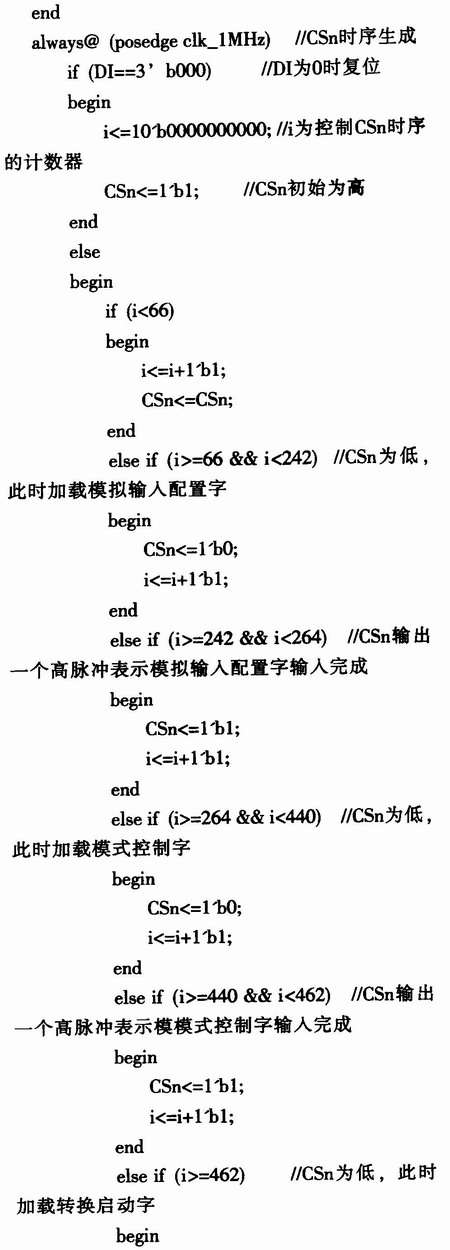

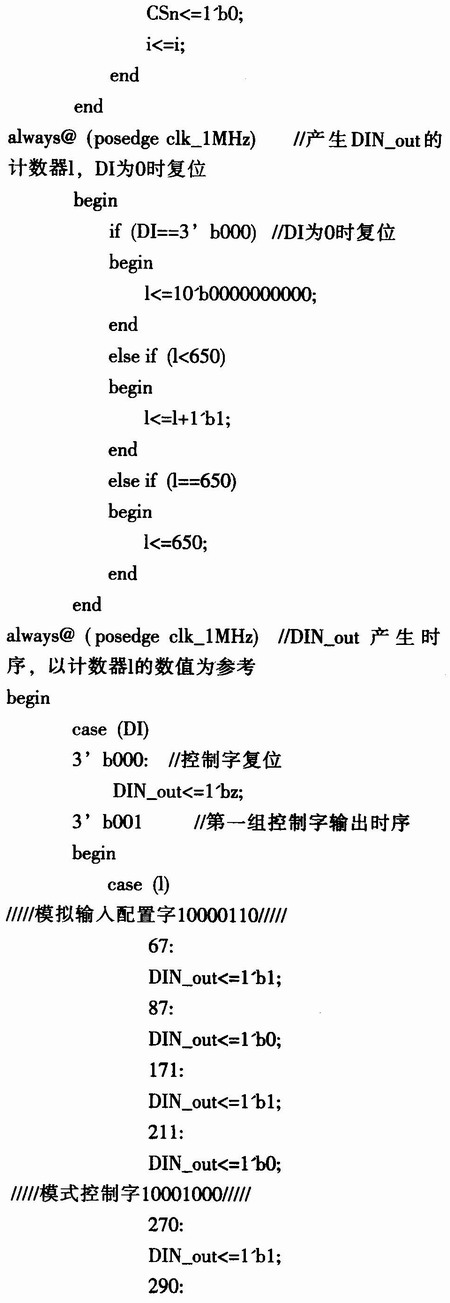

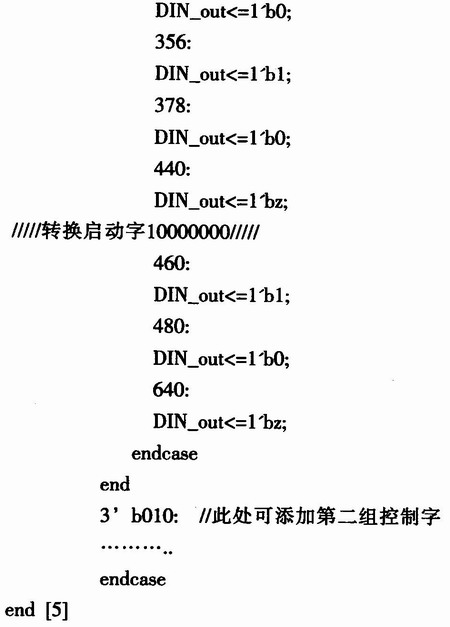

clk_1MHZ為CPLD時鐘,選1 MHz。通過CPLD可在內(nèi)部對時鐘進行分頻,輸出SCLK可作為MAX1032的輸入時鐘。DI由系統(tǒng)給CPLD輸入,作用是選擇MAX1032的控制字,同時也是CPLD的復位控制。DIN_out是給MAX1032加載的串行控制字,其加載時序可利用計數(shù)器控制。本例采用外部時鐘模式,模擬輸入配置字為10000110。第七位1是字開始標志;六到四位為0表示選擇CH0通道輸入,第三位為0表示采樣信號單端輸入;二到零位為110,表示量程選擇0~12 V。模式控制字為10001000,第七位1是字開始標志,六到四位為0表示使用外部時鐘模式。三到零位為100 0是芯片強制輸入。加載完模擬輸入配置字和模式控制字之后,就可以啟動采樣,以加載轉(zhuǎn)換啟動字開始采樣。轉(zhuǎn)換啟動字為10000000時,第七位1是字開始標志,六到四位為0表示選擇CH0通道輸入,三到零位為0000是芯片強制輸入。MAX1032控制協(xié)議和SPI類似,在SCLK的上跳沿輸入,下跳沿輸出。片選信號CSn時序利用計數(shù)器控制,每個控制字之間的CSn必須有一個高脈沖,脈寬至少40 ns(tCSPW),每個控制字輸入完后,CSn可以立即拉高(tCSH)。以下是可綜合的MAX1032控制程序的主要代碼:

圖6所示是Modelsim的仿真波形。SCLK上跳沿DIN_out的數(shù)據(jù)被MAX1032讀取。

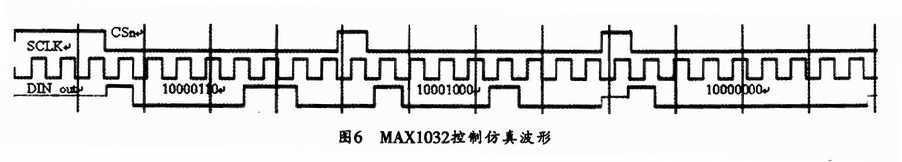

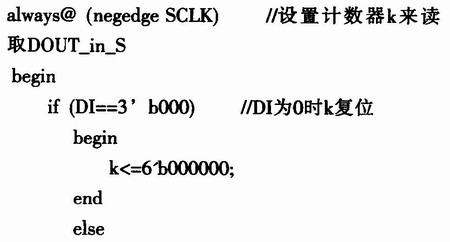

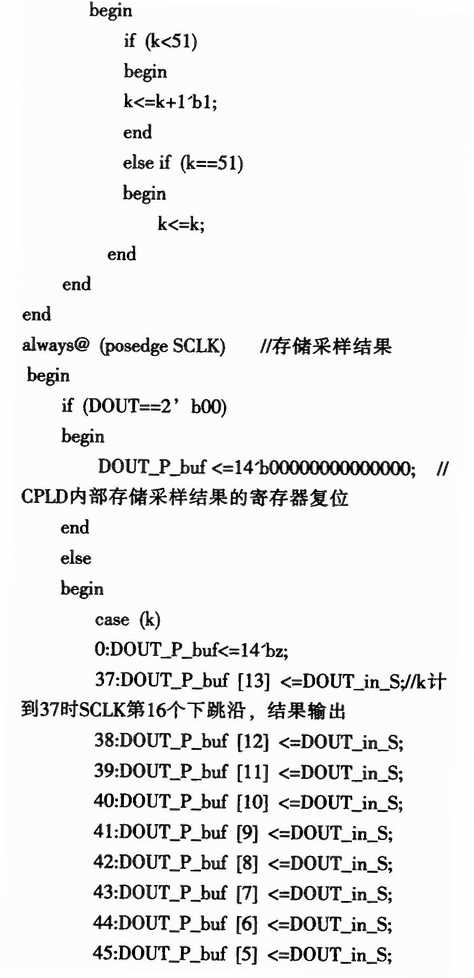

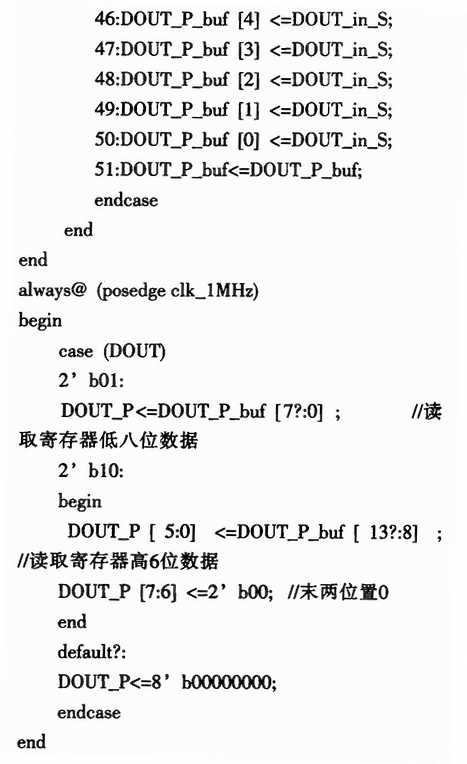

程序的第二部分的作用是將MAX1032輸出的串行采樣結(jié)果存入CPLD內(nèi)部的一個14位寄存器。采樣結(jié)果DOUT_in_S是14位的串行序列。CPLD在SCLK的上跳沿讀取數(shù)據(jù)后,可將其存到一個內(nèi)部寄存器,再由DOUT選擇輸出寄存器的高或低八位數(shù)據(jù)讀出。最后的采樣結(jié)果是并行輸出的。總共2個字節(jié),末兩位數(shù)據(jù)無效。對于外部時鐘模式,可從加載轉(zhuǎn)換啟動字開始計算,在第16個SCLK下跳沿,芯片將輸入采樣結(jié)果。得到結(jié)果即可按照公式(采樣電壓=12x(轉(zhuǎn)換成十進制的輸出結(jié)果)/16384)進行計算。以下是這部分功能的可綜合代碼:

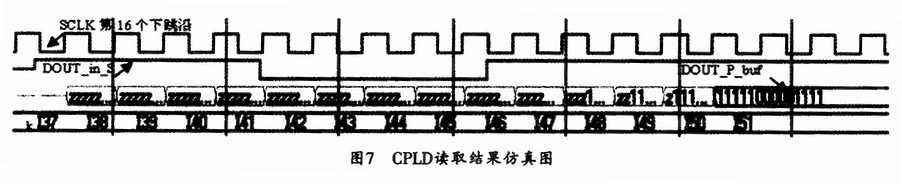

圖7所示是Moddsim仿真的CPLD讀取MAX1032的采樣結(jié)果并將其存入寄存器DOUT_P_buf的仿真圖。由圖可見,在啟動采樣后的第16個SCLK的下跳沿,MAX1032輸出14位串行采樣結(jié)果,CPLD將其存入內(nèi)部寄存器中以待系統(tǒng)讀取。一般在下一次采樣之前,需要將CPLD復位來清除上一次采樣的數(shù)據(jù)。由于外部時鐘模式下的SSTRB始終為低,故本例沒有對該信號進行處理。

5 結(jié)束語

本文介紹了利用CPLD控制MAX1032進行采樣的實現(xiàn)方法,包括CPLD的內(nèi)部邏輯設計和對采樣信號的處理等。實驗證明,該方法能夠適用

需要使用CPLD控制外圍電路的場合。