許多市場對高效率同相DC-DC轉(zhuǎn)換器的需求都在不斷增長,這些轉(zhuǎn)換器能以降壓或升壓模式工作,即可以將輸入電壓降低或提高至所需的穩(wěn)定電壓,并且具有最低的成本和最少的元件數(shù)量。反相SEPIC(單端初級電感轉(zhuǎn)換器)也稱為Zeta轉(zhuǎn)換器,具有許多支持此功能的特性(圖1)。對其工作原理及利用雙通道同步開關(guān)控制器ADP1877的實施方案進(jìn)行分析,可以了解其在本應(yīng)用中的有用特性。

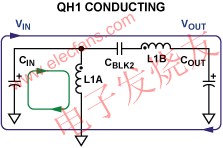

拓?fù)浣Y(jié)構(gòu) www.elecfans.com" border="0" hspace="0" src="http://files.chinaaet.com/images/20101102/cea81833-d8e0-4aa4-b6ad-d12dc58af0a2.jpg" style="filter: ; width: 236px; zoom: 1; height: 94px" />

圖1. 反相SEPIC拓?fù)浣Y(jié)構(gòu)

初級開關(guān)QH1和次級開關(guān)QL1反相工作。在導(dǎo)通時間內(nèi),QH1接通,QL1斷開。電流沿兩條路徑流動,如圖2所示。第一條路徑是從輸入端經(jīng)過初級開關(guān)、能量傳輸電容(CBLK2)、輸出電感(L1B)和負(fù)載,最終通過地流回輸入端。第二條路徑是從輸入端經(jīng)過初級開關(guān)、地基準(zhǔn)電感(L1A)和地流回輸入端。

圖2. 電流流向圖;QH1閉合,QL1斷開

在關(guān)斷期間,開關(guān)位置剛好相反。QL1接通,QH1斷開。輸入電容(CIN)斷開,但電流繼續(xù)經(jīng)過電感沿兩條路徑流動,如圖3所示。第一條路徑是從輸出電感經(jīng)過負(fù)載、地和次級開關(guān)流回輸出電感。第二條路徑是從地基準(zhǔn)電感經(jīng)過能量傳輸電容、次級開關(guān)流回地基準(zhǔn)電感。

圖3. 能量傳輸圖;QL1閉合,QH1斷開

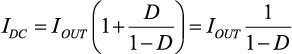

應(yīng)用電感伏秒平衡原理和電容電荷平衡原理,可以求得方程式1所規(guī)定的均衡直流轉(zhuǎn)換比,其中D為轉(zhuǎn)換器的占空比(一個周期的導(dǎo)通時間部分)。

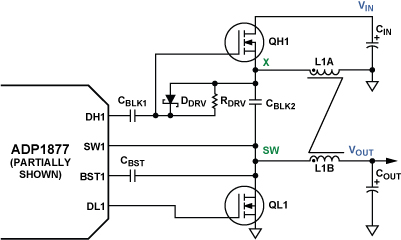

|

(1) |

上式表明:如果占空比大于0.5,輸出端將獲得較高的調(diào)節(jié)電壓(升壓);如果占空比小于0.5,調(diào)節(jié)電壓會較低(降壓)。此外還可分析得到其它相關(guān)結(jié)果:在無損系統(tǒng)中,能量傳輸電容(CBLK2)上的穩(wěn)態(tài)電壓等于VOUT;流經(jīng)輸出電感(L1B)的直流電流值等于IOUT;流經(jīng)地基準(zhǔn)電感(L1A)的直流電流值等于IOUT × VOUT/VIN。該能量傳輸電容還能提供VIN至VOUT的隔直。當(dāng)存在輸出短路風(fēng)險時,此特性很有用。

分析還顯示,反相SEPIC中的輸出電流是連續(xù)的,對于給定輸出電容阻抗,會產(chǎn)生較低的峰峰值輸出電壓紋波。這就允許使用較小、較便宜的輸出電容;相比之下,在非連續(xù)輸出電流拓?fù)浣Y(jié)構(gòu)中,為了達(dá)到同樣的紋波要求,需要使用較大且昂貴的電容。

通常,次級開關(guān)(QL1)是一個單向功率二極管,它會限制這種拓?fù)浣Y(jié)構(gòu)的峰值效率。然而,利用ADI公司雙通道同步開關(guān)控制器ADP1877(見附錄)的一個通道,并采用雙向MOSFET作為次級開關(guān),可以設(shè)計一個“完全同步配置”的反相SEPIC。這樣,峰值效率將大大提高,同時可以降低輸出電流大于1 A的轉(zhuǎn)換器尺寸和成本。

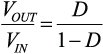

圖4顯示完全同步反相SEPIC配置的功率級,它利用ADP1877實現(xiàn),只需要三個小型、廉價的額外器件(CBLK1、DDRV和RDRV),其功耗可以忽略不計。

圖4. 同步反相SEPIC的功率級,利用ADP1877的通道1實現(xiàn)

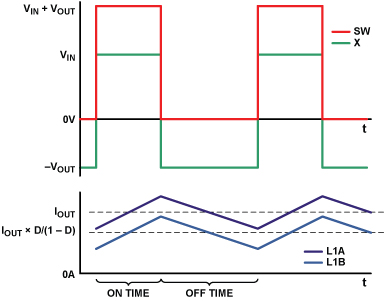

反相SEPIC的理想穩(wěn)態(tài)波形如圖5所示。通道1開關(guān)節(jié)點SW1(見附錄圖A)在VIN + VOUT (導(dǎo)通時間內(nèi))和0 V(關(guān)斷時間內(nèi))之間切換。將電荷泵電容CBST, 連接到SW1,以便在導(dǎo)通時間內(nèi)將約為VIN + VOUT + 5 V的電壓施加于高端內(nèi)部驅(qū)動器的自舉上電軌(BST1引腳)和高端驅(qū)動器的輸出(DH1引腳),從而增強初級浮空N溝道MOSFET開關(guān)QH1。箝位二極管DDRV, 確保穩(wěn)態(tài)輸出期間CBLK1上的電壓約為VOUT + VFWD(DDRV),該電壓參考ADP1877的DH1引腳到QH1柵極的電壓。在關(guān)斷時間內(nèi),當(dāng)X節(jié)點電壓約為–VOUT時,CBLK1上的電壓阻止初級開關(guān)產(chǎn)生高于其閾值的柵極-源極電壓。

圖5. 同步反相SEPIC的理想波形(忽略死區(qū))

ADP1877具有脈沖跳躍模式,使能時,可以降低開關(guān)速率,只向輸出端提供足以保持輸出電壓穩(wěn)定的能量,從而提高小負(fù)載時的效率,大大降低柵極電荷和開關(guān)損耗。在同步反相SEPIC和同步降壓拓?fù)浣Y(jié)構(gòu)中均可以使能此模式。圖4所示DC-DC轉(zhuǎn)換電路只需要雙通道ADP1877的一個通道,因此另一通道可以用于任一種拓?fù)浣Y(jié)構(gòu)。

電感耦合和能量傳輸電容

圖4中,功率電感L1A和L1B顯示為彼此耦合。在這種拓?fù)浣Y(jié)構(gòu)中,耦合電感的目的是減少輸出電壓和電感電流的紋波,并且提高最大可能閉環(huán)帶寬,下一部分將對此加以說明。

雖然這些電感互相耦合,但并不希望耦合太緊,以至于將一個繞組的大量能量通過鐵芯傳輸至另一個繞組。為了避免這一點,必須求得耦合電感的泄漏電感(LLKG),并選擇適當(dāng)?shù)哪芰總鬏旊娙?CBLK2),使得其復(fù)數(shù)阻抗的幅值為泄漏電感與單個繞組電阻(DCR)的復(fù)串聯(lián)阻抗的1/10,如方程式2、3、4所示。按照這一關(guān)系設(shè)計電路,可使耦合鐵芯所傳輸?shù)哪芰拷抵磷畹汀P孤╇姼锌梢愿鶕?jù)耦合電感數(shù)據(jù)手冊中提供的耦合系數(shù)計算。

|

(2) |

|

|

(3) |

|

(4) |

匝數(shù)比最好為1:1,因為對于給定水平的輸出電壓紋波,此時各繞組只需要分立電感所需電感的一半1。可以使用1:1以外的匝數(shù)比,但其結(jié)果將無法用本文中的方程式準(zhǔn)確描述。

小信號分析和環(huán)路補償

反相SEPIC轉(zhuǎn)換器的完整小信號分析超出了本文的范圍,不過,如果遵照下述原則,完整分析將更具學(xué)術(shù)意義。

首先必須計算諧振頻率(fRES)時的許多復(fù)數(shù)阻抗交互,以便求得目標(biāo)交越頻率的上限。當(dāng)電感解耦時,此頻率降低,導(dǎo)致最大可能閉環(huán)帶寬顯著降低。

|

(5) |

在此頻率時,可能有300°或更大的“高Q”相位遲滯。為了避免轉(zhuǎn)換器在整個負(fù)載范圍內(nèi)相位裕量偏小的問題,目標(biāo)交越頻率(fUNITY)應(yīng)為fRES的1/10。此諧振的阻尼主要取決于輸出負(fù)載電阻和耦合電感的直流電阻。在較小程度上,阻尼還取決于能量傳輸電容的等效串聯(lián)電阻(ESR)和功率MOSFET(QHl和QL1)的導(dǎo)通電阻。因此,當(dāng)輸出負(fù)載電阻改變時,閉環(huán)傳遞函數(shù)的特征在該頻率時發(fā)生明顯變化也不足為奇。

耦合系數(shù)通常不是一個能夠精確控制的參數(shù),因此應(yīng)將目標(biāo)交越頻率設(shè)置為比fRES低10倍的值(假設(shè)fRES小于開關(guān)頻率fSW)。當(dāng)fUNITY設(shè)置適當(dāng)時,可以使用標(biāo)準(zhǔn)“II型”補償——兩個極點和一個零點。

|

(6) |

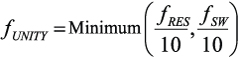

圖6顯示同步反相SEPIC降壓/升壓拓?fù)浣Y(jié)構(gòu)中ADP1877反饋環(huán)路的等效電路。上框包含功率級和電流環(huán)路,下框包含電壓反饋環(huán)路和補償電路。

圖6. 同步反相SEPIC拓?fù)浣Y(jié)構(gòu)中ADP1877具有內(nèi)部電流檢測I環(huán)路的功率級和補償方案

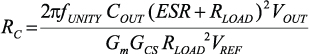

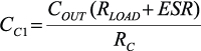

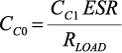

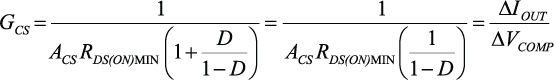

下框中的補償元件值可以通過下式計算:

|

(7) |

|

(8) |

|

(9) |

轉(zhuǎn)換器的跨導(dǎo)GCS利用下式計算:

|

(10) |

COUT 是轉(zhuǎn)換器的輸出電容。ESR是該輸出電容的等效串聯(lián)電阻。RLOAD是最小輸出負(fù)載電阻。ACS是電流檢測增益,對于ADP1877,它可以在3 V/V至24 V/V范圍內(nèi)以離散步進(jìn)選擇。Gm是誤差放大器的跨導(dǎo),ADP1877為550 μs。VREF 是與誤差放大器的正輸入端相連的基準(zhǔn)電壓,ADP1877為0.6 V。

GCS 是與頻率無關(guān)的增益項,隨增強后的次級開關(guān)電阻RDS(ON)而變化。最高交越頻率預(yù)期出現(xiàn)在此電阻和占空比D最低時。

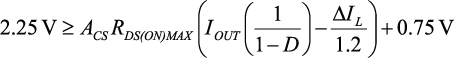

為確保在最大輸出電流時不會達(dá)到補償箝位電壓,所選的電流檢測增益(ACS)最高值應(yīng)滿足以下條件:

|

(11) |

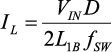

其中?IL 為峰峰值電感紋波電流。

|

(12) |

如果斜率補償過多,此處的方程式精確度將會下降:直流增益將降低,輸出濾波器將引起主極點的頻率位置提高。

斜率補償

對于利用ADP1877實現(xiàn)的同步反相SEPIC,必須考慮電流模式控制器2中的次諧波振蕩現(xiàn)象。

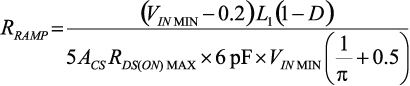

按照下式設(shè)置RRAMP ,可以將采樣極點的品質(zhì)因素設(shè)為1,從而防止發(fā)生次諧波振蕩3 (假設(shè) fUNITY 設(shè)置適當(dāng))。

|

(13) |

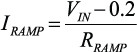

值得注意的是,隨著增強后的次級開關(guān)電阻RDS(ON)降低,采樣極點的Q也會下降。如果這一因素與其它相關(guān)容差一起導(dǎo)致Q小于0.25,則應(yīng)進(jìn)行仿真,確保在考慮容差的情況下,轉(zhuǎn)換器不會有過多斜率補償,并且不是太偏向于電壓模式。RRAMP 的值必須使得ADP1877 RAMP引腳的電流在6 μA至200 μA范圍內(nèi),其計算公式14如下:

|

(14) |

功率器件應(yīng)力

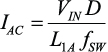

從圖2和圖3的電流流向圖可以看出,功率MOSFET在接通后要承載電感電流總和。因此,流經(jīng)兩個開關(guān)的電流直流分量為:

|

(15) |

如果電感的耦合比為1:1,則流經(jīng)兩個開關(guān)的電流交流分量為:

|

(16) |

知道這些值后,可以很快算出流經(jīng)各開關(guān)的電流均方根值。這些值與所選MOSFET的RDS(ON)MAX共同確保MOSFET具有熱穩(wěn)定性,同時功耗足夠低,以滿足效率要求。

圖7. 同步反相SEPIC的理想電流波形(忽略死區(qū))

精確計算初級開關(guān)的開關(guān)損耗超出了本文的范圍,但應(yīng)注意,從高阻態(tài)變?yōu)榈妥钁B(tài)時,MOSFET上的電壓擺輻約為~VIN + VOUT 至 ~0 V,流經(jīng)開關(guān)的電流擺輻為0 A至IOUT[1/(1 – D)]。由于擺幅如此之高,開關(guān)損耗可能是主要損耗,這是挑選MOSFET時應(yīng)注意的一點;對于MOSFET,反向傳輸電容((CRSS)與RDS(ON)成反比。

初級開關(guān)和次級開關(guān)的漏極-源極擊穿電壓(BVDSS均須大于輸入電壓與輸出電壓之和(見圖5)。

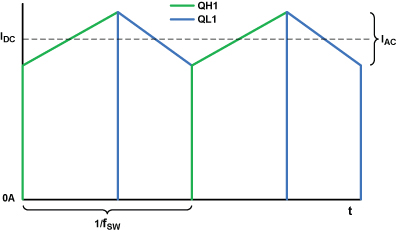

峰峰值輸出電壓紋波(?VRIPPLE)可通過下式近似計算:

|

(17) |

流經(jīng)輸出電容的電流均方根值 (I rms COUT) 為:

|

(18) |

方程式12所表示的峰峰值電感電流(?IL)取決于輸入電壓,因此必須確保當(dāng)此參數(shù)改變時,輸出電壓紋波不會超過規(guī)定值,并且流經(jīng)輸出電容的均方根電流不會超過其額定值。

對于利用ADP1877實現(xiàn)的同步反向SEPIC,輸入電壓與輸出電壓之和不得超過14.5 V,因為電荷泵電容與開關(guān)節(jié)點相連,當(dāng)初級開關(guān)接通時,其電壓達(dá)到VIN + VOUT。

實驗室結(jié)果

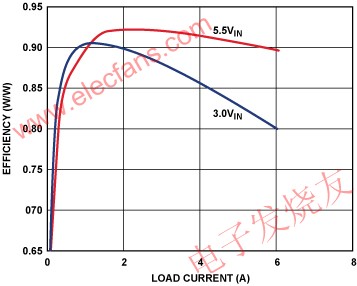

圖8顯示5 V輸出、3 V和5.5 V輸入時同步反向SEPIC的功效與負(fù)載電流的關(guān)系。對于需要在3.3 V和5.0 V輸入軌之間切換的應(yīng)用,或者當(dāng)實時調(diào)整輸入電壓以優(yōu)化系統(tǒng)效率時,這是常見情況。采用1 A至2 A負(fù)載時,無論輸入電壓高于或低于輸出電壓,轉(zhuǎn)換器的效率均超過90%。

圖8. 效率與負(fù)載電流的關(guān)系

與圖8相關(guān)的功率器件材料清單見表1,其中僅采用常見的現(xiàn)成器件。一項具可比性的異步設(shè)計采用一個具有低正向壓降的業(yè)界領(lǐng)先肖特基二極管代替QL1,在以上兩種輸入電壓下,其滿載時的效率低近10%。此外,異步設(shè)計尺寸更大、成本更高,而且可能需要昂貴的散熱器。

表1. 功率器件

| 標(biāo)志符 | 產(chǎn)品型號 | 制造廠商 | 值 | 封裝 | 備注 |

| QH1/QL1 | FDS6572A | Fairchild Semiconductor | 20 BVDSS | SO8 | 功率 MOSFET/6 mΩ (最大值) @ 4.5 Vgs @ 25°C Tj |

| L1A/B | PCA20EFD-U10S002 | TDK | 每個繞組3.4 µH | 30 mm × 22 mm × 12 mm | 1:1:1:1:1:1 耦合電感/鐵氧體/每個繞組35.8 mΩ (最大值) DCR |