摘 要: 線性調(diào)頻信號可以獲得較大的壓縮比,有著良好的距離分辨率和徑向速度分辨率,是目前雷達信號采用的主要形式。詳述了如何利用TI公司的TMS320C6701 DSP實現(xiàn)線性調(diào)頻信號的頻域" title="頻域">頻域數(shù)字脈沖壓縮" title="脈沖壓縮">脈沖壓縮,給出了系統(tǒng)的實現(xiàn)框圖和脈壓結(jié)果。

關(guān)鍵詞: 浮點DSP 數(shù)字脈沖壓縮 頻域處理 時域處理

線性調(diào)頻信號具有拋物線式的非線性相位譜,能夠獲得較大的時寬帶寬積;與其它脈壓信號相比,很容易用數(shù)字技術(shù)產(chǎn)生,且技術(shù)上比較成熟;所用的匹配濾波器對回波信號的多卜勒頻移不敏感,因而可以用一個匹配濾波器處理具有不同多卜勒頻移的回波信號。這將大大簡化信號處理系統(tǒng),因此它在工程中得到了廣泛的應用。采用這種信號的雷達可以同時獲得遠的作用距離和高的距離分辨率。數(shù)字化的脈沖壓縮系統(tǒng)具有性能穩(wěn)定、受干擾小、工作方式靈活多樣等優(yōu)點,是現(xiàn)代脈壓系統(tǒng)的發(fā)展趨勢。

本文以TI公司的高性能的TMS320C6701浮點DSP芯片作為實現(xiàn)數(shù)字脈沖壓縮的核心器件,實現(xiàn)了線性調(diào)頻信號的頻域數(shù)字脈沖壓縮。

1 數(shù)字脈沖壓縮原理

數(shù)字脈沖壓縮采用數(shù)字信號處理技術(shù)完成相關(guān)匹配濾波,通常采用時域處理和頻域處理兩種方法實現(xiàn)這一過程。

1.1 時域脈沖壓縮處理

時域脈沖壓縮直接對雷達回波信號進行卷積運算,如圖1所示。其算式如下:

式中,s(n)為A/D采樣之后的回波信號;h(n)為匹配濾波器的沖激響應信號;y(n)為時域脈壓輸出信號。采用時域方法進行脈沖壓縮且當卷積運算速度達到A/D采樣速度時,可以進行實時脈沖壓縮處理,輸入信號的長度不受濾波器階數(shù)的限制。但當A/D采樣頻率較高時,脈壓處理將無法實時完成。

1.2 頻域脈沖壓縮" title="頻域脈沖壓縮">頻域脈沖壓縮處理

頻域脈沖壓縮先對輸入回波序列進行FFT 變換,將離散輸入時間序列變換成離散譜,然后乘以匹配濾波器沖擊響應的離散譜,再用逆FFT 還原成壓縮后的時間離散信號,如圖2所示。其算式如下:

在大時寬信號時,采用高速FFT算法,大大減少了運算量,提高了運算速度, 因而現(xiàn)代雷達體制廣泛采用的是頻域算法。頻域算法的實現(xiàn)要求發(fā)展快速傅立葉變換" title="傅立葉變換">傅立葉變換的硬件,以前多用高速FFT運算器件實現(xiàn)頻域脈壓。但隨著通用DSP 器件速度的不斷加快,這些專用FFT 器件不僅沒有了高速FFT算法運算上的優(yōu)勢,同時還伴隨有功能單一、不便于功能擴展、成本高、實現(xiàn)電路復雜等劣勢,因此逐漸被淘汰,取而代之的是高速DSP 器件。本文正是用TI公司的高性能的TMS320C6701浮點DSP來實現(xiàn)頻域數(shù)字脈沖壓縮。

2 TMS320C6701的結(jié)構(gòu)和性能

TMS320C6701(以下簡稱C6701)是TI公司近年來推出的含多個處理單元的一種新型浮點DSP芯片。它采用VLIW結(jié)構(gòu),在167MHz的主頻下可以得到1GFLOPS的高處理速度。CPU中包括了兩套對稱的運算單元(L,S,M,D)和相應的兩套寄存器組,每組有16個32位寬的寄存器。每個功能單元輸入輸出端口相互獨立,可實現(xiàn)并行處理。

C6701的地址總線為32位,尋址范圍達到4GB。存儲空間可分為四部分:片內(nèi)程序空間、片內(nèi)數(shù)據(jù)空間、外部存儲空間和內(nèi)部外圍設備空間,可通過對五個BOOTMODE引腳的靈活設置設定各空間的地址范圍。片內(nèi)數(shù)據(jù)空間又分成兩塊,每一塊RAM被組織為八個2K×16的存儲體,使得CPU可以同時訪問不同存儲體的數(shù)據(jù),而不會發(fā)生沖突。片內(nèi)程序空間可設為Cache,存儲經(jīng)常使用的代碼,減少片外訪問次數(shù),從而提高程序運行速度。

C6701的外圍端口包括DMA控制器、主機接口(HPI)、中斷選擇等。兩個多通道緩存串行口(McBSP),除多通道、雙緩存外,還支持多種數(shù)據(jù)格式、硬件A/μ率壓擴、位時鐘和幀時鐘的靈活編程,另外還提供SBSRAM、SDRAM等高速存儲器的無縫接口。

C6701采用間接尋址,有線性方式和循環(huán)方式兩種。程序按三級流水線執(zhí)行,即取指、譯碼、執(zhí)行。C6701具有豐富的指令集,內(nèi)含50 余條指令,且大部分是單周期的,可完成數(shù)據(jù)傳輸、算術(shù)邏輯運算和程序控制等功能。

3 頻域脈沖壓縮系統(tǒng)的硬件結(jié)構(gòu)和原理

以C6701為核心器件,輔以相應的輸入輸出電路,可完成數(shù)字頻域脈沖壓縮系統(tǒng)的設計。實現(xiàn)的硬件結(jié)構(gòu)如圖3所示。

將正交的兩路采樣信號輸入到放大器。放大器一方面對信號放大,另一方面也將放大的信號以差分方式輸出。信號以差分方式輸出是為了抑制掉高階諧波分量,濾掉各種干擾信號(如電源和地的噪聲),這樣有利于提高A/D轉(zhuǎn)換器的性能。系統(tǒng)選用了12位A/D轉(zhuǎn)換芯片AD9220 ,該芯片具有單端輸入和差分輸入兩種方式,因此,放大器輸出信號能直接輸入到AD9220進行模/數(shù)轉(zhuǎn)換。兩路回波信號經(jīng)AD9220正交采樣后,再經(jīng)符號擴展成16位存入FIFO。C6701處理器將輸入的32位信號送到內(nèi)部RAM,按照圖2所示的方法進行頻域脈壓處理。首先對輸入信號進行FFT變換,將信號變成離散的頻域抽樣值。然后將FFT變換結(jié)果和匹配濾波系數(shù)相乘。設計中將匹配濾波器的系數(shù)存放在FLASH ROM中,上電后將此系數(shù)搬移到內(nèi)部高速數(shù)據(jù)RAM,然后才進行運算。為了獲得-40dB以下的副瓣電平,通常將匹配濾波器的系數(shù)進行漢明加權(quán)后存放在ROM中。再后,對相乘結(jié)果進行反傅立葉變換,完成頻域脈壓。最后,將反傅立葉變換結(jié)果進行求模運算,得出離散的脈壓信號并將其輸出。由于C6701是浮點處理器,既保證了較高的精度,又不用考慮溢出問題,使得有限字長的影響可以忽略不計。當雷達發(fā)射周期較長時,可以將輸入信號分段進行處理,每段單獨進行頻域脈沖壓縮,然后按照重疊保留法將每段壓縮結(jié)果組合成整個信號脈壓輸出。

以上脈壓算法可以通過編程在DSP內(nèi)部實現(xiàn),這不僅簡化了電路、減小了體積、提高了系統(tǒng)的可靠性,而且擴展了系統(tǒng)的功能,使系統(tǒng)具有較高的靈活性,即在不改變硬件電路的情況下,只需改變系統(tǒng)軟件和外部ROM中的匹配系數(shù),就能完成不同信號的脈沖壓縮功能。

4 頻域脈沖壓縮系統(tǒng)的軟件設計

頻域脈沖壓縮系統(tǒng)的軟件設計主要采用TI 公司的CCS軟件開發(fā)。在CCS下,軟件可分為三個階段。第一階段,根據(jù)任務編寫C語言程序,并對程序進行優(yōu)化。當代碼性能較低時,為改進代碼性能進入第二階段,第二階段利用優(yōu)化方法重新編寫C代碼,并檢查所生成的代碼性能。第三階段,從C語言程序中抽出對性能影響很大的程序段,使用線性匯編語言重新編寫,然后使用匯編優(yōu)化器對線性匯編程序進行優(yōu)化,從而得到滿意的代碼性能。根據(jù)以上方法,編寫出的脈沖壓縮系統(tǒng)的軟件包括系統(tǒng)初始化子程序" title="子程序">子程序、DMA子程序、正傅立葉變換FFT子程序和反傅立葉變換IFFT子程序、復數(shù)相乘子程序、求模子程序等。其流程圖如圖4所示。

在執(zhí)行系統(tǒng)初始化程序時,要對系統(tǒng)的控制狀態(tài)寄存器、外部存儲器接口控制寄存器等進行參數(shù)設置,保證系統(tǒng)按要求正常工作。為提高系統(tǒng)效率,系統(tǒng)通過DMA通道從外部CE2空間將數(shù)據(jù)讀入片內(nèi)RAM,所以初始化程序必須設置好外部存儲器CE2空間的控制寄存器。在進行FFT變換子程序的設計時,因為基四算法比基二算法快,并且頻率抽取算法比時間抽取算法能更好地發(fā)揮C6701的并行運算能力,所以采用基四頻率抽取算法。對4096點信號進行FFT變換,所需時間≤400μs。編寫的復數(shù)數(shù)組相乘通用子程序?qū)崿F(xiàn)4096點運算所需時間≤95μs。對于反變換,可以直接利用前面的FFT算法實現(xiàn),即先對輸入頻域序列作共軛變換,然后進行FFT運算,并對所得的時域序列再作共軛變換,最后除以FFT變換數(shù)據(jù)的個數(shù)。但這樣進行反變換所需要的時間較長,不能實時處理。為此按照基四頻率抽取的算法編寫了IFFT子程序,此IFFT子程序經(jīng)過CCS優(yōu)化之后,對4096點逆變換來講,需要400μs左右。本程序和FFT子程序配合使用,可以方便地實現(xiàn)信號的正傅立葉變換和反傅立葉變換,而不需要進行位反轉(zhuǎn)操作,不僅節(jié)省了存儲空間,而且加快了運算速度。為求復信號的模值,可以采用迭代等算法編寫求模子程序。

系統(tǒng)初始化程序如下:

system_intr ( )

{ LOAD_REG_FIELD(CSR,0,0,2);

SET_REG(ICR,0xFFF0);

REG_WRITE(EXTERNAL_INTR_POL_ADDR,0);

INTR_MAP_RESET();

SET_REG(ISTP,0);

LOAD_FIELD(EMIF_CE2_CTRL_ADDR,5,READ_SETUP,READ_SETUP_SZ);

LOAD_FIELD(EMIF_CE2_CTRL_ADDR,8,READ_STROBE,READ_STROBE_SZ);

LOAD_FIELD(EMIF_CE2_CTRL_ADDR,5, READ_HOLD,READ_HOLD_SZ);

}

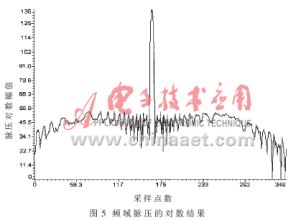

圖5是利用CCS提供的數(shù)據(jù)圖形顯示工具進行坐標變換后的脈壓結(jié)果。此線性調(diào)頻脈沖參數(shù)為:時寬 32μs,帶寬5MHz,采樣頻率為5MHz。

采用先進的高速數(shù)字信號處理器,使得大點數(shù)脈沖壓縮能夠在很短的時間內(nèi)高質(zhì)量地完成。同時利用本系統(tǒng),只要改變存儲器的系數(shù),就可以方便地實現(xiàn)非線性調(diào)頻脈沖壓縮及其它濾波,具有通用性。對于要求更高速度的系統(tǒng),可采用多片TMS320C6701并行處理。而TMS320C6701所帶的符合IEEE1149.1標準的JTAG口能夠方便地進行多片級聯(lián)調(diào)試,再加上開發(fā)軟件CCS所具有強大的功能,可以大大提高工作效率和縮短產(chǎn)品的開發(fā)時間。

參考文獻

1 林茂庸,柯有安.雷達信號理論[M].北京:國防工業(yè)出版社,1984

2 李方慧.TMS320C6000系列DSPs原理與應用[M]. 北京:電子工業(yè)出版社,2003

3 TMS320C6000 CPU and Instruction Set Reference Guide.TI, 2000

4 TMS320C6000 Peripherals Reference Guide. TI,1999

5 TMS320C6000 Code Composer Studio.TI,1999

6 任培宏.一種用時域方法實現(xiàn)的高速數(shù)字脈沖壓縮器[J].電訊技術(shù),2000(6):9~12