電路功能與優(yōu)勢

利用電壓輸出DAC實現(xiàn)真正的16位性能不僅要求選擇適當?shù)腄AC,而且要求選擇適當?shù)呐涮字С制骷?。針對精?6數(shù)模轉(zhuǎn)換應用,,本電路使用AD5542A/AD5541A電壓輸出DAC,、ADR421基準電壓源以及用作基準電壓緩沖的AD8675 超低失調(diào)運算放大器,,提供了一款低風險解決方案。

基準電壓緩沖對于設計至關重要,,因為DAC基準輸入的輸入阻抗與碼高度相關,,如果DAC基準電壓源未經(jīng)充分緩沖,將導致線性誤差,。開環(huán)增益高達120 dB的AD8675已經(jīng)過驗證和測試,,符合本電路應用關于建立時間、失調(diào)電壓和低阻抗驅(qū)動能力的要求,。

需要時,,精密,、低失調(diào)OP1177 可以用作可選的輸出緩沖器,。

這一器件組合可以提供業(yè)界領先的16位分辨率、±1 LSB積分非線性(INL)和±1 LSB微分非線性(DNL),,可以確保單調(diào)性,,并且具有低功耗、小PCB和高性價比等特性,。

圖1. 精密DAC配置(簡化的原理示意圖:未顯示去耦和所有連接)

電路描述

對于無誤差的理想DAC,,輸出電壓與基準電壓相關,如下式所示:

其中D為載入DAC寄存器的十進制數(shù)據(jù)字,,N為DAC的分辨率,。

對于2.5 V基準電壓且N = 16,上述公式可簡化為下式:

這樣,,在中間電平時VOUT為1.25 V,,在滿量程時為2.5 V。

LSB大小為2.5 V/65,536 = 38.1 μV,。

16位時,,1 LSB也相當于滿量程的0.0015%,或者15 ppm FS,。

基準電壓源ADR421(B級)的室溫初始精度為0.04%,,相當于16位時的約27 LSB。此初始誤差可以通過系統(tǒng)校準消除,。ADR421(B級)的溫度系數(shù)典型值為1 ppm/°C,,最大值為3 ppm/°C。

假設使用理想基準電壓源(基準電壓誤差已通過系統(tǒng)校準消除),,則AD5542A的最差情況單極性輸出電壓(包括誤差)可通過下式計算:

其中:

VOUT−UNI為單極性模式最差情況輸出,。

D為載入DAC的碼。

VREF為施加于DAC的基準電壓(假設無誤差),。

VGE為增益誤差,,單位伏特(V),。(注意,基準電壓緩沖的失調(diào)誤差必須包括在增益誤差中,,因此為基準電壓緩沖選用的運算放大器必須具有低輸入失調(diào)電壓特性),。

VZSE 為零電平誤差(失調(diào)誤差),單位伏特(V),。(注意,,可選輸出緩沖放大器的失調(diào)電壓會增加此誤差)

INL為DAC的積分非線性,單位伏特(V),。(注意,,可選輸出緩沖放大器的非線性會增加此誤差)

室溫下,此電路的實測零電平誤差和增益誤差分別為±0.7 LSB和±2 LSB,。在整個溫度范圍內(nèi)(?40°C至+85°C),,零電平誤差為±1.5 LSB,增益誤差為±3 LSB,。這些測量結果是從AD5542A的VOUT直接獲得,,沒有連接輸出緩沖器。

本電路采用電壓輸出DAC AD5542A,,提供真16位INL和DNL,。AD5541A/AD5542A的DAC架構為分段R-2R電壓模式DAC。采用這種配置,,輸出阻抗與碼無關,,而基準電壓源的輸入阻抗則與碼高度相關。因此,,基準電壓緩沖的選擇對于碼相關基準電流的處理非常重要,,如果DAC基準電壓緩沖不充分,可能會導致線性誤差,。選擇配合精密電壓輸出DAC使用的基準電壓緩沖時,,運算放大器的開環(huán)增益、失調(diào)電壓,、失調(diào)誤差溫度系數(shù)和電壓噪聲也是重要的選擇指標,。基準電壓電路中的失調(diào)誤差會引起DAC輸出端產(chǎn)生增益誤差,。

本電路采用驅(qū)動/檢測配置(開爾文檢測)的AD8675運算放大器作為AD5542A的低阻抗輸出基準電壓緩沖,。AD8675具有120 dB的開環(huán)增益,是一款精密,、36 V,、2.8 nV/√Hz運算放大器。其典型失調(diào)電壓為10 µV,典型溫漂小于0.2 µV/°C,,噪聲為0.1 µV峰峰值(0 Hz至10 Hz),,因而AD8675特別適合那些需要最小誤差源的應用。

AD5542A有兩種工作模式:緩沖模式和非緩沖模式,。使用何種工作模式由具體應用及其建立時間,、負載阻抗、噪聲等要求而定,??梢赃x擇輸出緩沖器來優(yōu)化直流精度或快速建立時間。本電路所用的可選輸出放大器為高精度OP1177,。DAC的輸出阻抗恒定(典型值6.25 kΩ),,且與碼無關,但為了將增益誤差降至最小,,輸出放大器的輸入阻抗應盡可能高,。輸出放大器還應具有1 MHz或更高的3 dB帶寬。輸出放大器給系統(tǒng)增加了另一個時間常數(shù),,因此會延長輸出的建立時間,。運算放大器的帶寬越寬,,則DAC與放大器組合的有效建立時間越短,。

圖1所示的器件組合實現(xiàn)了最小的PCB面積。AD5542A采用3 mm × 3 mm,、16引腳LFCSP或16引腳TSSOP封裝,。AD5541A采用3 mm × 3 mm、10引腳LFCSP或10引腳MSOP封裝,。

請注意,,AD5541A不包含基準電壓和地上的開爾文檢測線路、清零功能以及RFB 和 RINV電阻,。

AD8675和ADR421采用8引腳MSOP或SOIC封裝,,OP1177采用8引腳MSOP封裝。

可選輸出運算放大器為采用單位增益配置的OP1177,,它包括一個與反相輸入端串聯(lián)的6.19 kΩ電阻,。此電阻用于抵消偏置電流,并與AD5542A的輸出電阻相匹配,,后者約為6.25 kΩ ± 20%,。

測量結果表明,AD5542A/AD5541A是高精度,、低噪聲電平設置應用的理想選擇,。在這一高精度、高性能系統(tǒng)中,通過基準電壓源ADR421和基準電壓緩沖AD8675保持直流性能水平,。測量直接在VOUT上進行,,沒有連接可選的輸出緩沖器。

積分非線性和微分非線性測量

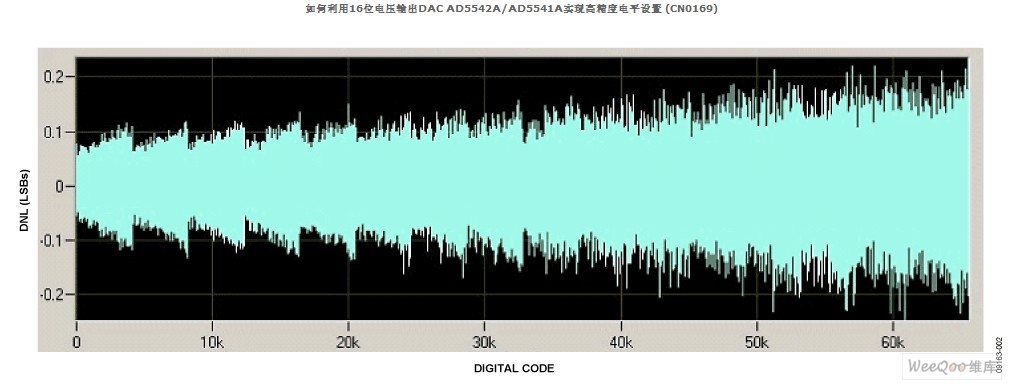

積分非線性(INL)誤差指實際DAC傳遞函數(shù)與理想傳遞函數(shù)的偏差,,用LSB表示,。差分非線性(DNL)誤差指實際步進大小與1 LSB的理想值之間的差異。圖1所示電路提供了16位分辨率,,DNL和INL均為±1 LSB,。圖2和圖3顯示了該電路的DNL和INL性能。

圖2. 微分非線性

圖3. 積分非線性

零電平誤差和增益誤差測量

室溫下,,零電平誤差 (VZSE)和增益誤差(VGE) 的測量結果分別為±0.7 LSB和±2 LSB,。在整個溫度范圍內(nèi)(?40°C至+85°C),零電平誤差為±1.5 LSB,,增益誤差為±3 LSB,。

布局考慮

在任何注重精度的電路中,必須仔細考慮電路板上的電源和接地回路布局,。包含本電路的印刷電路板(PCB)應將模擬部分與數(shù)字部分分離,。如果該電路所在系統(tǒng)中有其它器件要求AGND至DGND連接,則只能在一個點上進行連接,。該接地點應盡可能靠近AD5542A/AD5541A,。本電路應該采用具有較大面積接地層和電源層的多層PCB。

AD5542A/AD5541A的電源應使用10 μF和0.1 μF電容進行旁路,。這些電容應盡可能靠近該器件,,0.1 μF電容最好正對著該器件右上方。10 μF電容應為鉭珠型或陶瓷型電容,。0.1 μF電容必須具有低等效串聯(lián)電阻(ESR)和低等效串聯(lián)電感(ESL),,普通陶瓷型電容通常具有這些特性。

針對內(nèi)部邏輯開關引起的瞬態(tài)電流所導致的高頻,,該0.1 μF電容可提供低阻抗接地路徑,。

電源走線應盡可能寬,以提供低阻抗路徑,,并減小電源線路上的毛刺效應,。時鐘和其它快速開關的數(shù)字信號應通過數(shù)字地將其與電路板上的其它器件屏蔽開。