摘 要: 介紹了TMS320C64X系列DSP內(nèi)部Turbo碼協(xié)處理器" title="協(xié)處理器">協(xié)處理器(TCP)的結(jié)構(gòu)和算法。給出了使用TCP實(shí)現(xiàn)符合3GPP" title="3GPP">3GPP協(xié)議的Turbo譯碼的程序流程,實(shí)現(xiàn)了一種使用中斷服務(wù)程序控制的高效處理流程,最后給出了TCP譯碼性能與處理時(shí)延" title="時(shí)延">時(shí)延的硬件實(shí)現(xiàn)結(jié)果,并做出了一定的分析。

關(guān)鍵詞: TMS320C64X TCP Turbo Decoding 性能

自1993年Turbo編碼理論提出以來(lái),有關(guān)Turbo碼設(shè)計(jì)及其性能的研究已經(jīng)成為國(guó)際信息與編碼理論界最為重要的研究課題之一。Turbo碼在低信噪比下所表現(xiàn)出的近Shannon限的性能使得它在深空通信、移動(dòng)通信等領(lǐng)域中有著廣闊的應(yīng)用前景。由于Turbo碼編碼方式靈活、譯碼算法復(fù)雜,不適合在傳統(tǒng)硬件電路如FPGA上實(shí)現(xiàn)。TMS320C64X是TI公司推出的高性能定點(diǎn)DSP系列,片上除了高性能的C64x數(shù)字信號(hào)處理內(nèi)核外,還集成了Turbo碼協(xié)處理器(TCP,Turbo Coder Coprocessor),用于對(duì)符合3GPP協(xié)議以及IS2000協(xié)議的Turbo編碼進(jìn)行高速譯碼。

1 TCP的基本結(jié)構(gòu)

TMS320C64X是TI公司最新推出的處理能力高達(dá)4800MIPS的高性能DSP,內(nèi)部嵌入了Turbo譯碼協(xié)處理器(TCP)和Viterbi譯碼協(xié)處理器(VCP),專門用于無(wú)線通信中的高速數(shù)據(jù)處理。 片上的TCP能夠?qū)Χ噙_(dá)36路的384kbps或6路2Mbps的Turbo編碼信道在迭代6次的情況下進(jìn)行譯碼,其高速并行結(jié)構(gòu)能夠在小于2ms的時(shí)間內(nèi)完成3GPP協(xié)議中的2Mbps業(yè)務(wù)迭代譯碼,并且能夠通過(guò)編程控制性能進(jìn)一步減少處理時(shí)延。

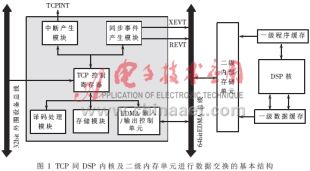

TCP通過(guò)EDMA(增強(qiáng)型DMA)同L2存儲(chǔ)器(二級(jí)內(nèi)部存儲(chǔ)單元)進(jìn)行數(shù)據(jù)交換" title="數(shù)據(jù)交換">數(shù)據(jù)交換,其基本結(jié)構(gòu)如圖1所示。TCP控制寄存器" title="控制寄存器">控制寄存器控制整體工作狀態(tài),包含相關(guān)編碼信息、DSP總線傳輸能力、譯碼性能等信息;EDMA輸入/輸出單元控制EDMA總線實(shí)現(xiàn)二級(jí)內(nèi)部存儲(chǔ)單元同TCP之間的數(shù)據(jù)交換;同步事件產(chǎn)生模塊產(chǎn)生EDMA讀/寫(xiě)同步事件;內(nèi)部存儲(chǔ)模塊和譯碼處理單元負(fù)責(zé)數(shù)據(jù)存儲(chǔ)與譯碼計(jì)算。

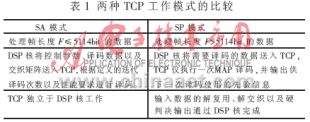

TCP有兩種工作方式:Standalong(SA)模式與Shared Processing(SP)模式。在SA模式下,TCP完成編程規(guī)定次數(shù)的迭代譯碼并輸出硬判決結(jié)果;在SP模式下,TCP僅完成一次MAP算法并輸出供下一次譯碼使用的先驗(yàn)信息。表1示出了兩種工作方式的區(qū)別。

3GPP協(xié)議中支持Turbo碼的信道最大編碼塊的大小為5114bit,所以在實(shí)現(xiàn)上選擇TCP工作在SA模式。

2 TCP的譯碼算法

MAP算法[1]是一種對(duì)具有有限狀態(tài)馬爾可夫特性的碼及離散無(wú)記憶特性的信道提供逐符號(hào)或逐比特似然值的最優(yōu)算法。Log-MAP算法[2]將標(biāo)準(zhǔn)算法中的似然值全部用對(duì)數(shù)似然值表示。這樣乘法運(yùn)算就變成了加法,加法變成了ea+eb=emax{a,b}+ln[1+exp(-a-b)],這里的對(duì)數(shù)項(xiàng)可通過(guò)一次查表和一次加法運(yùn)算實(shí)現(xiàn)。Max-Log-MAP算法[2]在上述對(duì)數(shù)域的算法中,將似然值加法表示式中的對(duì)數(shù)分量忽略掉,使似然加法完全變成求最大值運(yùn)算。

由于Turbo碼編碼方式靈活、譯碼算法復(fù)雜,所以在傳統(tǒng)硬件電路上實(shí)現(xiàn)Turbo譯碼比較復(fù)雜。

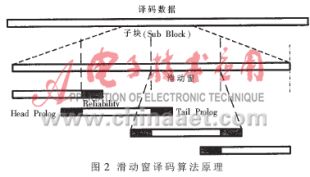

TCP很好地解決了算法實(shí)現(xiàn)中存在的問(wèn)題。TCP使用滑動(dòng)窗譯碼算法[5],將接收序列分割成子塊(Sub block)送入結(jié)構(gòu)相同的多個(gè)并行譯碼器進(jìn)行處理,分割數(shù)量的原則是保證多個(gè)譯碼器并行度達(dá)到最大。每個(gè)子塊通過(guò)多個(gè)滑動(dòng)窗使用Max-log-MAP算法進(jìn)行譯碼,譯碼過(guò)程中產(chǎn)生的臨時(shí)數(shù)據(jù)α和β保存在內(nèi)部存儲(chǔ)模塊的α單元和β單元中,需要時(shí)再通過(guò)計(jì)算得到先驗(yàn)信息或譯碼結(jié)果。滑動(dòng)窗譯碼算法的原理如圖2所示。

Turbo碼編碼時(shí),編碼器的狀態(tài)轉(zhuǎn)換關(guān)系是連續(xù)的馬爾科夫過(guò)程。在譯碼時(shí),需要確定編碼器的初始狀態(tài)和終止?fàn)顟B(tài)以及狀態(tài)之間的轉(zhuǎn)換關(guān)系。接收序列被分割為多個(gè)子塊之后,狀態(tài)的連續(xù)性被打斷。這樣,對(duì)于輸入到一個(gè)譯碼器中的子塊就不能確定其初始狀態(tài)和終止?fàn)顟B(tài)。因此,把一個(gè)子塊分為三個(gè)部分:頭延伸(Head Prolog)、可信部分(Reliability)和尾延伸(Tail Prolog)。Head Prolog初始狀態(tài)和Tail Prolog終止?fàn)顟B(tài)都設(shè)為等概率,然后根據(jù)接收序列以及編碼器狀態(tài)轉(zhuǎn)換規(guī)律逐步計(jì)算Reliability。在Reliability部分、起始時(shí)刻值和終止時(shí)刻近似調(diào)整為分割前的狀態(tài)時(shí),Head Prolog和Tail Prolog為冗余重疊的部分,此時(shí)計(jì)算譯碼輸出只需考慮Reliability部分,所以算法在譯碼性能上沒(méi)有什么影響,但是能夠極大地減少處理時(shí)延。另外,TCP還提供停止迭代譯碼標(biāo)準(zhǔn)Stopping Criteria,可通過(guò)對(duì)外信息信噪比(SNR)的估計(jì)來(lái)判斷是否需要繼續(xù)進(jìn)行迭代。如果當(dāng)前信息已經(jīng)不能再提供編碼增益,則立刻輸出硬判決結(jié)果而不考慮剩余的迭代次數(shù)。

3 TCP的編程實(shí)現(xiàn)

3.1 輸入數(shù)據(jù)的量化

TCP要求輸入數(shù)據(jù)為8bit的有符號(hào)數(shù),并認(rèn)為其格式為:SIIII.FFF(S為符號(hào)位,I為整數(shù)位,F(xiàn)為小數(shù)位)。假設(shè)接收信號(hào)可以表示為:Ri=![]() ×ui+ni。其中,ui=±1;ni為發(fā)送端經(jīng)過(guò)BPSK映射的原始數(shù)據(jù);Esymbol是發(fā)送端符號(hào)能量,數(shù)據(jù)量化時(shí)需要去掉這個(gè)能量,同時(shí)將數(shù)據(jù)恢復(fù)成BPSK映射之前的形式。而一個(gè)分量譯碼器產(chǎn)生的先驗(yàn)信息[2~3]可以表示為:Wk=

×ui+ni。其中,ui=±1;ni為發(fā)送端經(jīng)過(guò)BPSK映射的原始數(shù)據(jù);Esymbol是發(fā)送端符號(hào)能量,數(shù)據(jù)量化時(shí)需要去掉這個(gè)能量,同時(shí)將數(shù)據(jù)恢復(fù)成BPSK映射之前的形式。而一個(gè)分量譯碼器產(chǎn)生的先驗(yàn)信息[2~3]可以表示為:Wk=![]() xk+

xk+![]() zk+Wk(

zk+Wk(![]() yk)。其中,

yk)。其中,![]() xk由系統(tǒng)比特xk產(chǎn)生,

xk由系統(tǒng)比特xk產(chǎn)生,![]() zk由上級(jí)譯碼器生成的先驗(yàn)信息zk產(chǎn)生,Wk(

zk由上級(jí)譯碼器生成的先驗(yàn)信息zk產(chǎn)生,Wk(![]() yk)由校驗(yàn)比特yk產(chǎn)生,σ2為高斯白噪聲的方差。通常情況下,為了方便計(jì)算,去掉其中的系數(shù)

yk)由校驗(yàn)比特yk產(chǎn)生,σ2為高斯白噪聲的方差。通常情況下,為了方便計(jì)算,去掉其中的系數(shù)![]() 。于是輸入信號(hào)的量化因子可以表示為:ScaleFactor=

。于是輸入信號(hào)的量化因子可以表示為:ScaleFactor= 。其中,

。其中, 可以通過(guò)計(jì)算信號(hào)幅值的均值得到:

可以通過(guò)計(jì)算信號(hào)幅值的均值得到:![]() 通過(guò)計(jì)算接收信號(hào)幅值的方差得到:

通過(guò)計(jì)算接收信號(hào)幅值的方差得到:![]()

![]() 。

。

3.2 控制寄存器的配置

TCP中包含12個(gè)控制寄存器,這些寄存器分為三類:基本參數(shù)寄存器、EDMA接口參數(shù)寄存器以及尾比特寄存器。

基本參數(shù):控制編碼信息以及譯碼的相關(guān)標(biāo)準(zhǔn);

EDMA接口參數(shù): EDMA通道的相關(guān)參數(shù);

尾比特:確定編碼器最終狀態(tài)的信息。

3.3 EDMA配置以及DSP核同TCP之間的數(shù)據(jù)交換

EDMA是C6000系列DSP中的一個(gè)重要單元,負(fù)責(zé)二級(jí)內(nèi)存(L2 存儲(chǔ)器)同各個(gè)外設(shè)之間的數(shù)據(jù)交換[7~8]。

C64X系列DSP的EDMA通道共有64條,其中31/30(讀/寫(xiě))專門用于DSP核同TCP之間的數(shù)據(jù)交換。EDMA完成參數(shù)配置并啟動(dòng)之后,EDMA通道進(jìn)入使能狀態(tài)等待觸發(fā)。TCP啟動(dòng)后,產(chǎn)生相應(yīng)的讀/寫(xiě)同步事件TCPXEVT/TCPREVT觸發(fā)EDMA通道進(jìn)行數(shù)據(jù)傳輸。一次簡(jiǎn)單譯碼處理中的完整觸發(fā)過(guò)程如圖3所示。

結(jié)合TCP控制寄存器中的EDMA接口參數(shù)使用提供的API函數(shù)[9]配置EDMA通道傳輸參數(shù) [7] 。

3.4 高效的TCP處理模式

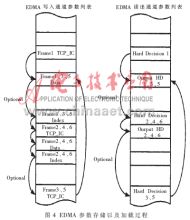

通常情況下并不滿足于對(duì)一段編碼數(shù)據(jù)實(shí)現(xiàn)譯碼,而是希望DSP滿負(fù)荷地工作,對(duì)連續(xù)到達(dá)的各種編碼格式(已知)的數(shù)據(jù)完成譯碼。在這里設(shè)計(jì)了一種奇偶交替的譯碼模式:將譯碼數(shù)據(jù)按照到達(dá)順序分為奇數(shù)組和偶數(shù)組,生成滿足編碼格式的TCP控制寄存器參數(shù)以及相應(yīng)的EDMA配置參數(shù)。TCP進(jìn)行第N個(gè)編碼數(shù)據(jù)譯碼處理的同時(shí),EDMA寫(xiě)通道向TCP傳輸?shù)贜+1個(gè)編碼數(shù)據(jù)控制參數(shù)和譯碼數(shù)據(jù),EDMA讀通道將第N-1個(gè)編碼數(shù)據(jù)的譯碼結(jié)果輸出,同時(shí)利用譯碼完成產(chǎn)生的中斷服務(wù)程序處理第N+2個(gè)數(shù)據(jù)的相關(guān)參數(shù)配置以及數(shù)據(jù)量化。EDMA的RAM中的參數(shù)存放格式如圖4所示。

3.5 TCP程序?qū)崿F(xiàn)流程

總之,TCP程序?qū)崿F(xiàn)應(yīng)包括以下步驟:

(1)數(shù)據(jù)量化;

(2)構(gòu)造TCP控制參數(shù)以及EDMA配置參數(shù);

(3)啟動(dòng)并配置EDMA通道;

(4)啟動(dòng)TCP產(chǎn)生同步事件觸發(fā)EDMA通道;

(5)接收硬判決結(jié)果。

(因本文篇幅偏長(zhǎng),本刊刪去了“TCP程序?qū)崿F(xiàn)流程圖”。如讀者感興起,可向作者索取。)

4 TCP譯碼性能硬件實(shí)現(xiàn)與分析

4.1 TCP譯碼性能

使用TMS320C6416 7E3(CPU時(shí)鐘為705.6MHz),對(duì)原始長(zhǎng)度為336bit和3840bit的符合3GPP協(xié)議的碼率為1/3的Turbo編碼數(shù)據(jù)進(jìn)行譯碼。譯碼性能如圖5和圖6所示。

4.2 TCP譯碼處理時(shí)延

使用TMS320C6416 7E3(CPU時(shí)鐘為705.6MHz),對(duì)原始長(zhǎng)度為336bit和3840bit的符合3GPP協(xié)議的碼率為1/3的Turbo編碼數(shù)據(jù)進(jìn)行譯碼。考慮迭代次數(shù)I=6、8、16;Prolog長(zhǎng)度P=24(未經(jīng)速率適配)、48(經(jīng)過(guò)速率適配)時(shí)得到的處理時(shí)延結(jié)果如表2和表3所示(只考慮譯碼處理時(shí)延,參數(shù)配置以及EDMA通道進(jìn)行數(shù)據(jù)傳輸所用時(shí)間不計(jì)算在內(nèi))。

通常情況下,Turbo碼的性能同交織長(zhǎng)度有很大關(guān)系,交織長(zhǎng)度越大,性能越好,但所需處理時(shí)延也就越高。使用TCP譯碼,長(zhǎng)度為336bit的短數(shù)據(jù)幀經(jīng)過(guò)8次迭代,在信噪比(SNR)為2dB下誤碼率(BER)達(dá)到10-7量級(jí),所需處理時(shí)延大概為50~60μs;長(zhǎng)度為3840bit的數(shù)據(jù)幀,經(jīng)過(guò)8次迭代,在信噪比為0.8dB下誤碼率達(dá)到10-8量級(jí),處理時(shí)延大約為300~350μs。可以認(rèn)為TCP在譯碼性能與處理時(shí)延兩個(gè)方面都能夠比較好地滿足3G系統(tǒng)對(duì)于譯碼模塊的要求。TCP作為C64X系列DSP的一個(gè)協(xié)處理器,相關(guān)的速率適配、數(shù)據(jù)量化等一系列工作都可以通過(guò)DSP核完成,較傳統(tǒng)的硬件電路有很大優(yōu)勢(shì)。

參考文獻(xiàn)

1 Claude Berrou and Alain Glavieux.Near Optimum Error Correcting Coding And Decoding:Turbo-Codes.Texas Instrument,1996

2 Patrick Robertson. Optimal and Sub-Optimal Maximum A Posteriori Algorithms Suitable for Turbo Decoding.Texas Instrument,1997

3 TMS320C6000 Peripherals Reference Guide.Texas Instrument,2001

4 TMS320C64x DSP Turbo-Decoder Coprocessor (TCP) Reference Guide. Texas Instrument,2003

5 Using TMS320C6416 Coprocessor Turbo Coprocessor. Texas Instrument,2003

6 TMS320C6416 Coprocessors and Bit Error Rates. Texas Instrument,2003

7 TMS320C6000 DSP Enhanced Direct Memory Access (ED-MA) Controller Reference Guide. Texas Instrument,2002

8 Applications Using the TMS320C6000 Enhanced DMA.Texas Instrument,2003

9 TMS320C6000 Chip Support Library API User’s Guide.Texas Instrument,2003