電路功能與優(yōu)勢

許多應(yīng)用都要求通過高分辨率、差分輸入ADC來轉(zhuǎn)換單端模擬信號,無論是雙極性還是單極性信號。本直流耦合電路可將單端輸入信號轉(zhuǎn)換為差分信號,適合驅(qū)動PulSAR系列ADC中的18位、1 MSPS器件AD7982。該電路采用單端轉(zhuǎn)差分驅(qū)動器ADA4941-1 和超低噪聲5.0 V基準電壓源ADR435 ,可以接受許多類型的單端輸入信號,包括高壓至低壓范圍內(nèi)的雙極性或單極性信號。整個電路均保持直接耦合。如果需要重點考慮電路板空間,可以采用小封裝產(chǎn)品,圖1所示的所有IC均可提供3 mm × 3 mm LFCSP或3 mm × 5 mm MSOP小型封裝。

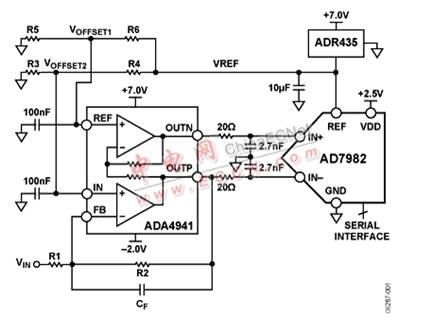

圖1:單端轉(zhuǎn)差分直流耦合驅(qū)動器電路(原理示意圖)

電路描述

AD7982的差分輸入電壓范圍由REF引腳上的電壓設(shè)置。當VREF = 5 V時,差分輸入電壓范圍為 ±VREF = ±5 V。從單端源VIN到ADA4941-1的OUTP的電壓增益(或衰減)由R2與R1之比設(shè)置。R2與R1之比應(yīng)等于VREF 與輸入電壓峰峰值VIN之比。當單端輸入電壓峰峰值為10 V且 VREF = 5 V時,R2與R1之比應(yīng)為0.5。OUTN上的信號為OUTP信號的反相。R1的絕對值決定電路的輸入阻抗。反饋電容CF根據(jù)所需的信號帶寬選擇,后者約為1/(2πR2CF)。20 Ω電阻與2.7 nF電容構(gòu)成3 MHz單極點低通噪聲濾波器。電阻R3和R4設(shè)置AD7982的IN?輸入端的共模電壓。

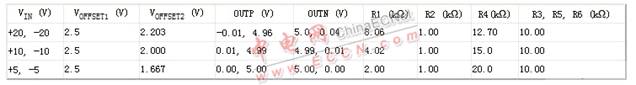

此共模電壓值等于VOFFSET2 × (1 + R2/R1),其中VOFFSET2 = VREF × R3/(R3 + R4)。電阻R5和R6設(shè)置ADC的IN+輸入端的共模電壓。此電壓等于VOFFSET1 = VREF × R5/(R5 + R6)。ADC的共模電壓(等于VOFFSET1)應(yīng)接近VREF/2,這意味著R5 = R6。表1列出了適合常用輸入電壓范圍的一些標準1%允許電阻值。

表1:適合常用輸入電壓范圍的電路值和電壓

請注意,ADA4941-1采用+7 V和?2 V電源供電。由于各路輸出的擺幅必須達到0 V至+5 V,因此正電源電壓應(yīng)比+5 V高數(shù)百毫伏,負電源電壓應(yīng)比0 V低數(shù)百毫伏。本電路選擇+7 V和?2 V的電源電壓。+7 V電源還能提供足夠的裕量,為ADR435供電。只要ADA4941-1上的絕對最大值總電源電壓不超過12 V,并且滿足ADR435的裕量要求,則也可以使用其它電壓。

AD7982需要一個 +2.5 V supply for VDD電源以及一個VIO 電源(圖1未顯示),后者的電壓可以在1.8 V至5 V之間,取決于I/O邏輯接口電平。

本電路對電源時序不敏感。在瞬間過壓條件下,AD7982輸入端可以承受最高±130 mA的電流。

AD7982 SPI兼容串行接口(圖1未顯示)能夠利用SDI輸入,將幾個ADC以菊花鏈形式連接到單個三線式總線上,并提供一個可選的忙閑指示。采用獨立電源VIO時,該器件與1.8V、2.5V、3V和5V邏輯兼容。

為了使本文所討論的電路達到理想的性能,必須采用出色的布線、接地和去耦技術(shù)。至少應(yīng)采用四層PCB:一個接地層、一個電源層和兩個信號層。

所有IC電源引腳都必須采用0.01 μF至0.1 μF低電感、多層陶瓷電容(MLCC)對接地層去耦(為簡明起見,圖1未顯示),并應(yīng)遵循“了解更多信息”部分所引用IC的各數(shù)據(jù)手冊中提出的建議。

有關(guān)推薦的布線方式和關(guān)鍵器件位置,應(yīng)參考產(chǎn)品*估板。請在器件的產(chǎn)品主頁上查看(見“了解更多信息”部分)。

常見變化

ADR43x 系列基準電壓源可以提供與ADC接口的各種不同基準電壓值。