隨著可編程技術(shù)的不斷發(fā)展,,FPGA被廣泛應(yīng)用于電子設(shè)計(jì)的各個領(lǐng)域。新的設(shè)計(jì)思想和設(shè)計(jì)方法也被不斷的提出和應(yīng)用,,如FPGA的動態(tài)部分重構(gòu)技術(shù),。所謂動態(tài)重構(gòu)是指對于時序變化的數(shù)字邏輯系統(tǒng),其時序邏輯的發(fā)生,,不是通過調(diào)用芯片內(nèi)不同區(qū)域不同邏輯資源的組合來實(shí)現(xiàn),,而是通過對具有專門緩存邏輯資源的FPGA,進(jìn)行局部和全局芯片邏輯的動態(tài)重構(gòu)而快速實(shí)現(xiàn),。動態(tài)可重構(gòu)FPGA器件在編程結(jié)構(gòu)上應(yīng)具有專門的特征,,其內(nèi)部邏輯塊和內(nèi)連線的改變可以通過讀取不同的配置比特流文件來實(shí)現(xiàn)邏輯重建。動態(tài)部分重構(gòu)是指重新配置FPGA的部分區(qū)域,,重構(gòu)過程中,,F(xiàn)PGA其余部分的工作狀態(tài)不受影響。此方式減小了重構(gòu)范圍和單元數(shù)目,,從而大大縮短了FPGA的重構(gòu)時間,。

應(yīng)用FPGA動態(tài)部分重構(gòu)功能使硬件設(shè)計(jì)更加靈活,可用于硬件的遠(yuǎn)程升級,、系統(tǒng)容錯和演化硬件以及通信平臺設(shè)計(jì)[1]等,。動態(tài)部分重構(gòu)可以通過兩種方法實(shí)現(xiàn):基于模塊化設(shè)計(jì)方法(Module-Based Partial Reconfiguration)和基于差別的設(shè)計(jì)方法(Difference-Based Partial Reconfiguration),本文以基于模塊化設(shè)計(jì)為例說明實(shí)現(xiàn)部分重構(gòu)的方法,。

1 FPGA配置原理簡介

本文針對Xilinx公司的FPGA進(jìn)行研究,,支持模塊化動態(tài)部分重構(gòu)的器件族有Virtex/-II/-E和Virtex-II Pro,。

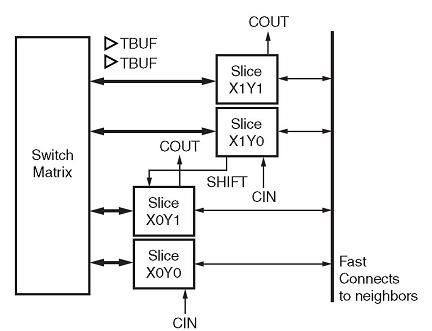

Xilinx公司FPGA是基于SRAM工藝的,包括配置邏輯塊(CLBs),,輸入輸出塊(IOBs),,塊RAMs,,時鐘資源和編程布線等資源[2],。CLBs是構(gòu)造用戶所需邏輯的功能單元,IOBs提供封裝引腿與內(nèi)部信號引線的接口,??删幊袒ミB資源提供布線通道連接可配置元件的輸入和輸出到相應(yīng)的網(wǎng)絡(luò)。

存儲在內(nèi)部配置存儲器單元中的數(shù)值決定了FPGA實(shí)現(xiàn)的邏輯功能和互接方式,。Virtex FPGA的配置存儲器是由配置列(Configuration Columns)組成的,,這些配置列以垂直陣列的方式排列,如圖1給出了Virtex-E XCV600E器件的配置列構(gòu)成圖,。配置存儲器可分為五種配置列:Center 列包含四個全局時鐘的配置信息,;兩個IOB 列存儲位于器件左邊和右邊所有IOBs的配置信息;CLB列存儲FPGA基本邏輯功能的配置信息,;Block SelectRAM Content列存儲內(nèi)部塊RAM的配置信息,;Block SelectRAM Interconnect列存儲內(nèi)部塊RAM間互聯(lián)的配置信息[3]。

圖1 Virtex-E XCV600E的配置列構(gòu)成及地址

配置列根據(jù)分配給它的配置地址(Configuration Address)來尋址,。每一個配置列在FPGA內(nèi)都有唯一的主地址(Major Address)空間,。

FPGA的邏輯功能通過配置比特流(Configuration Bitstream)來實(shí)現(xiàn)。對于動態(tài)部分重構(gòu)功能來說,,需重構(gòu)的配置邏輯是通過下載不同的部分配置比特流來實(shí)現(xiàn)的,。

2基于模塊化動態(tài)部分重構(gòu)FPGA的設(shè)計(jì)方法

所謂的FPGA模塊化設(shè)計(jì)就是將系統(tǒng)按照一定規(guī)則劃分成若干模塊,然后對每個模塊分別進(jìn)行設(shè)計(jì),、綜合,,并將實(shí)現(xiàn)結(jié)果約束在預(yù)先設(shè)置好的區(qū)域內(nèi),最后將所有模塊的實(shí)現(xiàn)結(jié)果有機(jī)的組織起來完成整個系統(tǒng)的設(shè)計(jì)[4],。其劃分模塊的基本原則為:子模塊功能相對獨(dú)立,,模塊內(nèi)部聯(lián)系盡量緊密,模塊間的連接盡量簡單,。對于那些難以滿足模塊劃分準(zhǔn)則的具有強(qiáng)內(nèi)部關(guān)聯(lián)的設(shè)計(jì),,不適合采用此設(shè)計(jì)方法。

FPGA模塊化設(shè)計(jì)的優(yōu)點(diǎn)在于:團(tuán)隊(duì)式并行工作從而加速整個項(xiàng)目的開發(fā)進(jìn)度,;每個子模塊都能夠靈活使用綜合和實(shí)現(xiàn)工具獨(dú)立進(jìn)行優(yōu)化,,從而達(dá)到更好的優(yōu)化結(jié)果;調(diào)試,、更改某個子模塊時,,不會影響其他模塊的實(shí)現(xiàn)結(jié)果,,保證了整個設(shè)計(jì)的穩(wěn)定性與可靠性。

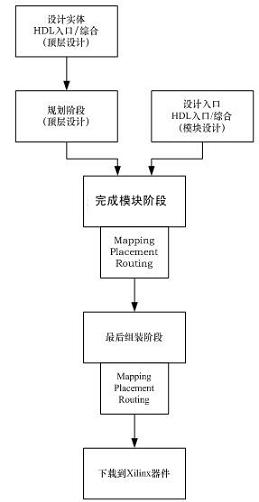

模塊化設(shè)計(jì)方法使用Xilinx公司的ISE軟件設(shè)計(jì)工具,,常用HDL語言作為設(shè)計(jì)輸入,,頂層模塊描述設(shè)計(jì)的全局邏輯,包括設(shè)計(jì)的輸入/輸出,、所有子模塊的黑盒子(Black Box)聲明以及子模塊之間的連接關(guān)系,。所謂黑盒子聲明是指在頂層模塊中僅僅對子模塊進(jìn)行端口描述與信號屬性聲明,并不包含任何實(shí)際邏輯和時序關(guān)系的描述,。子模塊通常也使用HDL語言描述,,分別設(shè)計(jì)出各子模塊的邏輯實(shí)體并綜合所設(shè)計(jì)的子模塊。由于子模塊的輸入/輸出并不是整個設(shè)計(jì)的外部接口,,所以在綜合過程中應(yīng)禁止子模塊插入I/O端口,,而僅在綜合頂層模塊時才插入I/O端口。最后將所有子模塊的實(shí)現(xiàn)結(jié)果和頂層的實(shí)現(xiàn)結(jié)果有機(jī)地組織起立,,完成整個設(shè)計(jì)的實(shí)現(xiàn),。圖2是基于模塊化設(shè)計(jì)方法的流程。

圖2 模塊化設(shè)計(jì)流程

采用模塊化設(shè)計(jì)方法實(shí)現(xiàn)FPGA的動態(tài)部分重構(gòu),,首先進(jìn)行模塊劃分,,將設(shè)計(jì)的固定邏輯即運(yùn)行過程中不需要更改的邏輯劃分到固定模塊,將需要更改的部分劃分到可重構(gòu)模塊中,。其次模塊的放置位置和大小也有限制,,必須遵循一定的規(guī)則[5]:可重構(gòu)模塊的高度和器件的高度一致,從圖1中可以直觀地認(rèn)為模塊必須包含整個配置列,;可重構(gòu)模塊的寬度最小是4個Slice(一個CLB包含兩個完全相同的Slice),,并且必須為4個Slice的倍數(shù);如果可重構(gòu)模塊位于器件的最左邊或是最右邊的Slice列,,則所有位于器件邊緣的IOBs將作為可重構(gòu)模塊的資源,;為了減少設(shè)計(jì)的復(fù)雜度,可重構(gòu)模塊的數(shù)量應(yīng)該盡量少等,。

3 FPGA動態(tài)部分重構(gòu)的實(shí)現(xiàn)

在本設(shè)計(jì)實(shí)例中,,F(xiàn)PGA實(shí)現(xiàn)的功能是對外圍接口電路進(jìn)行邏輯控制以及根據(jù)外圍不同設(shè)備輸入的數(shù)據(jù)選擇適當(dāng)?shù)臄?shù)據(jù)處理算法。據(jù)此將設(shè)計(jì)劃分為固定模塊和可重構(gòu)模塊,,其中固定模塊內(nèi)實(shí)現(xiàn)對外接口的控制邏輯,,可重構(gòu)模塊內(nèi)實(shí)現(xiàn)數(shù)據(jù)處理算法。本例中只將FPGA的邏輯功能更換一次,,即可重構(gòu)模塊只部分重構(gòu)一次,,將其在重構(gòu)前后的不同邏輯功能分別計(jì)作reconfig_a和reconfig_b。系統(tǒng)會根據(jù)需要動態(tài)部分重構(gòu)FPGA,,為不同的數(shù)據(jù)源選擇適合的處理方法,。本設(shè)計(jì)由Virtex-E XCV600E器件來實(shí)現(xiàn),。

根據(jù)模塊所需資源的大小和模塊劃分原則,在用戶約束文件(UCF)中將每個模塊的位置進(jìn)行約束,,如下所示:

INST "fix" AREA_GROUP = "AG_fix" ,;(1)

AREA_GROUP "AG_fix" RANGE = CLB_R1C1:CLB_R48C36 ;(2)

INST "reconfig" AREA_GROUP = "AG_reconfig" ,; (3)

AREA_GROUP "AG_reconfig" RANGE = CLB_R1C37:CLB_R48C72 ,;(4)

其中(2)、(4)指定了兩個模塊的具體位置,。

按照模塊化設(shè)計(jì)流程,,分別對固定模塊fix和可重構(gòu)模塊reconfig_a和reconfig_b進(jìn)行設(shè)計(jì)綜合,,再將兩個可重構(gòu)模塊分別和固定模塊進(jìn)行組合,,完成整體設(shè)計(jì)。此過程中可重構(gòu)模塊和FPGA的整個設(shè)計(jì)分別生成配置比特流,。

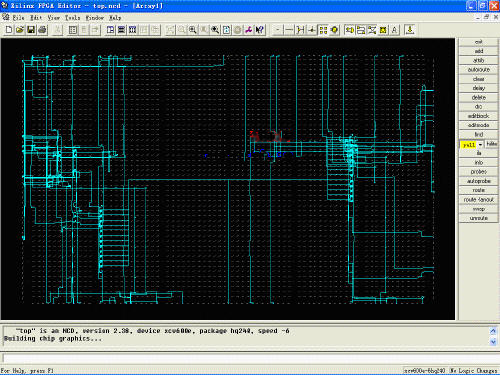

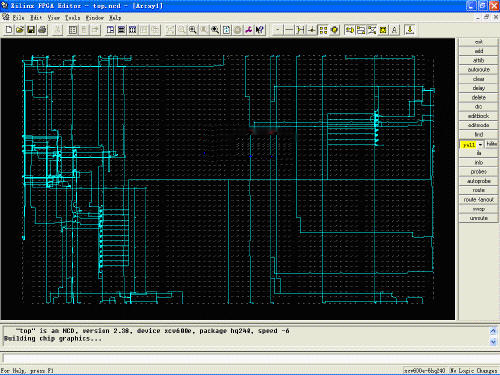

圖3和圖4是FPGA部分重構(gòu)前后的整個設(shè)計(jì)的物理實(shí)現(xiàn),,圖中左半部分為固定模塊區(qū)域,右半部分為可重構(gòu)模塊區(qū)域,。從兩圖中可知在部分重構(gòu)前后可重構(gòu)模塊區(qū)域內(nèi)布線發(fā)生變化,,而固定模塊區(qū)域內(nèi)布線沒有發(fā)生變化。

圖3 fix和reconfig_a整體設(shè)計(jì)的物理實(shí)現(xiàn)結(jié)果

圖4 fix和reconfig_b整體設(shè)計(jì)的物理實(shí)現(xiàn)結(jié)果

FPGA動態(tài)部分重構(gòu)時首先須將整個配置文件下載到器件中,,重構(gòu)時系統(tǒng)根據(jù)運(yùn)行的需要選擇適合的部分重構(gòu)配置比特流,。Virtex-E XCV600E配置比特流的大小為495204個字節(jié),而可重構(gòu)模塊reconfig_a和reconfig_b配置比特流的大小分別為93324個字節(jié)和111868個字節(jié),,因此采用部分重構(gòu)不僅能夠在運(yùn)行不間斷的情況下更新可重構(gòu)模塊區(qū)域內(nèi)的邏輯功能,,而且也能使重構(gòu)配置時間大大減少。

3 結(jié)論

本文以Xilinx FPGA為研究對象,,介紹了采用模塊化設(shè)計(jì)實(shí)現(xiàn)FPGA動態(tài)部分重構(gòu)功能的方法,。FPGA的動態(tài)部分重構(gòu)功能使硬件設(shè)計(jì)更加靈活,可以將不同設(shè)計(jì)定位到芯片內(nèi)同一邏輯資源部分,,重構(gòu)此部分邏輯資源,,同時保持其他部分電路功能正常,從而靈活快速的改變系統(tǒng)設(shè)計(jì),,能夠減少器件的花費(fèi),,降低功耗、更有效的利用電路板空間,,可以應(yīng)用于系統(tǒng)實(shí)時容錯,、自適應(yīng)硬件算法等。

本文作者創(chuàng)新點(diǎn):基于FPGA動態(tài)可重構(gòu)技術(shù)將設(shè)計(jì)從一個純空間的數(shù)字邏輯系統(tǒng)轉(zhuǎn)換為在時間,、空間混合構(gòu)建的數(shù)字邏輯系統(tǒng),。這種技術(shù)是數(shù)字系統(tǒng)設(shè)計(jì)方法,、設(shè)計(jì)思想的變革,使FPGA資源利用率成倍提高,。目前我國在FPGA可重構(gòu)技術(shù)方面開展的研究很少,。本論文闡述了采用模塊化設(shè)計(jì)實(shí)現(xiàn)FPGA動態(tài)部分重構(gòu)的方法,能夠使FPGA部分邏輯功能重新配置過程中,,其余部分邏輯功能正常運(yùn)行,,即實(shí)現(xiàn)了FPGA邏輯功能的動態(tài)部分重構(gòu)。