引 言

FPGA動態(tài)局部可重構(gòu)技術(shù)是指允許可重構(gòu)的器件或系統(tǒng)的一部分進行重新配置,,配置過程中其余部分的工作不受影響。動態(tài)局部可重構(gòu)縮短了重構(gòu)的時間,,減少了系統(tǒng)重構(gòu)的開銷,,提高了系統(tǒng)的運行效率。局部動態(tài)可重構(gòu)技術(shù)中通常將系統(tǒng)劃分為固定模塊和可重構(gòu)模塊,??芍貥?gòu)模塊與其他模塊之間的通信(包括可重構(gòu)模塊和固定模塊之間、可重構(gòu)模塊和可重構(gòu)模塊之間)都是由總線宏實現(xiàn)的,。

動態(tài)可重構(gòu)技術(shù)在FPGA中的實現(xiàn)是Xilinx公司首先提出的,,并且提供了相應(yīng)的開發(fā)工具和開發(fā)流程。他們從Virtex系列器件開始支持動態(tài)可重構(gòu)技術(shù),,同時他們提供了現(xiàn)成的總線宏文件給動態(tài)可重構(gòu)系統(tǒng)開發(fā)者使用,,但是它們提供的總線宏設(shè)計與軟件版本的兼容性很差。Xilinx提供的總線宏可能因為軟件版本的問題會無法正常使用,,所以用戶需要借助正在使用的版本軟件設(shè)計總線宏,,以實現(xiàn)FPGA動態(tài)局部可重構(gòu)設(shè)計。

在研究總線宏的結(jié)構(gòu)基礎(chǔ)上,,采用FPGA Editor可視化的方法設(shè)計基于TBUF的總線宏,,并通過FP-GA動態(tài)可重構(gòu)實驗驗證了該方法的正確性。

1 基于TBUF的總線宏結(jié)構(gòu)

在不同系列的Xilinx FPGA器件中,,使用不同的總線宏來實現(xiàn)動態(tài)局部可重構(gòu)技術(shù),。在Virtex,Virtex-E,,Virtex-ⅡPro X,,Spartan-Ⅱ,Spartan-ⅡE和Spartan-3系列器件中所使用的總線宏都是基于TBUF的,,可重構(gòu)模塊的位置固定不變,;在Virtex4,Virtex5更高性能的器件中,所使用的總線宏是基于Slice的,,可重構(gòu)模塊的位置是可變的,;而Virtex-Ⅱ,Virtex-ⅡPro所使用的總線宏既可以基于TBUF,,也可以基于Slice,。

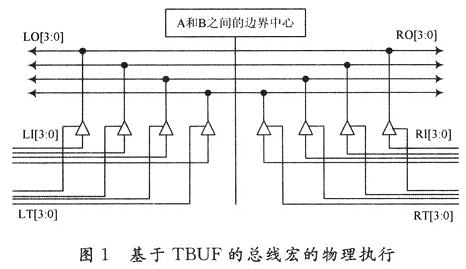

目前,使用最多的總線宏,,其物理實現(xiàn)是使用6個三態(tài)緩沖器(TBUF),,實現(xiàn)4位的雙向通信。每個TBUF占用1位,,每位使用1根TBUF長線,從FPGA的最左側(cè)到最右側(cè),,如圖1所示,。TBUF的T端是三態(tài)使能端口;I端是數(shù)據(jù)輸入端口,;O是數(shù)據(jù)輸出端口,。相應(yīng)地,總線宏的T端(LT和RT)是方向控制端口,,控制總線宏從左或從右輸出,;I端(LI和RI)是數(shù)據(jù)輸入端口;O端(LO和RO)是數(shù)據(jù)輸出端口,。

總線宏的信息通信是雙向的,,既可以從左到右,也可以從右到左,。但是對于一個設(shè)計來說,,一旦信息通信方向確定以后就不能再改變??偩€宏的位置精確地跨騎在模塊A和模塊B之間(A或B是可重構(gòu)模塊,,或AB全是可重構(gòu)模塊),其中四柵三態(tài)緩沖器在模塊A內(nèi),,另外四柵在B內(nèi),。對于Virtex-Ⅱ等系列器件,因內(nèi)部結(jié)構(gòu)不同,,故兩柵跨騎在模塊A內(nèi),,另外兩柵跨騎在模塊B內(nèi)。

2 基于TBUF的總線宏設(shè)計

這里在深入研究Xilinx公司所提供的總線宏的基礎(chǔ)上,,結(jié)合宏的設(shè)計技術(shù),,完善了總線宏的設(shè)計。

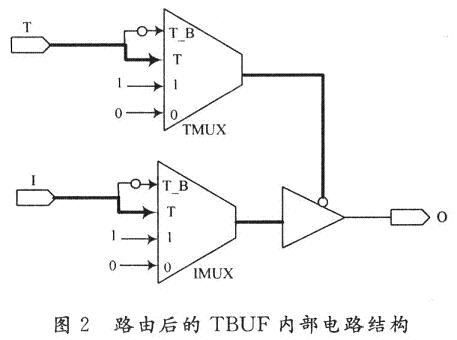

(1)TBUF的內(nèi)部路由。圖2給出內(nèi)部路由后的TBUF電路結(jié)構(gòu)圖,。TMUX的T端決定總線宏的控制端LT和RT高電平有效,,而T_B端決定低電平有效。

無論控制信號是高電平有效,,還是低電平有效,,在使用總線宏進行通信時,LT和RT的值必須是相反的,,或者是同時無效的,。例如,當(dāng)控制信號高有效時,,即T端為1時,,TBUF打開。如果總線宏是從左向右傳遞數(shù)據(jù),,則必須將LT設(shè)為1,,RT為0,反之亦然,;如果總線宏不需要傳遞數(shù)據(jù),,那么兩個控制信號應(yīng)同時為0,此時總線宏輸出為高阻態(tài),。

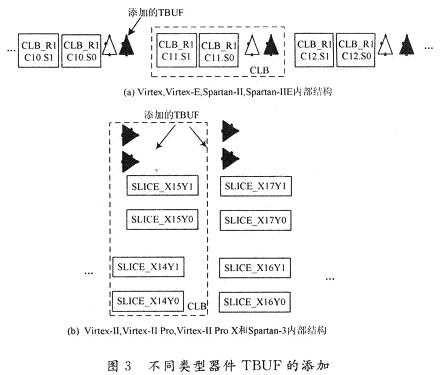

(2)TBUF添加的方法,。Virtex,Virtex-E,,Spar-tan-Ⅱ,,Spartan-ⅡE的內(nèi)部結(jié)構(gòu)類似,與TBUF添加的方法是相同的,。在相應(yīng)的位置選擇一個可編程邏輯塊(Configurable Logic Block,,CLB)中的一個TBUF作為總線宏的一個TBUF(1個CLB包含2個TBUF),依次選擇同一行相連下一個CLB中的一個TBUF,,直至選夠8個TBUF為止,;對于Spartan-3,Virtex-Ⅱ,,Virtex-ⅡPro和Virtex-ⅡPro X系列器件,;每一個CLB中的2個TBUF都作為總線宏的TBUF被選用,在同一行中依次選擇相連的4個CLB中的8個TBUF作為總線宏的TBUF,,如圖3所示,。

(3)TBUF外部端口的命名規(guī)則。根據(jù)圖1的總線宏結(jié)構(gòu),,對各個TBUF的外部端口T,,I和O進行相應(yīng)的命名,,命名時要符合所使用版本軟件的要求。例如,,若對端口進行如下命名:LI<3>,,LT<3>等,而端口在進行物理設(shè)計規(guī)則檢查(Design Rule Check,,DRC)時會出錯,,根據(jù)所提示的出錯信息將命名改為:LI(3),LT(3)等,,即能順利通過DRC,,完成端口的命名。

(4)總線宏輸出端口的定義,??偩€宏輸出端口的定義只能通過手工路由(Manual Route)方法,把相應(yīng)TBUF的輸出端口通過端口連線和TBUF長線連接起來,。