引言

傳統(tǒng)的定時(shí)器硬件連接比較復(fù)雜,可靠性差,而且計(jì)時(shí)時(shí)間短,難以滿(mǎn)足需要。本設(shè)計(jì)采用可編程芯片和VHDL語(yǔ)言進(jìn)行軟硬件設(shè)計(jì),不但可使硬件大為簡(jiǎn)化,而且穩(wěn)定性也有明顯提高。由于可編程芯片的頻率精度可達(dá)到50 MHz,因而計(jì)時(shí)精度很高。本設(shè)計(jì)采用逐位設(shè)定預(yù)置時(shí)間,其最長(zhǎng)時(shí)間設(shè)定可長(zhǎng)達(dá)99小時(shí)59分59秒。完全可以滿(mǎn)足用戶(hù)的需要,使用也更為方便。

1 系統(tǒng)原理

本定時(shí)器的核心器件為EP1C6Q240C8芯片。該芯片有選位、置位、啟動(dòng)、復(fù)位、倒計(jì)時(shí)等功能,顯示采用2個(gè)3位LED數(shù)碼管,并采用共陰接法,可以動(dòng)態(tài)掃描顯示。其系統(tǒng)原理如圖1所示。

2 硬件設(shè)計(jì)

本系統(tǒng)共有兩大模塊,分別為控制/定時(shí)模塊和顯示模塊。其中控制/定時(shí)模塊包括按鍵的功能定義和計(jì)時(shí)的邏輯定義。顯示模塊則包括片選模塊、位掃描模塊和數(shù)碼管譯碼模塊。

設(shè)計(jì)時(shí)可將秒信號(hào)輸入控制/定時(shí)模塊,此時(shí)系統(tǒng)將輸出六個(gè)四位BCD碼,以分別表示時(shí)、分、秒位。在預(yù)置數(shù)時(shí),計(jì)數(shù)器可以秒的速度遞增,從而實(shí)現(xiàn)逐位預(yù)置數(shù);而在定時(shí)倒計(jì)數(shù)時(shí),計(jì)數(shù)器可以秒的速度遞減,從而實(shí)現(xiàn)倒計(jì)時(shí)。系統(tǒng)中的位選擇器用于對(duì)六位進(jìn)行循環(huán)掃描輸出,并將掃描輸出送到譯碼器。譯碼器模塊可對(duì)輸入的四位進(jìn)行譯碼,同時(shí)在設(shè)置數(shù)值時(shí)用6個(gè)LED燈分別指示其所設(shè)置的位。

該系統(tǒng)硬件由兩部分組成,一部分是EPlC6Q240C8芯片,另一部分是按鍵,譯碼器,LED數(shù)碼管,發(fā)光二極管及可編程芯片的支持電路。圖2所示是其AAA控制定時(shí)模塊的引腳排列。其主要功能引腳的定義如下:

Setw(置位鍵):用于選定定時(shí)器所需定時(shí)的對(duì)應(yīng)位。發(fā)光二極管對(duì)應(yīng)七段數(shù)碼管設(shè)置,當(dāng)選定對(duì)應(yīng)的位時(shí),相應(yīng)的發(fā)光二極管亮;

Set(置數(shù)鍵):用于設(shè)置選定位的具體數(shù)值;

Start鍵:用于設(shè)定好時(shí)間后啟動(dòng)秒表計(jì)時(shí)。可通過(guò)軟件使start按鍵經(jīng)過(guò)鎖存器后進(jìn)人AAA模塊。Start觸發(fā)后可產(chǎn)生持續(xù)的高電平;

ALM(揚(yáng)聲器):可在計(jì)時(shí)結(jié)束時(shí)發(fā)聲報(bào)警;

Clr(清零鍵):用于計(jì)時(shí)器的清零復(fù)位;

七段數(shù)碼管用于顯示定時(shí)數(shù)字,set模塊用控制數(shù)碼管的掃描頻率。

3 主要模塊軟件程序

圖3所示是該定時(shí)器的軟件系統(tǒng)構(gòu)成。本軟件包括控制/定時(shí)模塊和顯示模塊兩大部分。

3.1 控制/定時(shí)模塊

AAA控制/定時(shí)模塊是該定時(shí)器的核心部分,該模塊的程序流程圖如圖4所示。

當(dāng)START為高電平時(shí),該定時(shí)器將進(jìn)入倒計(jì)時(shí)階段。當(dāng)CLK脈沖上升沿到來(lái)時(shí),計(jì)數(shù)以秒的速度減1,直到計(jì)時(shí)結(jié)束,使ALM位為高電平為止。CLR為復(fù)位端,可用來(lái)清零,通常采用異步復(fù)位方式。SETW用于選位,高電平有效。SET用于對(duì)選定的位進(jìn)行置數(shù),也是高電平有效。ALM輸出端將在定時(shí)結(jié)束時(shí)產(chǎn)生高電平。Q0~Q5為四位BCD碼輸出端口,主要用于顯示。

3.2 顯示模塊

通過(guò)XUAN模塊可完成BCD碼的轉(zhuǎn)化,再經(jīng)DISP模塊譯碼.然后輸出給七段數(shù)碼管。

(1)XUAN模塊

XUAN可產(chǎn)生四位BCD碼輸入,并從sel端輸出。該模塊的管腳圖如圖5所示。其源程序代碼如下:

(2)DISP模塊

DISP模塊主要用于譯碼,可定義七段數(shù)碼管顯示的數(shù)字。其源程序如下:

4 系統(tǒng)仿真及結(jié)果

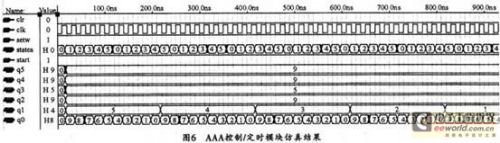

圖6所示是對(duì)AAA控制/定時(shí)模塊的仿真結(jié)果。由此結(jié)果可見(jiàn),當(dāng)setw置“1”時(shí),statea位選從0到5循環(huán),分別代表六個(gè)數(shù)碼管的位置。當(dāng)start置“1”時(shí),q5-q0進(jìn)行借位減法。q5、q4表示小時(shí),最高可到99小時(shí);q3、q2表示分鐘,最高59分鐘;q1、q0表示秒,最高為59秒。

5 結(jié)束語(yǔ)

本設(shè)計(jì)從總體要求出發(fā),采用模塊化設(shè)計(jì)方法,實(shí)現(xiàn)了長(zhǎng)達(dá)99小時(shí)的定時(shí)設(shè)計(jì)。同時(shí)采用QuartusⅡ4.0仿真環(huán)境進(jìn)行了仿真。結(jié)果證明,本系統(tǒng)可以實(shí)現(xiàn)理想的定時(shí)操作而且設(shè)計(jì)體現(xiàn)了人性化,具有較強(qiáng)的實(shí)際應(yīng)用價(jià)值。