摘? 要: 以DALSA 公司的CA-D7-1024T數(shù)字CCD相機為例,詳細討論了數(shù)字CCD相機的接口信號及其時序關(guān)系;研究了數(shù)字CCD相機圖像傳輸卡的關(guān)鍵技術(shù),介紹了傳輸卡的電路原理及各部分的實現(xiàn)方法。

關(guān)鍵詞: CCD相機? FPGA? 圖像數(shù)據(jù)" title="圖像數(shù)據(jù)">圖像數(shù)據(jù)傳輸卡? PCI總線

?

隨著CCD技術(shù)的發(fā)展,頻率高、數(shù)字化的新型CCD相機不斷出現(xiàn)。CCD相機輸出的數(shù)字化,簡化了相機與傳輸采集系統(tǒng)的接口設(shè)計,使數(shù)字CCD相機正越來越多地成為實時PCI控制、數(shù)據(jù)采集、圖形圖像處理、遙感遙測等系統(tǒng)中的探測器。這種CCD相機多采用幀轉(zhuǎn)移型體系結(jié)構(gòu),轉(zhuǎn)換速度快,量化精度、量子效率高。準確理解相機的接口信號及其時序關(guān)系,掌握其圖像數(shù)據(jù)傳輸卡的原理及實現(xiàn)方法,可大大拓寬數(shù)字CCD相機的應(yīng)用領(lǐng)域,提高應(yīng)用系統(tǒng)" title="應(yīng)用系統(tǒng)">應(yīng)用系統(tǒng)的靈活性。

1 數(shù)字CCD相機及其接口技術(shù)

在本系統(tǒng)中使用DALSA公司生產(chǎn)的CA-D7-1024T數(shù)字CCD相機。該相機是一種幀轉(zhuǎn)移型的CCD相機,相機的空間分辨力為1024×1024像元,單像元尺寸為12μm×12μm,100%填充因子。在相機內(nèi)部采用了相關(guān)雙采樣(CDS)、垂直反暈(VAB)等技術(shù),大大提高了相機的成像品質(zhì)。相機輸出經(jīng)過采樣、量化的數(shù)據(jù),量化精度為12位,最大" title="最大">最大幀頻為8.4Hz,電子快門。相機內(nèi)部由CCD圖像傳感器、驅(qū)動器、定時器、A/D轉(zhuǎn)換等模塊組成。其接口信號分為兩類:用戶總線接口信號和數(shù)據(jù)總線接口信號。

用戶總線接口信號包括:

·EXSYNC:觸發(fā)幀讀出信號,是必備信號。當EXSYNC固定接低電平時,相機以最大幀速率輸出圖像數(shù)據(jù);當EXSYNC正負交替 時,它的下降沿觸發(fā)幀讀出。

·PRIN:像元復(fù)位信號,為可選信號。在兩次EXSYNC有效之間復(fù)位像元(給積累電荷的電容放電),從而縮短有效曝光時間。PRIN低有效,在其上升沿開始有效曝光。如果PRIN固定接高電平" title="高電平">高電平,積分時間最大;如果PRIN被固定接低電平,探測器收集不到任何圖像信息。

·BIN:像元合并信號,也是可選信號,可以控制像元合并。像元合并后會降低相機的空間分辨率,但會增強探測器對光的敏感性。BIN信號高有效,不用時將其接為低電平。

以上信號均由應(yīng)用系統(tǒng)產(chǎn)生,送給相機,為應(yīng)用系統(tǒng)根據(jù)需要設(shè)定相機的工作模式提供了手段。

數(shù)據(jù)總線接口信號為相機輸出信號,包括:

·DATA0~11:12位數(shù)據(jù)總線。DATA0~11是相機輸出的、分別對應(yīng)目標某個像元灰度的12位圖像數(shù)據(jù)。

·STROBE:像元時鐘信號。STROBE是圖像數(shù)據(jù)的像元時鐘。它的頻率與數(shù)據(jù)速率相同,即使數(shù)據(jù)無效,STROBE仍然連續(xù)交變。為了獲得有效的圖像數(shù)據(jù),傳輸卡應(yīng)在FVAL和LVAL為高電平時,在STROBE的下降沿進行數(shù)據(jù)鎖存。

·FVAL:幀同步信號。FVAL高電平表明相機正輸出一幀有效數(shù)據(jù)。

·LVAL:行同步信號。當FVAL為高電平時,LVAL高電平表明相機正輸出一個有效的像元行。在兩個有效行之間,LVAL會變低跳過幾個無效的像元,跳過的像元數(shù)取決于相機的型號和預(yù)觸發(fā)設(shè)定。

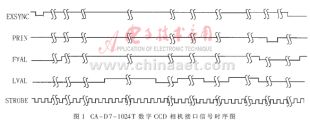

圖像數(shù)據(jù)傳輸卡正是利用這些接口信號來實現(xiàn)對相機的控制及圖像數(shù)據(jù)的抓取操作。為提高信號的抗干擾能力,所有這些接口信號均按RS422規(guī)范,以差分方式在數(shù)字相機和圖像傳輸卡間進行傳輸,傳輸電纜為100Ω屏蔽雙絞線。圖1表示了相機接口信號之間的時序關(guān)系。

?

?

當PRIN由低電平向高電平跳變時,相機開始曝光。達到設(shè)定的曝光時間后,使EXSYNC信號變低,觸發(fā)幀讀出。此時相機首先進行幀轉(zhuǎn)移,幀轉(zhuǎn)移一結(jié)束,輸出信號FVAL由低變高表示有效的數(shù)據(jù)幀開始,LVAL由低變高表示相機正輸出有效像元行。當FVAL和LVAL再一次變低時,表示一幀數(shù)據(jù)輸出結(jié)束,可以開始第二次觸發(fā)幀讀出(使EXSYNC有效)。第二次曝光可在第一次幀轉(zhuǎn)移結(jié)束后與第二次幀讀出啟動前這段時間進行,曝光時間在一定范圍內(nèi)可調(diào)。

2 數(shù)字CCD相機圖像數(shù)據(jù)傳輸卡的設(shè)計實現(xiàn)

在應(yīng)用系統(tǒng)中,數(shù)字CCD相機圖像數(shù)據(jù)傳輸卡的主要任務(wù)是產(chǎn)生相機工作所需的輸入信號,解譯相機的輸出信號,使相機在電控方式下工作,并實時、正確地抓取相機輸出的圖像數(shù)據(jù),在相機和計算機內(nèi)存之間建立硬件傳輸通道。為了適應(yīng)數(shù)字CCD相機數(shù)據(jù)傳輸速率的不斷提高,早期基于ISA總線的圖像數(shù)據(jù)傳輸卡正逐步向基于PCI總線的傳輸卡過渡。

2.1 圖像數(shù)據(jù)傳輸卡電路說明

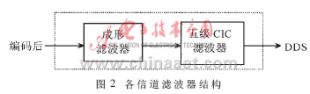

筆者設(shè)計開發(fā)的適用于DALSA公司CA-D7-1024T型數(shù)字CCD相機的圖像傳輸卡的原理框圖如圖2所示。

?

?

驅(qū)動轉(zhuǎn)換接口電路對相機與傳輸卡間的接口信號進行RS422和TTL電平間的相互轉(zhuǎn)換;雙口RAM為幀存儲器,經(jīng)編程控制可將相機輸出的一幀圖像數(shù)據(jù)寫入,或經(jīng)PCI橋讀出圖像數(shù)據(jù)至內(nèi)存。采用幀存儲器可以實現(xiàn)多個相機同時曝光,圖像數(shù)據(jù)分時通過計算機總線寫入內(nèi)存。FPGA時序發(fā)生器用來產(chǎn)生雙口RAM的地址線、讀寫控制線以及相機和傳輸卡正常工作所需的聯(lián)絡(luò)信號。PCI接口芯片是計算機與雙口RAM及FPGA間的橋梁,在它們之間實現(xiàn)數(shù)據(jù)、控制信號" title="控制信號">控制信號的傳輸,并可通過初始化設(shè)置,實現(xiàn)PCI協(xié)議提供的各種傳輸模式。

2.2? FPGA時序邏輯發(fā)生器設(shè)計

本圖像數(shù)據(jù)傳輸卡采用ALTRA公司生產(chǎn)的FPGA芯片EPM7128SLC84-15作為時序邏輯發(fā)生器。通過在系統(tǒng)編程(ISP)使其實現(xiàn)一個20位計數(shù)器、一個1位計數(shù)器、兩個鎖存器及十幾個非標邏輯門的功能。其中20位計數(shù)器給1M×4Bit的幀存儲器提供地址;1位計數(shù)器用來對卡上的30MHz時鐘信號進行二分頻,產(chǎn)生15MHz的VCLK信號;兩個鎖存器分別輸出行同步和場同步信號;邏輯門用來實現(xiàn)信號的與、或、非等邏輯運算。

ALTERA公司的MAX+PLUSⅡ編程仿真工具軟件,可對FPGA芯片進行在系統(tǒng)編程、仿真、調(diào)試,大大提高了傳輸卡設(shè)計的靈活性和對不同型號相機的適應(yīng)能力,縮短了傳輸卡的研發(fā)周期。使用AHDL編程語言對FPGA芯片進行在系統(tǒng)編程,程序文件的主體如下:

BEGIN

??? HSYNC = lpm_ff_component2.q[0..0];

????????????? lpm_ff_component2.clock = FVALT&STROBT&LVALT!GP5) # GP5&VCLK;

????????????? lpm_ff_component2.data[0..0] = HSYNN;

????????????? ??? VSYNC = lpm_ff_component3.q[0..0];

????????????? lpm_ff_component3.clock = FVALT&STROBT&LVALT&

???????????????????? (!GP5) # GP5&VCLK;

????????????? lpm_ff_component3.data[0..0] = VSYNN;

?????? ??? STROO = FVALT&STROBT&LVALT&(?選GP5);

??? A[19..0] = lpm_counter_component.q[19..0];

??? lpm_counter_component.aclr = sclr;

????????????? lpm_counter_component.clock=FVALT&STROBT&LVALT&

???????????????????? (!GP5) # GP5&VCLK;

??? /WE = !(FVALT&LVALT&?選STROO) ;

??? /OE = FVALT;

??? FVTA = FVALT;

??? /FVTA = !FVALT;

??? VCLK = lpm_counter_component1.q[0..0];

??? lpm_counter_component1.clock = VVCLK;

??? VVCLK = CLK & GP5;

??? 2VCLK = VVCLK;

??? F1 = A19&GP5;

??? HSYNN =A5&A6&A7&A8&A9&GP5;

??? VSYNN =A14&A15&A16&A17&A18&GP5;

??? END;

2.3 多層高速印制電路板設(shè)計

筆者研制的圖像數(shù)據(jù)傳輸卡的印制板設(shè)計為四層板,除了頂層和低層外,單獨設(shè)計了電源和地層,這是基于PCI總線板卡的基本要求。另外,由于卡上的數(shù)據(jù)、地址及控制信號多為高速信號,在進行印制板設(shè)計時,還必須注意以下幾點:

·PCI橋引腳的最大走線長度限于1.5英寸,CLK信號走線長度限于2.5±0.1英寸,且只連接一個負載;

·板上的共享PCI信號線的無負載特性阻抗(Z0)應(yīng)控制在60~100Ω;

·PCI控制信號應(yīng)考慮上拉電阻;

·每個電源引腳都要對地去耦合,處理開關(guān)電流的沖擊。一般跨接0.01μF高頻去耦電容;

·采集卡應(yīng)遵守最大引腳電容小于10pF的限制;

·共享的PCI信號在板上,只能帶一個負載。

在深入研究了數(shù)字CCD相機接口要求的基礎(chǔ)上,按照以上的設(shè)計原理,自行研制成功基于PCI總線的、適用于多相機同時曝光的圖像數(shù)據(jù)傳輸卡。該卡在機載多波段偏振成像系統(tǒng)原理樣機中成功地通過了調(diào)試。測試數(shù)據(jù)表明,圖像數(shù)據(jù)傳輸卡能夠滿足系統(tǒng)的設(shè)計要求。

?

參考文獻

1 李貴山,戚德虎.PCI局部總線開發(fā)者指南.西安:西安電子科技大學(xué)出版社,2000

2 盧 毅,賴 杰.VHDL與數(shù)字電路設(shè)計.北京:科學(xué)出版社,2001

3 CA-D4 and CA-D7 Camera User's Manual. rev 03. printed,1999