1.引言

隨著大規(guī)模集成電路和單片機(jī)的迅速發(fā)展,復(fù)雜可編程邏輯器件(CPLD)具有使用靈活、可靠性高、功能強(qiáng)大的優(yōu)點(diǎn),在電子產(chǎn)品設(shè)計(jì)中得到了廣泛的應(yīng)用。CPLD可實(shí)現(xiàn)在系統(tǒng)編程,重復(fù)多次,而且還兼容IEEE1149.1(JTAG)標(biāo)準(zhǔn)的測試激勵端和邊界掃描能力,使用CPLD器件進(jìn)行開發(fā),不僅可以提高系統(tǒng)的集成化程度、可靠性和可擴(kuò)充性,而且大大縮短產(chǎn)品的設(shè)計(jì)周期。由于CPLD采用連續(xù)連接結(jié)構(gòu),易于預(yù)測延時,從而使電路仿真更加準(zhǔn)確。CPLD是標(biāo)準(zhǔn)的大規(guī)模集成電路產(chǎn)品,可用于各種數(shù)字邏輯系統(tǒng)的設(shè)計(jì)。近年來,隨著采用先進(jìn)的集成工藝和大批量生產(chǎn),CPLD 器件成本不斷下降,集成密度、速度和性能都大幅度提高,這樣一個芯片就可以實(shí)現(xiàn)一個復(fù)雜的數(shù)字電路系統(tǒng);再加上使用方便的開發(fā)工具,給設(shè)計(jì)修改帶來很大方便。本文以Xilinx公司的CoolRunner系列CPLD芯片為例,實(shí)現(xiàn)對水下爆炸時沖擊波信號數(shù)據(jù)的記錄。

2 水下沖擊波記錄儀的組成及工作原理

2.1 功能介紹

該水下沖擊波記錄儀電路主要用于測試水下爆炸時沖擊波的強(qiáng)弱,通過專用數(shù)據(jù)處理軟件它能夠?qū)Σ杉降臎_擊波信號的數(shù)據(jù)進(jìn)行波形重現(xiàn), 并從波形上可讀出沖擊波的壓力峰值及其上升時間和作用時間。

2.2 體系結(jié)構(gòu)組成

水下沖擊波記錄儀由數(shù)據(jù)記錄器、接口、測試數(shù)據(jù)處理軟件三部分組成。數(shù)據(jù)記錄器是一個集壓力傳感器、瞬態(tài)波形記錄器、接口、電源等于一體的微型測試裝置,內(nèi)置電壓放大器,直流供電,輸入信號經(jīng)放大、高速A/D轉(zhuǎn)換后實(shí)現(xiàn)自動數(shù)字存儲。

2.3 工作原理

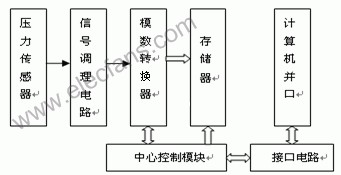

壓力傳感器的主要作用是敏感水下沖擊波的強(qiáng)弱,其輸出通過恒流源電路把沖擊壓力信號轉(zhuǎn)換為電壓信號。調(diào)理電路將信號轉(zhuǎn)換到模數(shù)轉(zhuǎn)換器的模擬量輸入范圍之后,由模數(shù)轉(zhuǎn)換器對其進(jìn)行采集,通過中心控制模塊對轉(zhuǎn)換后的數(shù)字信號的幅值進(jìn)行判斷并對存儲器地址進(jìn)行初始化、遞推,數(shù)字信號即被存儲。讀數(shù)時計(jì)算機(jī)通過并口發(fā)出讀數(shù)時鐘及命令,對三路存儲器進(jìn)行路選、片選并將其中的數(shù)據(jù)讀出。

記錄儀觸發(fā)方案采用負(fù)延遲內(nèi)觸發(fā):當(dāng)信號幅值大于或等于傳感器輸出滿量程的10%時啟動負(fù)延遲,而當(dāng)信號幅值小于此值時系統(tǒng)處于循環(huán)采集狀態(tài),從而可以有效地防止干擾引起的誤觸發(fā)與不觸發(fā)并準(zhǔn)確、完整地記錄整個沖擊波波形。水下沖擊波記錄儀的原理組成框圖見圖1。

圖1 水下沖擊波記錄儀工作原理圖

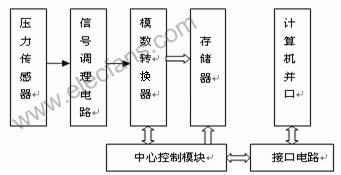

3 CPLD的應(yīng)用

在本設(shè)計(jì)中主要使用Xilinx公司開發(fā)的CoolRuner CPLD芯片完成設(shè)計(jì)。本文設(shè)計(jì)中所采用的是該系列中的XCR3256器件,可實(shí)現(xiàn)6000門的數(shù)字邏輯電路,內(nèi)嵌256個宏單元,支持4個全局時鐘,具有低功耗、可快速ISP、延時可預(yù)測等特點(diǎn)。我們選用XCR3256芯片實(shí)現(xiàn)水下沖擊波記錄儀主控模塊,該主控模塊用于對各外圍器件的控制,協(xié)調(diào)各外圍器件的工作。外圍器件主要有電源芯片組、靜態(tài)RAM存儲器、晶體振蕩器、A/D轉(zhuǎn)換器、LED、并口等。其中晶體振蕩器包括產(chǎn)生主時鐘的12MHz晶振和產(chǎn)生延時計(jì)數(shù)時鐘的1MHz晶振。主控模塊與各外圍器件的框圖如圖2所示。

圖2 水下沖擊波記錄儀主控模塊與各外圍器件電路原理框圖

3.1 靈活性強(qiáng),開發(fā)周期短

圖2中A/D轉(zhuǎn)換器采用AD7470。它的啟動轉(zhuǎn)換輸入端CONVST由主時鐘分頻得到且采樣頻率可編程。可編程延時電路是通過一個四路撥碼開關(guān)對CPLD輸入不同的電平組合實(shí)現(xiàn)的,通過設(shè)定CPLD數(shù)字邏輯對產(chǎn)生延時計(jì)數(shù)時鐘的1MHz晶振計(jì)數(shù),輸入不同的電平組合從而譯碼產(chǎn)生不同的延遲時間,而更改電平組合只需對記錄儀的面板操作即可。CPLD器件配以ISE開發(fā)系統(tǒng)可完成設(shè)計(jì)輸入、編譯、驗(yàn)證及編程,設(shè)計(jì)校驗(yàn)可進(jìn)行完整的模擬, 最壞情況下的定時分析和功能測試。設(shè)計(jì)人員無需編程器就可重構(gòu)數(shù)字系統(tǒng),具有“硬件軟做”的特點(diǎn)。

3.2 功耗低,集成度高

圖2中電源管理電路中的電源芯片主要包括MAX1658、MAX1659和MAX1616,它們的共同點(diǎn)就是都有一個SHDN輸入端,當(dāng)SHDN端為低電平時,無論電壓輸入端輸入多大電壓,輸出電壓均為0V,而只有當(dāng)SHDN端為高電平,輸入端接入合適電壓時,輸出端才能產(chǎn)生相應(yīng)的電壓值供系統(tǒng)正常工作。由于裝置最終工作在水下,需要電池供電,這就要求電路必須低功耗。

記錄儀工作時共有5個狀態(tài):低功耗延時設(shè)置待上電狀態(tài)、低功耗待觸發(fā)狀態(tài)、數(shù)據(jù)記錄狀態(tài)、數(shù)據(jù)保持狀態(tài)、讀出數(shù)據(jù)狀態(tài)。狀態(tài)的轉(zhuǎn)換是在中心控制模塊的控制之下完成的。系統(tǒng)自帶了一個數(shù)據(jù)保持電源,因此不用時系統(tǒng)處于數(shù)據(jù)保持狀態(tài)。主控模塊上電以后,通過四路撥碼開關(guān)設(shè)置延時時間,延時時間到了之后其它模塊自動上電,處于待觸發(fā)狀態(tài),準(zhǔn)備對數(shù)據(jù)進(jìn)行采集。隨著觸發(fā)信號的到來,系統(tǒng)狀態(tài)被轉(zhuǎn)換至數(shù)據(jù)記錄狀態(tài),記錄完畢后,系統(tǒng)進(jìn)入低功耗數(shù)據(jù)保持狀態(tài)等待被回收。取回裝置后,讀數(shù)時系統(tǒng)轉(zhuǎn)換為讀出數(shù)據(jù)狀態(tài),讀數(shù)結(jié)束后系統(tǒng)又處于數(shù)據(jù)保持狀態(tài),等待下一次記錄。這樣系統(tǒng)每記錄一次,其對應(yīng)的狀態(tài)就要循環(huán)一次。在系統(tǒng)工作的不同階段,我們可以通過CPLD內(nèi)部數(shù)字邏輯來控制各個電源芯片的SHDN輸入端,讓必須工作的芯片的SHDN輸入端置高,不需要工作的芯片的SHDN輸入端置低,從而實(shí)現(xiàn)了低功耗。

Xilinx器件的集成度范圍可達(dá)300~250000可用門,可以很容易地集成現(xiàn)有邏輯功能, 無論這些邏輯是由多個離散邏輯器件、多個PLD或是FPGA組成的,還是由幾個定制的器件組成的。在系統(tǒng)設(shè)計(jì)中,集成度提高意味著設(shè)備規(guī)模減小,元器件數(shù)量減小,而元器件數(shù)量減小就必然降低功耗,特別是嵌入式陣列塊(EAB)的使用,可以把存儲器集成到CPLD芯片中,特別有利于芯片上系統(tǒng)的設(shè)計(jì),降低了系統(tǒng)的成本,設(shè)備功耗,而且能夠提高系統(tǒng)的性能和可靠性。

3.3 低成本,高可靠性

采用CPLD器件來進(jìn)行電路設(shè)計(jì), 可以大幅度地減少印制板的面積、焊點(diǎn)和接插件, 降低裝配和調(diào)試費(fèi)用。大量的分立器件在進(jìn)行印制板電裝時, 往往會發(fā)生由于虛焊或接觸不良而造成故障, 并且這種故障常常難以發(fā)現(xiàn), 給調(diào)試和維修帶來極大的困難。因此, 采用CPLD 器件后, 由于集成度提高, 元器件數(shù)量減少, 印制板數(shù)量減少, 因而分機(jī)組合減少, 降低設(shè)備的綜合成本, 使得設(shè)備的可靠性大大提高。

4 設(shè)計(jì)過程

Xilinx公司的CPLD開發(fā)工具ISE,支持多種輸入方式,給設(shè)計(jì)開發(fā)提供了極大的方便,因此本系統(tǒng)采用ISE進(jìn)行設(shè)計(jì)。它可以便捷地完成設(shè)計(jì)輸入、編輯、與校驗(yàn)工具連接,設(shè)計(jì)人員可以使用標(biāo)準(zhǔn)的EDA設(shè)計(jì)輸入工具來建立邏輯設(shè)計(jì),使用ISE編譯器對XCR3256器件進(jìn)行編譯,其設(shè)計(jì)流程如圖3。

4.1 設(shè)計(jì)輸入

設(shè)計(jì)輸入方式有原理圖輸入,硬件描述(HDL)語言輸入,波形輸入等多種方式。記錄儀電路的各個功能塊: 單向總線緩沖器的產(chǎn)生, A/D時鐘信號、寫信號及片選信號的產(chǎn)生,地址發(fā)生器的產(chǎn)生,讀、寫命令及數(shù)據(jù)的傳輸控制,對讀數(shù)時鐘的消抖等都是采用硬件描述語言(VHDL)來實(shí)現(xiàn)的,最后采用原理圖輸入把各個功能塊連接在一起。采用語言描述的優(yōu)點(diǎn)是效率較高, 結(jié)果也較容易仿真, 信號觀察較方便。

4.2 設(shè)計(jì)處理

分別在設(shè)計(jì)文件中讀取信息并產(chǎn)生編程文件和仿真文件及自動錯誤定位, 設(shè)計(jì)規(guī)則檢查以及各器件劃分,編譯器還能實(shí)現(xiàn)用戶指定的定時要求,例如:傳播延時(tPD),時鐘頻率(f osc)等。

圖3 設(shè)計(jì)流程

4.3 設(shè)計(jì)仿真

當(dāng)設(shè)計(jì)完成后, 設(shè)計(jì)者可以通過仿真來驗(yàn)證設(shè)計(jì)電路的特性是否和設(shè)計(jì)目的相一致, 這里是通過時序模擬來測試邏輯功能及器件最差情況下時間關(guān)系。通過仿真結(jié)果可以很直觀地觀察到結(jié)果是否符合設(shè)計(jì)要求。

4.4 器件編程

完成設(shè)計(jì)輸入和時序仿真操作后,最后一步就是對XCR3256器件進(jìn)行編程,用計(jì)算機(jī)通過Xilinx專用編程電纜進(jìn)行配置,編譯生成的配置文件經(jīng)計(jì)算機(jī)并行通信口接到Xilinx專用編程電纜上,再接到器件的編程接口,利用ISE開發(fā)系統(tǒng)提供的編程軟件即可對器件進(jìn)行配置。這種方法的優(yōu)點(diǎn)是配置方便、迅速,便于修改。這非常有利于電路的調(diào)試, 電路調(diào)試時經(jīng)常需要對電路設(shè)計(jì)劃分來逐步調(diào)試。通過更改設(shè)計(jì),可以對器件重新編程, 容易完成電路調(diào)試。

5 結(jié)束語

本文中介紹的水下沖擊波記錄儀主要用于測試水下爆炸時產(chǎn)生的沖擊波的強(qiáng)弱, 采用CPLD器件進(jìn)行設(shè)計(jì),大大提高了系統(tǒng)設(shè)計(jì)的靈活性,提高了系統(tǒng)的可靠性和集成度,縮短了產(chǎn)品研制的周期,同時還可以降低設(shè)計(jì)成本,節(jié)省PCB板的面積和布線難度,提高了設(shè)備可靠性,得到了滿意的試驗(yàn)結(jié)果。