0 引 言

隨著計算機與微電子技術(shù)的發(fā)展,電子設計自動化EDA領(lǐng)域已成為電子技術(shù)發(fā)展的主體,數(shù)字系統(tǒng)的設計正朝著速度快、容量大、體積小、重量輕的方向發(fā)展。推動該潮流發(fā)展的引擎,就是日趨進步和完善的CPLD(Complex Programmable Logic Device)設計技術(shù)。而電子設計自動化,是近幾年迅速發(fā)展起來的將計算機軟件、硬件、微電子技術(shù)交叉運用的現(xiàn)代電子設計學科,其中EDA設計語言中的 VHDL語言是一種快速的電路設計工具,功能涵蓋了電路描述、電路合成、電路仿真等三大電路設計工作。該數(shù)字電壓表的電路設計,正是用VHDL語言完成的。此次設計主要應用美國Altera公司自行設計的一種CAE軟件工具,即Max+PlusⅡ軟件。

1 數(shù)字電壓表的構(gòu)成及工作原理

數(shù)字電壓表是諸多數(shù)字化儀表的核心與基礎(chǔ)。以數(shù)字電壓表為核心擴展成的各種數(shù)字化儀表,幾乎覆蓋了電子電工測量、工業(yè)測量、自動化系統(tǒng)等各個領(lǐng)域。

1.1 數(shù)字電壓表

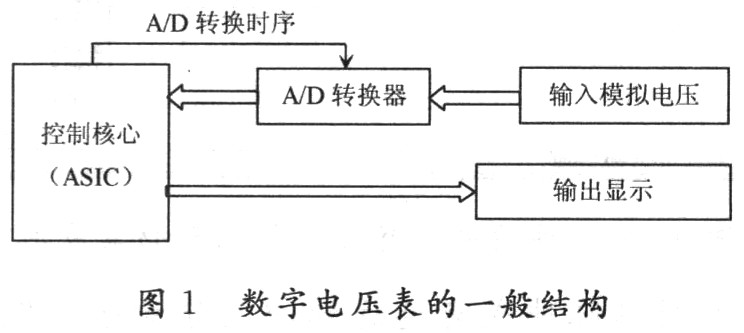

數(shù)字電子系統(tǒng)通常由ASIC芯片和外圍硬件設備組成,具有靈活性不強等缺陷。如圖1所示的數(shù)字電壓表,A/D轉(zhuǎn)換器在控制ASIC所提供的時序信號作用下,對輸入模擬信號進行轉(zhuǎn)換,控制核心再對轉(zhuǎn)換結(jié)果進行運算和處理,最后驅(qū)動輸出裝置顯示數(shù)字電壓信號。由于系統(tǒng)功能由ASID硬件結(jié)構(gòu)決定,其功能難以更新和擴展。如果用EDA方法設計,即以可編程邏輯器件CPLD代替ASIC芯片,用硬件描述語言決定系統(tǒng)功能,就可在硬件不變的情況下修改程序以更新和擴展功能,使其靈活性顯著提高。基于此考慮,用EDA方法設計了一個簡易數(shù)字電壓表控制電路,旨在研究提高數(shù)字電子系統(tǒng)靈活性的設計方法。

1.2 數(shù)字電壓表的工作原理

數(shù)字電壓表的改進結(jié)構(gòu)如圖2所示,它的硬件包括三個部分,其中轉(zhuǎn)換器ADC0804的作用是將模擬電壓信號轉(zhuǎn)換成數(shù)字電壓值,并送到CPLD以待運算和處理;七段數(shù)碼顯示器的作用是接收CPLD轉(zhuǎn)換后的BCD數(shù)據(jù)并顯示;CPLD兼有處理和協(xié)調(diào)作用,包括控制A/D轉(zhuǎn)換動作、接收A/D轉(zhuǎn)換結(jié)果及編碼、驅(qū)動顯示等作用。因此,CPLD可分為三個功能模塊,即控制模塊、計算模塊和顯示驅(qū)動模塊。

2 CPLD設計

由以上分析,數(shù)字電壓表的CPLD設計,適合于頂層電路與三個底層模塊相結(jié)合的設計方法,其中顯示驅(qū)動模塊有標準的七段顯示VHDL子程序可供調(diào)用。下面僅論述其余兩模塊的設計。

2.1 控制模塊的設計

該模塊的任務是,控制ADC0804的工作時序,可分為S0~S3四個連續(xù)的步驟或狀態(tài)。任務分別是:使ADC0804準備轉(zhuǎn)換(狀態(tài)S0)、轉(zhuǎn)換(狀態(tài) S1)、CPLD準備讀取轉(zhuǎn)換結(jié)果(狀態(tài)S2)、讀取轉(zhuǎn)換結(jié)果(狀態(tài)S3)。各狀態(tài)由CPLD輸出腳CS、WR、RD的不同電平組合確定,主要的VHDL 語句為:

2.2 計算模塊

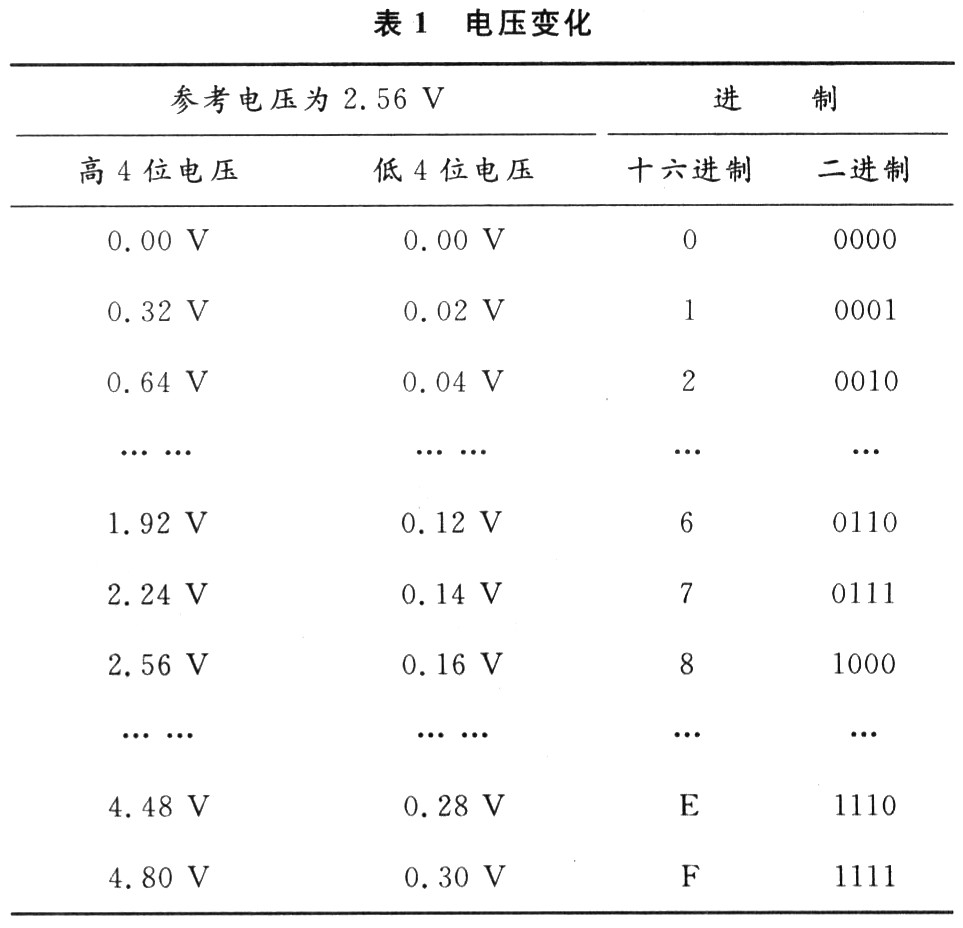

該模塊將A/D轉(zhuǎn)換結(jié)果分為高低4位,查表依次得到其BCD碼后再進行計算,計算結(jié)果與A/D轉(zhuǎn)換器的位寬和參考電壓Vref均有關(guān)。本文選用8位轉(zhuǎn)換器 ADC0804,參考電壓為5.12 V,故能輸出從0~5.12 V按照0.02 V步進變化的256(28)個離散值。如表1所示。

電壓離散值可用8位二進制(或2位十六進制數(shù))表示,表1中列出了輸出數(shù)字電壓高4位及低4位可能出現(xiàn)的16個值。如果CPLD從ADC20804接收到信號01101000B(即68H),對照表1高4位0110B是1.92 V,而低4位1000B是0.16 V,則最后的電壓輸出結(jié)果是1.92+0.16=2.08 V。

本文要求精確到兩位小數(shù)0.01 V,故將輸出電壓表示成12位的BCD碼形式。如上述的1.92 V是(000110010010)BCD,0.16 V是(000000010110)BCD,相加結(jié)果2.08 V是(001000001000)BCD。同理,若CPLD轉(zhuǎn)換數(shù)據(jù)01110000B(即70H),則計算結(jié)果2.24 V是(001000100100)BCD。因此計算模塊的設計主要包括一個12位的加法器及與之對應的存儲器。

主要VHDL語句如下:

3 仿真結(jié)果

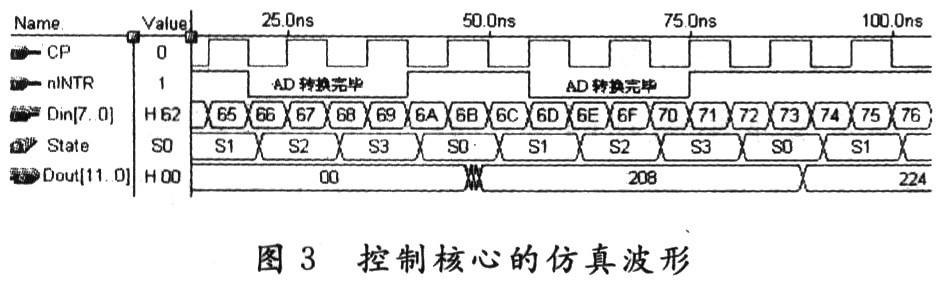

CPLD設計完成后,用Max+Plus II軟件編譯和仿真,波形如圖3所示。由圖3可知,CPLD工作時,先啟動控制模塊,它對模數(shù)轉(zhuǎn)換的一次控制由四個狀態(tài)組成。在狀態(tài)S0,選定 ADC0804,為模數(shù)轉(zhuǎn)換做準備;在狀態(tài)S1,使ADC0804進行轉(zhuǎn)換,當CPLD的INTR信號端由高電平轉(zhuǎn)為低電平時,模數(shù)轉(zhuǎn)換結(jié)束進入下一狀態(tài) S2,為讀取轉(zhuǎn)換結(jié)果做準備;在狀態(tài)S3,CPLD讀取模數(shù)轉(zhuǎn)換結(jié)果。接著,CPLD的計算模塊工作,求出二進制模數(shù)轉(zhuǎn)換數(shù)據(jù)的12位BCD碼。最后啟動顯示驅(qū)動模塊,用數(shù)碼管顯示有兩位小數(shù)的數(shù)字電壓值。例如,模數(shù)轉(zhuǎn)換結(jié)果即CPLD的輸入信號Din[7..0]若為68H,則輸出電壓 Dout[11..0]是2.08 V,Din[7..0]為70H時,輸出電壓Dout[11..0]是2.24 V,符合設計要求。

4 結(jié) 語

本文數(shù)字電壓表的功能由VHDL程序決定,用Max+Plus II軟件編譯、仿真和邏輯綜合后,下載到CPLD芯片EPF10K10LC84-4。CPLD工作主頻為100 MHz,邏輯綜合占用了174個邏輯單元,資源利用率為30%。本文所設計的數(shù)字電壓表電路板已通過硬件測試,能測量和顯示0~5 V的弱電壓信號,準確度為0.02 V,并已在我校EDA工程實訓中心測試成功。保持CPLD芯片不變,將輸入信號改為溫度信號、濕度等信號分別測試時,均能顯示相應的數(shù)字值,因此,基于這種設計方法的數(shù)字電子系統(tǒng)具有很強的靈活性。