1 引 言

信號源是雷達系統(tǒng)的重要組成部分,。雷達系統(tǒng)常常要求信號源穩(wěn)定,、可靠、易于實現(xiàn),、具有預失真功能,,信號的產生及信號參數(shù)的改變簡單,、靈活。本文采用DSP和CPLD來設計信號源的控制部分,,一方面能利用DSP軟件控制的靈活性,,另一方面又能利用CPLD硬件上的高速、高集成度和可編程性,。使用這種方法可以充分利用軟件支持來生成和加載任意波形數(shù)據(jù),,并能方便地實現(xiàn)對信號參數(shù)的控制和對波形數(shù)據(jù)的隨意修改,同時又能保證信號產生的高速,、靈活可控,。

2 系統(tǒng)結構

采用波形存儲直讀法,即通過對存儲的波形采樣數(shù)據(jù)進行數(shù)模變換,,直接生成模擬信號的一種方法,。圖1為信號源的系統(tǒng)結構。本信號源可工作于聯(lián)機和脫機兩種方式,。聯(lián)機工作時,,波形數(shù)據(jù)從微機加載,由DSP控制,,通過CPLD內的數(shù)據(jù)通道寫入SRAM,,經回讀、校驗后,,從SRAM內高速送入到數(shù)/模轉換器件產生雷達信號,。脫機工作時,波形數(shù)據(jù)可在系統(tǒng)上電時由EEPROM加載,,EEPROM中可存放一組波形數(shù)據(jù),,也可存儲多組數(shù)據(jù)以方便應用。

3 硬件實現(xiàn)

3.1 TMS320F206與EEPROM的接口設計

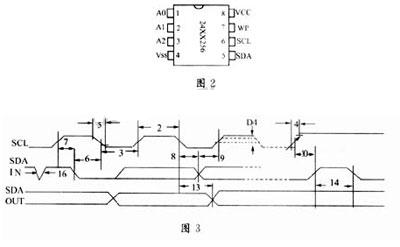

在實際系統(tǒng)中,,DSP采用TI公司的TMS320F206芯片,,EEPROM采用Microchip公司的24LC256 CMOS串行EEPROM(圖2)。TMS320F206屬于定點,、靜態(tài)CMOS數(shù)字信號處理器,。它采用先進的哈佛結構,具有片內外設,、片內存儲器及專用的運算指令集,,這些特點使得此器件使用靈活方便。24LC256工作電壓為2.5V~5.5V,,容量為32K×8bit,,為兩線串行接口總線,標準與I2CTM兼容。SCL為24LC256的時鐘輸入管腳,,SDA為其串行地址/數(shù)據(jù)輸入/數(shù)據(jù)輸出管腳,。24LC256提供讀順序地址內容的操作方式,其內部的地址指針在每次讀操作完成之后加1,,此地址指針允許在一次讀操作期間,,連續(xù)順序地讀出整個存儲器的內容。其時序如圖3所示,。

設計中將TMS320F206的通用I/O端口IO2模擬出SCL的時鐘,,IO3負責將數(shù)據(jù)寫入和從24LC256讀出(TMS320F206與24LC256的接口如圖1所示)。脫機工作時,,其流程如圖4,。

3.2 CPLD設計

可編程邏輯器件采用XILINX公司的CPLD,型號為XC95288XL-6TQ144C,。該器件為144-pin TQFP封裝,內部有288個宏單元,,最高工作時鐘為151MHz,。XC95288XL內部邏輯分為三部分:TMS320F206與微機接口的通信、高速地址計數(shù),、SRAM片選讀寫信號的產生,。

3.2.1 TMS320F206經過CPLD與微機接口的通信

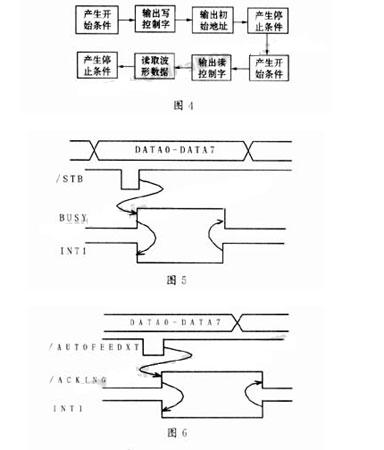

TMS320F206與微機接口的通信采用并行接口協(xié)議(EPP),主要完成從微機加載數(shù)據(jù)到SRAM,、將數(shù)據(jù)從SRAM回讀到微機,,整個過程對于并行接口來說采用查詢方式,對于TMS320F206來說采用中斷方式,。TMS320F206使用引腳接收由CPLD發(fā)出的中斷,,通過設置TMS320F206片內寄存器IRM與ICR,使TMS320F206響應中斷而不響應,。其時序如圖5和6所示,。

脫機工作狀態(tài)下,從并口加載數(shù)據(jù)時,,微機將數(shù)據(jù)發(fā)送到并口,,并發(fā)出低脈沖,CPLD接收STB到后,,置BUSY=1,,發(fā)出中斷信號,TMS320F206接收到中斷后,,控制CPLD鎖存數(shù)據(jù),,并將數(shù)據(jù)寫入SRAM,置BUSY=0;從并口回讀數(shù)據(jù)時,,微機設置并口為輸入狀態(tài),,然后發(fā)出AUTOFEEDXT低脈沖,CPLD接收到后,,置=1,,發(fā)出中斷信號給TMS320F206,TMS320F206控制CPLD從SRAM讀取數(shù)據(jù)并送到并口,,置=0,。