1,、前言

隨著計(jì)算機(jī)技術(shù)的高速發(fā)展,各工業(yè)發(fā)達(dá)國(guó)家投入巨資,,對(duì)現(xiàn)代制造技術(shù)進(jìn)行研究開(kāi)發(fā),,提出了全新的制造模式,其核心思想之一是柔性化制造,,制造系統(tǒng)能夠隨著加工條件的變化動(dòng)態(tài)調(diào)整,。目前,各類 MCU 快速發(fā)展,,它們不僅運(yùn)算速度快,、價(jià)格便宜、種類繁多,,而目不同M CU 針對(duì)不同的應(yīng)用在其片上集成了專用控制電路,,滿足了不同的應(yīng)用需求還提高了電路的安全性和穩(wěn)定性。綜合上述的分析與論證,,本文設(shè)計(jì)了一種基于DSP" title="DSP">DSP+CPLD" title="CPLD">CPLD 現(xiàn)場(chǎng)可編程門陣列器件的可重構(gòu)數(shù)控系統(tǒng)" title="數(shù)控系統(tǒng)">數(shù)控系統(tǒng),。

2、硬件設(shè)計(jì)

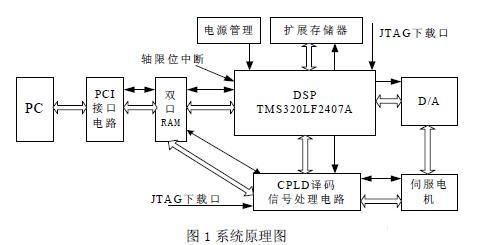

本運(yùn)動(dòng)控制卡是以PC 機(jī)作為主機(jī)的運(yùn)動(dòng)控制卡,,選用DSP 作為核心微處理器,,卡上集成編碼器信號(hào)采集和處理電路,D/A" title="D/A">D/A輸出電路,,擴(kuò)展存儲(chǔ)器電路和PC-DSP通訊電路,。PC機(jī)把粗處理的數(shù)據(jù)通過(guò)DSP-PC 通訊接口傳遞給運(yùn)動(dòng)控制系統(tǒng),DSP通過(guò)對(duì)光電編碼器反饋信號(hào)處理電路的結(jié)果分析,,計(jì)算出與給定位置的誤差值,,再通過(guò)軟件位置調(diào)節(jié)器獲得位置控制量,計(jì)算出運(yùn)動(dòng)速度控制量,,產(chǎn)生的輸出信號(hào)經(jīng)D/A 轉(zhuǎn)換將模擬電壓量送給伺服放大器,,通過(guò)對(duì)伺服電機(jī)的控制實(shí)現(xiàn)對(duì)位置的閉環(huán)控制。系統(tǒng)的結(jié)構(gòu)框圖如圖 1 所示,。

選用美國(guó)TI公司的16位定點(diǎn)DSP TMS320LF2407A" title="TMS320LF2407A">TMS320LF2407A作為本運(yùn)動(dòng)控制器的核心處理器,,地址譯碼、時(shí)序邏輯,、編碼器信號(hào)處理電路用CPLD來(lái)完成,,用PCI 接口芯片實(shí)現(xiàn)雙口RAM與PC 機(jī)的通訊,雙口RAM用來(lái)存儲(chǔ)和緩沖DSP與PC 機(jī)間的通訊數(shù)據(jù),SRAM用來(lái)存儲(chǔ)運(yùn)動(dòng)控制器運(yùn)行時(shí)的程序和數(shù)據(jù),。

(1).DSP外部中斷接口處理

對(duì)于數(shù)控機(jī)床來(lái)說(shuō),,由于受工作行程等各方面的限制,在其超過(guò)控制范圍時(shí),,引入包括限位中斷和編碼器INDEX 信號(hào)中斷,。每個(gè)控制軸有正反方向的兩個(gè)限位開(kāi)關(guān),,產(chǎn)生兩個(gè)限位信號(hào),,4 個(gè)軸共8 個(gè)限位信號(hào):LIMA+, LIMA -、LIMB +, LIMB -,、LIMC +, LIMC-,,LIMD+, LIMD -其中“+”表示正限位,“-”表示負(fù)限位,。這幾個(gè)信號(hào)通過(guò)CPLD 的相與之后接到DSP 的中斷管腳XINT1,,同時(shí)這些信號(hào)通過(guò)光藕電路接入DSP的I/O 口。當(dāng)運(yùn)動(dòng)到限位開(kāi)關(guān)處時(shí),,就會(huì)觸發(fā)DSP的外部中斷信號(hào)XINT1,,然后DSP就可以根據(jù)I/O 判定是哪個(gè)限位開(kāi)關(guān)超過(guò)工作范圍。8 個(gè)限位開(kāi)關(guān)分別接到DSP 的I/O 口,通過(guò)設(shè)置MCRA(地址:7090H),MCRB(地址:7092H)為零,,使這些復(fù)用管腳處于I/O 功能,。限位輸入信號(hào)的狀態(tài)可以從寄存器PADATDIR(地址:7098H )和PBDATDIR(地址:709AH)對(duì)應(yīng)的數(shù)據(jù)位讀取,對(duì)應(yīng)的數(shù)據(jù)方向位設(shè)為零,以使這些I/O 管腳工作在“輸入”狀態(tài)下,。編碼器的INDEX信號(hào)處理同上面相類似,。每個(gè)軸能產(chǎn)生一個(gè)INDEX 信號(hào),4 個(gè)軸有4個(gè)INDEX 信號(hào),。這4 個(gè)信號(hào)通過(guò)邏輯與門產(chǎn)生一個(gè)中斷信號(hào),,接到XINT2,同時(shí)接到DSP 的I/O 口,供中斷產(chǎn)生時(shí)DSP讀入,。

(2).四軸編碼器信號(hào)處理電路設(shè)計(jì)

四軸編碼器信號(hào)處理電路是對(duì)光電編碼器輸出的兩組相差90o 的方波信號(hào)的處理,,從而獲得執(zhí)行元件實(shí)際位置,其輸出是一路16 位的數(shù)字量,,反饋給中央處理器,,編碼器信號(hào)處理電路包括濾波,倍頻,,計(jì)數(shù)幾個(gè)功能模塊,,傳統(tǒng)的四軸編碼器信號(hào)處理電路采用分立元件來(lái)設(shè)計(jì),它可靠性,、抗干擾能力差,,應(yīng)用CPLD 設(shè)計(jì)了單片并行四軸編碼器信號(hào)處理電路。

它具有實(shí)時(shí)性好,硬件體積小,,工作效率高,,提高系統(tǒng)的集成度,相對(duì)于分立元件,,單片并行四軸編碼信號(hào)處理電路集成在一個(gè)片子上,,一方面單片芯片內(nèi)的門電路、觸發(fā)器的參數(shù)特性是完全一致的,,在相同轉(zhuǎn)速下脈沖信號(hào)的脈沖周期可以保持一致,。另一方面,電路做在單個(gè)芯片內(nèi),,抗干擾性能比分離器件構(gòu)成的電路也有很大的提高,,增強(qiáng)了系統(tǒng)的靈活性、通用性和可靠性,。本文設(shè)計(jì)是一個(gè)四軸伺服系統(tǒng),,因此有八路四組方波信號(hào),A 相B相相差90o,,CLR,,CLK,WE 分別為輸出清零,,系統(tǒng)時(shí)鐘和輸出使能,,SEL*是輸出選擇信號(hào),選擇X,,Y,,Z,A中的一組信號(hào)處理的結(jié)果作為輸出信號(hào),,分時(shí)送到數(shù)據(jù)總線,。

濾波模塊的設(shè)計(jì)

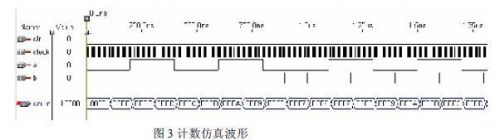

編碼盤理論上是穩(wěn)定的方波信號(hào),但在實(shí)際操作中,,經(jīng)常會(huì)存在脈動(dòng)干擾,,濾波模塊的功能是將這些脈動(dòng)干擾濾掉,降低系統(tǒng)產(chǎn)生誤動(dòng)作的可能性,,提高系統(tǒng)的可靠性,,下面的VHDL 程序通過(guò)對(duì)A,B 兩相方波信號(hào)同時(shí)延時(shí)四個(gè)CLK 脈沖,,,,脈沖寬度小于三個(gè)CLK脈沖周期的輸入信號(hào)被濾掉。仿真結(jié)果如圖:

倍頻計(jì)數(shù)模塊的設(shè)計(jì)

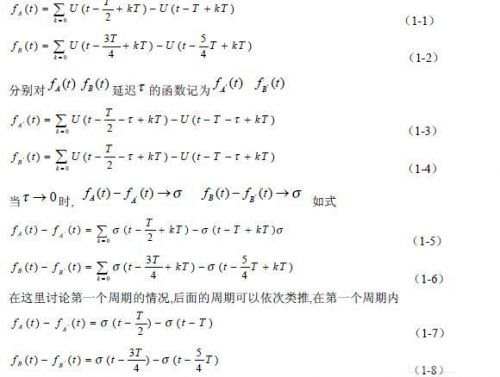

四倍頻電路的設(shè)計(jì)是為了增加計(jì)數(shù)脈沖在一個(gè)周期中的個(gè)數(shù),,來(lái)提高測(cè)量的分辨率,,工程中常把光電編碼器輸出的兩路方波信號(hào)的上升沿和下降沿,,來(lái)獲得四倍頻的脈沖信號(hào),把光電編碼器的分辨率提高四倍,,通過(guò)光電編碼器輸出兩路方波信號(hào)相差的正負(fù)來(lái)確定運(yùn)動(dòng)的方向,,對(duì)光電編碼器輸出信號(hào)A、B,;可以寫成:

如圖:

在一個(gè)周期內(nèi)產(chǎn)生的四倍頻計(jì)數(shù)脈沖輸出S,,方向判別信號(hào)J,通過(guò)一個(gè)16 位可逆計(jì)數(shù)就可以實(shí)現(xiàn)對(duì)伺服裝置的位置檢測(cè),,實(shí)現(xiàn)位置伺服控制系統(tǒng)的控制,。

3、控制算法的設(shè)計(jì)

?。?).控制模型

數(shù)控機(jī)床的最高運(yùn)動(dòng)速度,、跟蹤精度、定位精度等重要指標(biāo)均取決于驅(qū)動(dòng)及位置控制系統(tǒng)的動(dòng)態(tài)與靜態(tài)性能,。因此,研究與開(kāi)發(fā)高性能的驅(qū)動(dòng)系統(tǒng)及位置控制系統(tǒng),,一直是研究數(shù)控機(jī)床的關(guān)鍵技術(shù)之,。日前數(shù)控機(jī)床位置伺服控制仍然普遍應(yīng)用經(jīng)典控制方法,如比例型或比例一積分型等算法,,其優(yōu)點(diǎn)是算法簡(jiǎn)便,,易于實(shí)現(xiàn),但存在著控制參數(shù)的適應(yīng)性差,、抗十?dāng)_能力不強(qiáng)等缺陷,。為了適應(yīng)制造業(yè)對(duì)高效率地生產(chǎn)高質(zhì)量產(chǎn)品日標(biāo)的追求以及對(duì)形狀愈來(lái)愈復(fù)雜零件的加工需要,要求不斷地改善與提高位置伺服系統(tǒng)的穩(wěn)態(tài)精度,、動(dòng)態(tài)響應(yīng)特性,,對(duì)系統(tǒng)參數(shù)變化的自適應(yīng)性和抗干擾性,因而采用并發(fā)展先進(jìn)的控制技術(shù)是必然趨勢(shì),??上У氖牵壳疤岢龅闹T多控制算法中,,具有實(shí)用價(jià)值的技術(shù)極少,,主要表現(xiàn)在:①受算法計(jì)算量等限制,難以滿足控制的實(shí)時(shí)性要求;②控制理論在參數(shù)設(shè)計(jì)及穩(wěn)定性分析等方面不完善;③建模誤差對(duì)控制品質(zhì)的限制,。

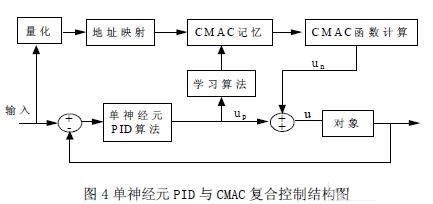

本文利用神經(jīng)網(wǎng)絡(luò)的自學(xué)習(xí)功能,,設(shè)計(jì)了一種在線單神經(jīng)元PID 與CMAC 并行控制智能型位置控制器,并將之用到數(shù)控系統(tǒng)的實(shí)時(shí)控制中,,取得了很好的控制效果,,控制模型結(jié)構(gòu)如圖:

?。?)仿真和實(shí)現(xiàn)

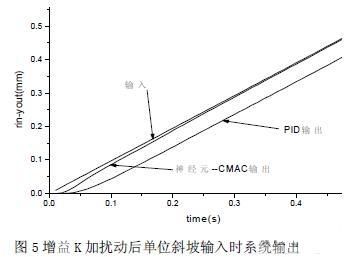

采用的單神經(jīng)元PID及CMAC 相結(jié)合的復(fù)合控制算法,完成對(duì)位置伺服控制器典型輸入斜坡輸入響應(yīng)的仿真實(shí)驗(yàn),。圖5 是位置伺服系統(tǒng)的單位斜坡輸入在輸入端加入10%的階躍擾動(dòng)后,,兩種控制算法的輸出曲線圖,通過(guò)對(duì)圖形的分析,,可以看出,,單神經(jīng)元PID 與CMAC相結(jié)合控制算法比常規(guī)PID 控制算法有更小的跟隨誤差,和更好的抗干擾能力,。這個(gè)在位置伺服控制系統(tǒng)中更為重要,。

4、結(jié)束語(yǔ)

利用計(jì)算控制功能強(qiáng)大的DSP 芯片構(gòu)建了數(shù)控系統(tǒng)平臺(tái),,應(yīng)用CPLD 解決了系統(tǒng)不同應(yīng)用場(chǎng)合邏輯電路變化的問(wèn)題,,從硬件上實(shí)現(xiàn)了可重構(gòu)性??刂扑惴ㄝ^常規(guī)PID 控制有更好的動(dòng)態(tài)特性,、控制精度、抗干擾能力,,而且具有自適應(yīng)功能,。該系統(tǒng)是一種開(kāi)放的系統(tǒng),可以使用戶很方便的不斷進(jìn)行軟,、硬件升級(jí),,一定時(shí)間內(nèi)跟上數(shù)控技術(shù)發(fā)展的步伐。