引 言

目前在電氣自動(dòng)化控制裝置中,廣泛采用各種通信手段以完成上層與底層控制器、底層控制器以及控制芯片之問的信息傳遞,并實(shí)現(xiàn)相應(yīng)的控制功能;各種通信功能的設(shè)計(jì)與實(shí)現(xiàn)已成為自動(dòng)化裝置設(shè)計(jì)的重要組成部分。本文以一種超聲波電機(jī)運(yùn)動(dòng)控制裝置為應(yīng)用背景,討論了基于CPLD的DSP控制芯片多SPI端口通信技術(shù)。

串行同步外設(shè)端口(SPI)通常也稱為同步外設(shè)端口,具有信號(hào)線少、協(xié)議簡(jiǎn)單、傳輸速度快的特點(diǎn),大量用在微控制器與外圍芯片的通信中。目前SPI通信方式已被普遍接受,帶有SPI端口的芯片越來越多,如Flash、RAM、A/D轉(zhuǎn)換、LED顯示、控制專用DSP芯片等。

本文介紹一種采用運(yùn)動(dòng)控制專用DSP芯片DSP56F801設(shè)計(jì)的超聲波電機(jī)運(yùn)動(dòng)控制裝置。由于該超聲波電機(jī)需要采用兩相四路對(duì)稱PWM信號(hào)來實(shí)現(xiàn)驅(qū)動(dòng)控制,而DSP芯片無法直接產(chǎn)生所需PWM信號(hào),采用軟件方法又會(huì)占用大量的DSP計(jì)算時(shí)間,于是設(shè)計(jì)了基于可編程邏輯器件(CPLD)的對(duì)稱PWM信號(hào)發(fā)生器。該信號(hào)發(fā)生器在DSP的控制下,可以實(shí)現(xiàn)輸出兩相PWM控制信號(hào)的占空比及相位差調(diào)節(jié);同時(shí)采用具有SPI接口的可編程振蕩器LTC6903,實(shí)現(xiàn)在DSP控制下的PWM控制信號(hào)頻率調(diào)節(jié)。由此可見,為了實(shí)現(xiàn)DSP對(duì)PWM控制信號(hào)占空比、相位差及頻率的控制,需要采用適當(dāng)?shù)耐ㄐ欧绞綄?shí)現(xiàn)DSP與CPLD及LTC6903之間的控制信息傳遞。DSP56F801芯片具有一個(gè)SPI通信端口。本文在分析SPI數(shù)據(jù)傳輸時(shí)序關(guān)系的基礎(chǔ)上,設(shè)計(jì)并實(shí)現(xiàn)了基于CPLD的多SPI接口通信。

1 工作原理

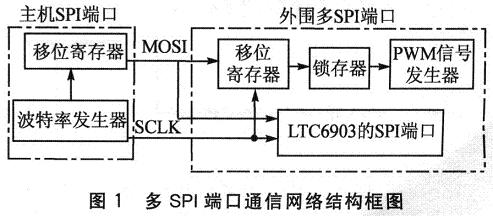

SPI是一個(gè)同步協(xié)議接口,所有的傳輸都參照一個(gè)共同的時(shí)鐘。在同一個(gè)SPI端口可以實(shí)現(xiàn)一個(gè)主機(jī)芯片與多個(gè)從機(jī)芯片的相連,這時(shí)主機(jī)通過觸發(fā)從設(shè)備的片選輸入引腳來選擇從設(shè)備,沒有被選中的從設(shè)備將不參與SPI傳輸。SPI主使用4個(gè)信號(hào):主機(jī)輸出/從機(jī)輸入(MOSI)、主機(jī)輸入/從機(jī)輸出(MISO)、串行時(shí)鐘信號(hào)SCLK和外設(shè)芯片選擇信號(hào)(SS)。主機(jī)和外設(shè)都包含一個(gè)串行移位寄存器,主機(jī)通過向它的SPI串行移位寄存器寫入一個(gè)字節(jié)來發(fā)起一次傳輸。寄存器是通過MOSI引腳將字節(jié)傳送給從設(shè)備,從設(shè)備也將自己移位寄存器中的內(nèi)容通過MISO信號(hào)線返回給主機(jī)。這樣,兩個(gè)移位寄存器中的內(nèi)容就被交換了。外設(shè)的寫操作和讀操作是同步完成的,因此SPI成為一個(gè)很有效的串行通信協(xié)議。SPI端口的通信網(wǎng)絡(luò)結(jié)構(gòu)框圖如圖1所示。為了使信號(hào)發(fā)生器輸出可調(diào)頻、調(diào)壓和調(diào)相輸出的兩相四路PWM波,需要DSP向CPLD電路輸出參數(shù)。這4個(gè)控制參數(shù)的傳遞是在小型的通信網(wǎng)絡(luò)中實(shí)現(xiàn)的。在該網(wǎng)絡(luò)中,DSP的SPI只是進(jìn)行數(shù)據(jù)輸出端口的寫操作,即輸出電壓控制字、相位控制字和頻率控制字。數(shù)據(jù)流程:主機(jī)DSP向CPLD傳輸數(shù)據(jù),在傳輸數(shù)據(jù)時(shí),數(shù)據(jù)在MOSI引腳上輸出,同時(shí)數(shù)據(jù)在時(shí)鐘信號(hào)的作用下實(shí)現(xiàn)同步移位輸出。由于不需要從機(jī)向主機(jī)回送任何數(shù)據(jù),主機(jī)在數(shù)據(jù)傳輸結(jié)束之后,結(jié)束這次傳送。由于SPI端口工作時(shí)沒有應(yīng)答信號(hào),并且數(shù)據(jù)在發(fā)送時(shí)無需校驗(yàn)位,所以要求主、從器件的數(shù)據(jù)發(fā)送與接收必須完全符合設(shè)定的SPI時(shí)序要求,否則數(shù)據(jù)傳輸將出現(xiàn)錯(cuò)誤。

2 基于CPLD的串口SPI設(shè)計(jì)

2.1 移位寄存器設(shè)計(jì)

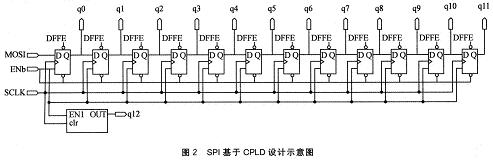

本設(shè)計(jì)為一個(gè)12位的SPI串行接收端口。圖1中移位寄存器是由12個(gè)D觸發(fā)器和1個(gè)計(jì)數(shù)器組成的,實(shí)現(xiàn)移位接收和串并轉(zhuǎn)換。在傳輸過程中,先使能移位寄存器和計(jì)數(shù)器,啟動(dòng)傳輸,同時(shí)計(jì)數(shù)器開始計(jì)數(shù)。當(dāng)計(jì)數(shù)到16時(shí),進(jìn)位端輸出一個(gè)脈沖寬度的高電平脈沖,進(jìn)行數(shù)據(jù)鎖存,其電路如圖2所示。

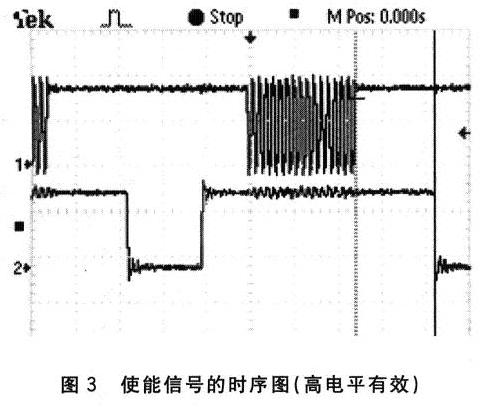

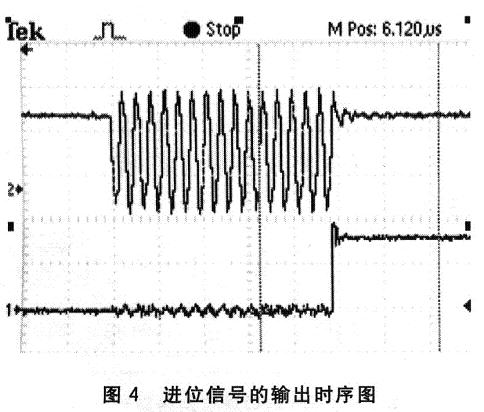

實(shí)驗(yàn)中為保證時(shí)序正確,測(cè)出了使能信號(hào)和計(jì)數(shù)器進(jìn)位脈沖的輸出時(shí)序,如圖3、圖4所示。其中十六進(jìn)制計(jì)數(shù)器采用的是上升沿計(jì)數(shù),在第16個(gè)上升沿到來時(shí),跳變?yōu)楦唠娖剑WC數(shù)據(jù)的正確接收鎖存。

2.2 鎖存器設(shè)計(jì)

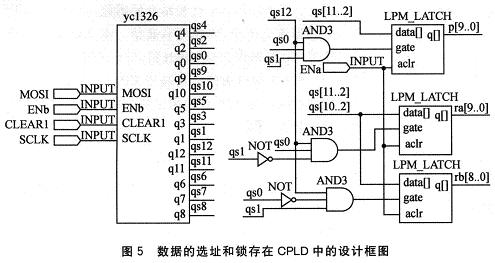

鎖存器的工作特點(diǎn):當(dāng)gate引腳上輸入高電平信號(hào)時(shí),鎖存器工作開始鎖存總線上的數(shù)據(jù);當(dāng)gate引腳上是低電平時(shí),鎖存器不工作,即當(dāng)總線上的數(shù)據(jù)發(fā)生變化時(shí),鎖存器的輸出不發(fā)生變化。由于本設(shè)計(jì)需要多個(gè)參數(shù)傳輸,通過地址選擇的方法把這3個(gè)數(shù)據(jù)從一條總線上區(qū)分出來,設(shè)置傳輸數(shù)據(jù)的低兩位為地址選擇位。地址選擇位經(jīng)移位寄存器,串并轉(zhuǎn)換,作為三輸入與門的兩個(gè)輸入端,進(jìn)行地址選擇。每次16位的數(shù)據(jù)移位結(jié)束,數(shù)據(jù)穩(wěn)定時(shí),在計(jì)數(shù)器高電平作用下,相應(yīng)gate的引腳上輸出高電平,數(shù)據(jù)鎖存入相應(yīng)的鎖存器。例如,可以設(shè)置低兩位是“11”時(shí),DSP送入PWM電路的是ll位的調(diào)相信號(hào);當(dāng)?shù)蛢晌辉O(shè)置成“01”時(shí),DSP送入PWM電路的是10位調(diào)節(jié)A相占空比的信號(hào);當(dāng)?shù)蛢晌辉O(shè)置成“10”時(shí),DSP送入PWM電路的是10位調(diào)節(jié)B相占空比的信號(hào)。由此可以在電路中設(shè)計(jì)一個(gè)三輸人的與門,當(dāng)16位數(shù)據(jù)傳輸完畢,即在相應(yīng)gate的引腳上輸出高電平時(shí),數(shù)據(jù)存入對(duì)應(yīng)的鎖存器,如圖5所示。

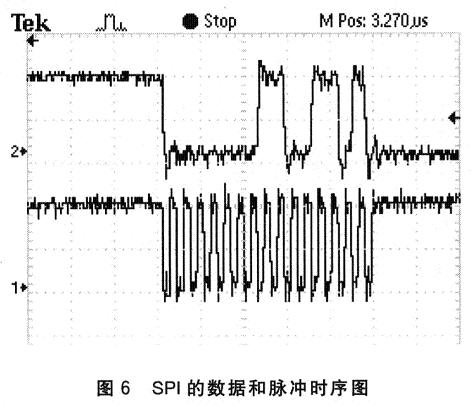

2.3 DSP與LTC6903的接口配置

由于LTC6903芯片本身具有SPI接口,需要在DSP的程序中設(shè)置相應(yīng)的SPI寄存器。LTC6903采用上升沿接收,且接收時(shí)高位在前,所以需要DSP設(shè)置為下降沿傳輸,傳輸時(shí)高位在前。在傳輸?shù)倪^程中,在脈沖信號(hào)的下降沿?cái)?shù)據(jù)發(fā)生變化,傳輸數(shù)據(jù);在脈沖信號(hào)的上升沿?cái)?shù)據(jù)穩(wěn)定,便于LTC6903鎖存數(shù)據(jù),傳輸時(shí)序如圖6所示。從圖中可以看出,所要傳輸?shù)臄?shù)據(jù)是十六進(jìn)制數(shù)019A,下降沿?cái)?shù)據(jù)發(fā)生變化,上升沿?cái)?shù)據(jù)穩(wěn)定,傳輸16位數(shù)據(jù),有16個(gè)脈沖。實(shí)驗(yàn)結(jié)果表明,DSP配置是與LTC6903的SPI接口工作時(shí)序相匹配的。

3 DSP中SPI的開發(fā)過程

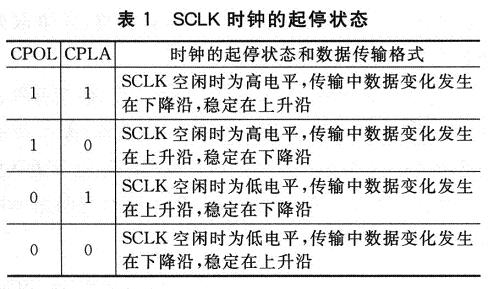

SPI端口數(shù)據(jù)傳輸?shù)奶攸c(diǎn)是:主設(shè)備的時(shí)鐘信號(hào)出現(xiàn)與否決定數(shù)據(jù)傳輸?shù)拈_始,一旦檢測(cè)到時(shí)鐘信號(hào)即開始傳輸,時(shí)鐘信號(hào)無效后傳輸結(jié)束。這期間,從設(shè)備使能時(shí)鐘信號(hào)的起停狀態(tài)很重要。DSP56F801的SPI端口的時(shí)鐘信號(hào)起停狀態(tài)如表1所列。在設(shè)計(jì)中設(shè)置的SPI控制寄存器的CPOL和CPLA位是“11”。SCLK空閑時(shí)為高電平,傳輸中數(shù)據(jù)變化發(fā)生在下降沿,穩(wěn)定在上升沿。從圖2可看出實(shí)現(xiàn)了與CPLD中的移位鎖存電路的匹配,傳輸正確。

SPI端口協(xié)議要求系統(tǒng)上電復(fù)位后,從機(jī)先于主機(jī)開始工作。如果從機(jī)在主機(jī)之后開始工作,就有可能丟掉部分時(shí)鐘信號(hào),使得從機(jī)并不是從數(shù)據(jù)的第一位開始接收,造成數(shù)據(jù)流的不同步。可通過硬件延時(shí)或軟件延時(shí)的方法,來確保從機(jī)先于主機(jī)工作。本設(shè)計(jì)采用軟件延時(shí)的辦法來實(shí)現(xiàn)數(shù)據(jù)流的同步。這個(gè)延時(shí)由兩部分組成,一部分是DSP串行輸出數(shù)據(jù)的時(shí)間延時(shí),另外一部分就是后續(xù)數(shù)字電路中的延時(shí)。延時(shí)的具體計(jì)算過程如下:數(shù)據(jù)傳輸時(shí)使用的時(shí)鐘信號(hào)是對(duì)總線時(shí)鐘的2分頻,當(dāng)DSP的主頻是60 MHz時(shí),總線時(shí)鐘頻率是30MHz,對(duì)它進(jìn)行2分頻,可以計(jì)算出SCLK的周期是66.6ns(實(shí)際所測(cè)出的周期是78.2 ns)。另外通過測(cè)試得到PWM電路的延時(shí)最長時(shí)間是23.6 ns,鎖存器的最大延時(shí)是7.6 ns,移位寄存器的最大延時(shí)是3.O ns。由上述對(duì)CPLD數(shù)字電路的延時(shí)和對(duì)SCLK周期的測(cè)試,就可以得到這樣一個(gè)結(jié)論:設(shè)PWM電路的延時(shí)時(shí)間為t1、鎖存器的延時(shí)時(shí)間為t2、移位寄存器的延時(shí)時(shí)間為t3、SCLK的時(shí)鐘周期是Tc,在SPI傳輸?shù)倪^程中,整個(gè)電路的延時(shí)t可以這樣計(jì)算:

由于數(shù)字電路傳輸中存在這樣的延時(shí),所以在寫DSP程序時(shí),需要加入一定的延時(shí)。此實(shí)驗(yàn)中加入的延時(shí)是2μs,可以實(shí)現(xiàn)可靠傳輸。

4 實(shí)驗(yàn)結(jié)果

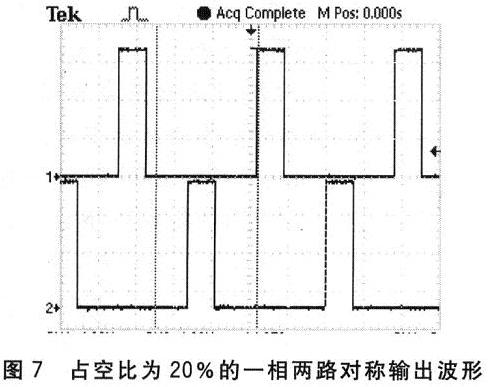

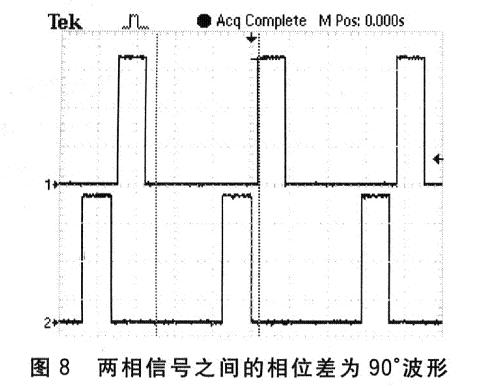

本設(shè)計(jì)采用全數(shù)字結(jié)構(gòu),易于用CPLD實(shí)現(xiàn)。以EPM7256為目標(biāo)芯片,設(shè)計(jì)并實(shí)現(xiàn)了正確的數(shù)據(jù)傳輸。當(dāng)DSP56F801輸出的十六進(jìn)制參數(shù)分別為頻率字DBOE,相位字0403,A相的占空比字04CE,B相的占空比字04CD時(shí),波形輸出如圖7、圖8所示。圖7給出了信號(hào)發(fā)生器A相輸出信號(hào)的實(shí)測(cè)波形,信號(hào)占空比調(diào)節(jié)為20%;圖8給出了A相輸出信號(hào)1和B相輸出信號(hào)l的實(shí)測(cè)波形,兩相信號(hào)相位差調(diào)節(jié)為常用的90°。該實(shí)驗(yàn)結(jié)果表明,參數(shù)傳輸正確,波形輸出良好。

結(jié) 語

SPI通信方式具有硬件連接簡(jiǎn)單、使用方便等優(yōu)點(diǎn),應(yīng)用廣泛。采取硬件和軟件相結(jié)合的措施,可以確保SPI通信中數(shù)據(jù)流的同步,實(shí)現(xiàn)可靠通信。本文給出了DSP多SPI端口通信的設(shè)計(jì)與實(shí)現(xiàn)過程,討論了其中的關(guān)鍵技術(shù)問題。SPI多端口通信方法基于CPLD實(shí)現(xiàn),易移植,易于實(shí)現(xiàn)功能擴(kuò)展,可廣泛應(yīng)用于各種采用SPI通信方式的自動(dòng)化裝置。