1、引言

六自由度電磁敏感定位系統(tǒng)作為一種新型的跟蹤定位裝置,可實時地確定目標的六個參數(shù),已在機載火控系統(tǒng)(頭盔瞄準具)、精密醫(yī)療器械、單兵作戰(zhàn)模擬訓練中獲得廣泛應用[1、2]。該跟蹤系統(tǒng)由正弦信號發(fā)射電路、敏感信號接收電路組成的硬件和從敏感接收數(shù)據(jù)中求解目標參數(shù)的算法程序兩部分組成,定位計算精度受制于上述兩部分的誤差。目前,在不考慮環(huán)境因素影響的情況下,算法誤差已達到小于1毫弧的水平,因此,硬件電路的誤差成為制約系統(tǒng)定位精度的主要因素。根據(jù)工作原理,該系統(tǒng)采取按時序依次激勵發(fā)射天線,從而根據(jù)敏感天線接收信號組成接收矩陣計算目標參數(shù)。然而,作為時序控制電路的模擬器件,存在無法避免的溫度漂移和時間漂移問題,從而大大影響了時序發(fā)射的精度,使系統(tǒng)定位計算的精度降低。為了解決該問題,本文利用CPLD數(shù)字控制技術對時序電路進行改進。CPLD(Complex Programmable Logic Device)是新一代的數(shù)字邏輯器件,具有速度快、集成度高、可靠性強、用戶可重復編程或動態(tài)重構其邏輯功能等特點。利用CPLD芯片和數(shù)字控制技術設計的時序電路,可將時序控制的精度提高到納秒級,并且工作穩(wěn)定,不受溫度的影響,有利于系統(tǒng)定位精度的提高。

2、系統(tǒng)原理[2、3]

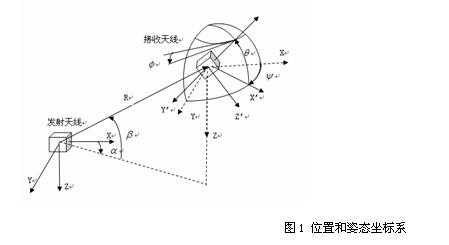

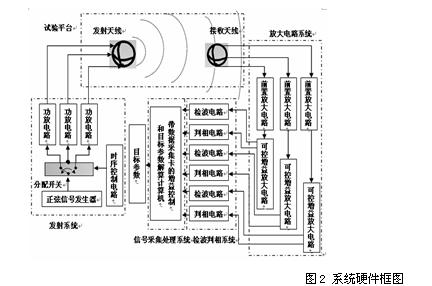

六自由度電磁敏感系統(tǒng)的工作原理[2]如下:以發(fā)射天線的三個軸(x、y、z)為參考坐標系,接收天線相對于發(fā)射天線的位置參數(shù)由距離 、方位角和仰角表示,姿態(tài)參數(shù)由偏航角 、俯仰角 和橫滾角 表示,此六個參數(shù)即為需要計算的目標參數(shù),即六自由度,參看圖1。系統(tǒng)由正弦信號發(fā)生器、時序控制電路、功率放大電路、三軸環(huán)天線、接收信號放大電路、檢波判相電路和數(shù)據(jù)采集與參數(shù)計算電路組成,參看圖2。

系統(tǒng)工作時,發(fā)射電路以時分制激勵方式依次激勵發(fā)射天線的三路環(huán)形天線,每激勵一次,接收天線(共三路)均收到三個信號,在一個激勵周期內接收天線共收到九個信號,由此九個信號組成的接收矩陣可計算出所有的目標參數(shù)。

3、時序控制電路設計[4]

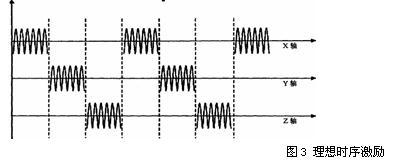

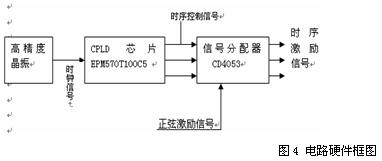

由系統(tǒng)工作原理可知,發(fā)射信號需以時分制方式依次激勵三路發(fā)射天線,因此,時序控制的精確在提高系統(tǒng)跟蹤定位計算精度方面顯得十分重要。圖3是時序控制理想工作狀態(tài)下,發(fā)射信號時分制激勵發(fā)射的狀態(tài)圖。但由于原時序電路采用的電容等模擬元器件的有限精度以及模擬器件受溫度影響的結果,時序控制信號會發(fā)生漂移,精度較低,從而使接收矩陣元素的實際值與理論值發(fā)生較大大偏差,影響了系統(tǒng)的計算精度。要想提高系統(tǒng)定位計算的精度,必須提高系統(tǒng)時序控制的精度,基于此,本文根據(jù)CPLD數(shù)字控制技術,在MAX II系列芯片EPM570T100C5上設計了一種新型的數(shù)字時序控制電路,大大提高了系統(tǒng)時序控制的精度,從而提高了系統(tǒng)計算精度。電路組成如圖4所示。

由32MHz高精度晶體振蕩器提供精確的時鐘信號。MAX II芯片EPM570T100C5產生精確的時序控制信號。EPM570是世界一流的低成本器件,適用于實現(xiàn)任何數(shù)字控制功能。該芯片采用非易失單芯片解決方案,可解決處理器I/O引腳不夠用等板級問題,管理上電排序,配置其它更復雜的器件,或者低成本實現(xiàn)不兼容接口(“膠合邏輯”)的轉換。具有低成本、零功耗、小封裝、瞬間啟動以及非易失性、系統(tǒng)內可編程能力(ISP)等優(yōu)點。CD4053根據(jù)CPLD芯片提供的精確時序數(shù)字控制信號完成正弦信號的時分制激勵。