??? 摘 要: DS92LV18是集串行編碼器和解碼器于一體的高性能串行解串器,是光纖數(shù)據(jù)傳輸設(shè)計中的理想器件,筆者以自身的設(shè)計體驗,對該芯片在光纖數(shù)據(jù)傳輸設(shè)計中應(yīng)該注意的問題進(jìn)行了深入的研究,并給出了相應(yīng)的解決方案。

??? 關(guān)鍵詞: DS92LV18? 編碼器? 解碼器? 串行解串器? 光纖數(shù)據(jù)傳輸

?

??? DS92LV18是National公司推出的一款高性能串行解串器,該芯片集串行編碼器和解碼器于一體,是光纖數(shù)據(jù)傳輸設(shè)計中的理想器件[4][5]。筆者多次在高速視頻數(shù)據(jù)傳輸設(shè)計中選用了該芯片。使用過程中發(fā)現(xiàn),在電氣接口匹配、時鐘、PCB布線、電源和接地設(shè)計等幾個問題上必須引起高度重視。否則,設(shè)計出的光傳輸模塊" title="光傳輸模塊">光傳輸模塊只能在實驗室測試條件下滿足應(yīng)用要求,而當(dāng)實際應(yīng)用于系統(tǒng)后,由于數(shù)據(jù)傳輸不穩(wěn)定,誤碼率極高,根本不能滿足應(yīng)用要求。更極端的情況是,設(shè)計的模塊根本不能傳輸數(shù)據(jù)。針對上述問題,筆者提出了相應(yīng)的解決方案。

1 光傳輸模塊的硬件組成

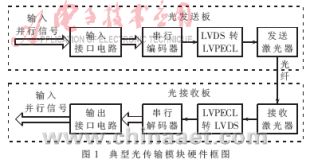

??? 光傳輸模塊的硬件由光發(fā)送板和光接收板組成,其典型硬件構(gòu)成如圖1所示。

???????????????????

??? 在實際應(yīng)用中,輸入光發(fā)送板的數(shù)字信號一般為并行RS422信號、并行LVDS信號、并行TTL/LVTTL和并行CMOS/LVCMOS信號等。經(jīng)過輸入接口電路" title="接口電路">接口電路處理,將這些信號變換成串行編碼器能接收的LVTTL/LVCMOS并行信號。圖1中,串行編碼器的作用是將并行LVTTL/LVCMOS信號編碼成高速的串行LVDS信號,而發(fā)送激光器一般只能接收LVPECL信號,因此在串行編碼器和發(fā)送激光器之間要增加LVDS轉(zhuǎn)LVPECL電氣接口匹配電路。

??? 從發(fā)送板激光器發(fā)出的光信號經(jīng)過光纖進(jìn)入光接收板的接收激光器,接收激光器經(jīng)過光電轉(zhuǎn)換后,輸出LVPECL電信號,然后經(jīng)LVPECL轉(zhuǎn)LVDS電氣接口匹配電路將LVPECL信號轉(zhuǎn)換成LVDS信號給串行解碼器;串行解碼器將串行LVDS信號恢復(fù)成并行的LVTTL/LVCMOS信號,然后經(jīng)過輸出接口電路將并行LVTTL/LVCMOS信號變換成下級電路需要的并行信號。

2 DS92LV18簡介

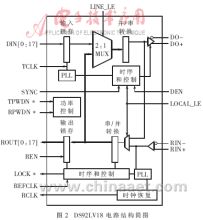

??? 圖2是DS92LV18的電路結(jié)構(gòu)簡圖[5],其芯片的引腳功能如下:

???????????????????

??? DIN[0:17]:18位并行LVTTL/LVCOMS輸入數(shù)據(jù)信號;

??? TCLK:編碼時鐘,該時鐘的輸入范圍為15MHz~66MHz,當(dāng)編碼器工作時,該時鐘信號" title="時鐘信號">時鐘信號經(jīng)編碼鎖相環(huán)" title="鎖相環(huán)">鎖相環(huán)20倍頻后將DIN[0:17]和TCLK編碼成20位串行數(shù)據(jù)信號,以LVDS信號從DO+和DO-輸出,應(yīng)用中要求與解碼時鐘REFCLK同頻率,兩個時鐘頻率偏差不能超過5%;

?? ?SYNC:編碼器工作控制信號,當(dāng)編碼器工作時,該信號置低電平;

?? ?TPWDN:編碼器工作控制信號,當(dāng)編碼器工作時,該信號置高電平;

?? ?DEN:編碼器工作控制信號,當(dāng)編碼器工作時,該信號置高電平;

??? RPWDN:解碼器工作控制信號,當(dāng)解碼器工作時,該信號置高電平;

?? ?REN:解碼器工作控制信號,當(dāng)解碼器工作時,該信號置高電平;

??? RIN+、RIN-:解碼器輸入串行LVDS信號;

??? ROUT[0:17]:解碼器輸出的18位并行LVTTL信號;

??? RCLK:解碼器輸出時鐘,當(dāng)解碼器正常工作時,該時鐘與輸入的解碼時鐘REFCLK同頻率;

??? LOCK:解碼器工作狀態(tài)指示信號,當(dāng)解碼器工作不正常時,該信號為高電平,通過檢測該號可以測出系統(tǒng)傳輸?shù)恼`碼率;

??? LINE_LE:回饋信號,當(dāng)該信號置高電平時,輸入信號RIN+和RIN-直接輸出給DO+和DO-,該信號可以用于芯片工作狀態(tài)檢測,實際應(yīng)用中,該信號置低電平;

??? LOCAL_LE:回饋信號,當(dāng)該信號置高電平時,輸入信號DIN[0:17]直接輸出給ROUT[0:17],該信號可以用于芯片工作狀態(tài)檢測,在實際應(yīng)用中置低電平;

??? AVDD:模擬供電電源,3.3V供電;

??? AGND:模擬地;

?? ?DVDD:數(shù)字供電電源,3.3V供電;

??? DGND:數(shù)字地;

??? PVDD:鎖相環(huán)供電電源,3.3V供電;

??? PGND:鎖相環(huán)地。

3 設(shè)計中應(yīng)注意的問題

3.1 電氣接口匹配

??? LVDS和LVPECL是高速數(shù)據(jù)傳輸設(shè)計中常用的兩種電氣接口標(biāo)準(zhǔn)。兩種電氣接口標(biāo)準(zhǔn)的詳細(xì)情況可見參考文獻(xiàn)[2]~[4]。兩種電氣接口之間的接口匹配轉(zhuǎn)換電路有兩種實現(xiàn)方式:(1)使用電阻、電容分立元件進(jìn)行匹配轉(zhuǎn)換;(2)使用TI、MAXIM、NATIONAL等公司提供的專用芯片進(jìn)行匹配轉(zhuǎn)換。具體的轉(zhuǎn)換匹配電路見參考文獻(xiàn)[3]。

??? 圖3是高頻狀態(tài)下電阻、電容的等效電路圖。實驗中發(fā)現(xiàn),無論采用那種匹配方式,相關(guān)外接電阻、電容的封裝都是越小越好,尤其是傳輸速率達(dá)吉赫茲以上時,外接電阻、電容最好選用0402這樣的小封裝,否則,電阻、電容的分布電感電容可能會嚴(yán)重影響電路的性能,有時甚至?xí)乖O(shè)計失敗。

??????????????????????????

3.2 時鐘設(shè)計

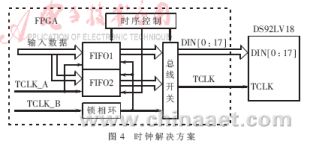

??? 筆者在調(diào)研過程中發(fā)現(xiàn),類似DS92LV18的芯片下限工作頻率都比較高,DS92LV18是下限工作頻率稍低的芯片。如果數(shù)據(jù)傳輸速率低于15MHz,圖1光發(fā)送板中,不能將經(jīng)輸入接口電路轉(zhuǎn)換的數(shù)據(jù)信號和時鐘信號直接連到DS92LV18相關(guān)的引腳上。實驗過程中發(fā)現(xiàn),光接收板中,串行解碼器一般由外部晶體直接提供時鐘信號,該時鐘信號經(jīng)過阻抗匹配后一般都比較穩(wěn)定,可是,光發(fā)送板中,編碼時鐘信號是經(jīng)過輸入接口電路轉(zhuǎn)換得到的,由于轉(zhuǎn)換電路產(chǎn)生的誤差,兩個時鐘信號有時很難滿足偏差小于5%的應(yīng)用要求。更糟糕的情況是,在某系統(tǒng)中,由于地線干擾等原因,進(jìn)入光發(fā)送板的時鐘信號上偶爾會出現(xiàn)毛刺,以上兩種情況都會導(dǎo)致光傳輸模塊不能正常工作。針對以上問題,筆者對光發(fā)送板硬件進(jìn)行了改進(jìn),提出了圖4所示的解決方案。

??? 圖4中,虛線中的部分由FPGA實現(xiàn)。目前,F(xiàn)PGA技術(shù)比較成熟,一般低價位FPGA中都集成了多個鎖相環(huán)和少量可編程的存儲器資源,該可編程存儲器資源可以被配置為雙口RAM、SRAM、FIFO等。圖4中,TCLK_A為光發(fā)送板中經(jīng)輸入接口電路轉(zhuǎn)換后得到的數(shù)據(jù)同步時鐘信號,TCLK_B為由時鐘晶體產(chǎn)生的穩(wěn)定時鐘信號(該時鐘信號大于等于15MHz),F(xiàn)IFO1和FIFO2為工作在乒乓方式下的兩個FIFO。當(dāng)一個FIFO存儲輸入數(shù)據(jù)時,另一個FIFO讀出存儲的數(shù)據(jù),讀出時鐘由TCLK_B提供,讀出的數(shù)據(jù)通過總線開關(guān)輸出給DS92LV18,相應(yīng)的控制邏輯由時序控制器產(chǎn)生。通常,TCLK_A不會有毛刺,可以作為FIFO的存儲時鐘。為了提高數(shù)據(jù)傳輸?shù)姆€(wěn)定性,建議對TCLK_A作如下處理:當(dāng)TCLK_A大于15MHz時,使TCLK_B與TCLK_A同頻,然后將TCLK_B四倍頻,利用倍頻時鐘對TCLK_A過采樣,將TCLK_A恢復(fù)成穩(wěn)定的同頻時鐘,然后利用該恢復(fù)時鐘作為FIFO的存儲時鐘;當(dāng)TCLK_A小于15MHz時,使TCLK_B為TCLK_A的整數(shù)倍,同樣使用過采樣技術(shù)對TCLK_A進(jìn)行處理,然后供FIFO作為存儲時鐘使用。編碼時鐘由FPGA將TCLK_B經(jīng)過內(nèi)部鎖相環(huán)鎖相后提供給DS92LV18使用。實驗發(fā)現(xiàn),編碼時鐘信號經(jīng)過以上處理后,非常穩(wěn)定,完全可以滿足應(yīng)用要求。

???????????????????????????

3.3 PCB布線設(shè)計

??? 光發(fā)送板和接收板中有LVTTL/LVCMOS、LVDS和LVPECL等幾種信號。LVDS/LVPECL信號很容易被LVTTL/LVCMOS信號干擾,在PCB布線設(shè)計時,必須注意以下問題:

??? (1)至少使用4層PCB板(從頂層到底層):LVDS/LVPECL信號層、地層、電源層、LVTTL/LVCMOS信號層[1];

??? (2)使單端信號和LVDS/LVPECL信號相互隔離,否則單端信號可能會耦合到LVDS信號上,最好將單端信號和LVDS/LVPECL信號放在由電源/地層隔離的不同層上。如果在同一層上,單端信號和LVDS/LVPECL信號的距離至少應(yīng)該在12mm以上[3];

??? (3)使用分布式的多個電容來旁路LVDS/LVPECL設(shè)備,表面貼電容靠近電源/地層管腳放置[3][4];

??? (4)電源層和地層應(yīng)使用粗線,不要使用50Ω布線規(guī)則[3];

??? (5)保持PCB地線層返回路徑寬而短[3][4];

??? (6)盡量減少過孔和其他引起線路不連續(xù)性的因素[3][4];

??? (7)避免導(dǎo)致阻值不連續(xù)性的90°走線,使用圓弧或45°折線來替代[1];

??? (8)在差分" title="差分">差分線對內(nèi),兩條線之間的距離應(yīng)盡可能短,以保持接收器的共模抑制能力,在印制板上,兩條差分線之間的距離應(yīng)盡可能保持一致,以避免差分阻抗的不連續(xù)性[1];

??? (9)使用端接電阻實現(xiàn)對差分傳輸線的最大匹配,阻值一般在90Ω~130Ω之間,系統(tǒng)也需要此終端電阻來產(chǎn)生正常工作的差分電壓[3];

??? (10)最好使用精度1%~2%的表面貼電阻(0402封裝)跨接在差分線上,必要時也可使用兩個各為50Ω的電阻,并在中間通過一個電容接地,以濾去共模噪聲[4];

??? (11)端接電阻應(yīng)遠(yuǎn)離驅(qū)動端,盡量靠近接收輸入端[3][4]。

3.4 電源和接地設(shè)計

??? 光發(fā)送板中有輸入接口電路供電,DS92LV18有數(shù)字電源、模擬電源和鎖相環(huán)電源,F(xiàn)PGA有內(nèi)核電源、I/O電源和鎖相環(huán)電源。實驗中發(fā)現(xiàn),DS92LV18模擬電源和鎖相環(huán)電源共用電源,DS92LV18數(shù)字電源和FPGA的I/O電源共用電源。其他電源分別供電,這是比較好的電源供電方案。電源模塊最好使用線性穩(wěn)壓芯片,不要使用開關(guān)電源模塊。而且,穩(wěn)壓電源芯片最好都加三級以上的LC濾波電路,然后再供相應(yīng)的芯片使用。實驗中還發(fā)現(xiàn),激光器和DS92LV18的功耗非常大,需要很大的供電電流,給激光器和DS92LV18供電的線性穩(wěn)壓電源芯片最好能提供2A以上的輸出電流,相應(yīng)濾波電路一定要注意電感的過電流能力和電感上的壓降,盡量選用電阻小、過電流大的電感,同時要做好電源穩(wěn)壓芯片的散熱設(shè)計。實驗中還發(fā)現(xiàn),系統(tǒng)中如果只有使用開關(guān)電源供電的應(yīng)用場合,相應(yīng)的供電開關(guān)電源模塊一定要預(yù)留30%以上的輸出功率,否則,開關(guān)電源的開關(guān)特性可能會變得很差,即使加多級濾波電路也無法消除比較大的開關(guān)噪聲。

??? 為了排除前級電路對光發(fā)送板的干擾,圖1所示的輸入接口電路最好使用數(shù)字隔離器將前級電路地和后級電路地實現(xiàn)物理隔離。DS92LV18有鎖相環(huán)地PGND、模擬地AGND和數(shù)字地DGND,F(xiàn)PGA有數(shù)字地FDGND和鎖相環(huán)地FPGND,設(shè)計中PGND、FPGND和AGND共地,DGND和FDGND共地,將這兩個地分割,在板上設(shè)置一個公共地COM_GND,最后AGND、DGND和COM_GND以圖5的方式共地。

??????????????????????????????? ?????

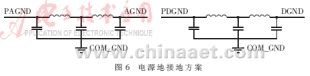

????在實際應(yīng)用中,給光傳輸模塊供電的電源線和地線可能會加長。為了減小地線干擾,為模擬電源供電的電源地PAGND和為數(shù)字電源供電的電源地PDGND與模擬地AGND和數(shù)字地DGND的接地方案如圖6所示。

??????????????????????????????

????圖5和圖6的公共地COM_GND在系統(tǒng)應(yīng)用中為機(jī)殼地,在實際應(yīng)用中,上面的接地方案對系統(tǒng)地線干擾有明顯的抑制作用。光接收板的電源和地設(shè)計與光發(fā)送板相同。

4 實驗結(jié)果

??? 圖7是沒有注意上述設(shè)計問題的實驗結(jié)果,從圖像顯示的結(jié)果可以看出,光傳輸模塊根本不能正常工作,設(shè)計是失敗的。圖8是注意了上述設(shè)計問題的實驗結(jié)果,從圖像顯示的結(jié)果可以看出,該設(shè)計非常成功,完全可以滿足應(yīng)用要求。

??????????????????????????????

?? 92LV18是光纖數(shù)據(jù)傳輸設(shè)計中很有代表性的一款芯片,筆者采用工程應(yīng)用中發(fā)現(xiàn)問題、解決問題的方法對該芯片的應(yīng)用進(jìn)行了深入探討,文中設(shè)計思路具有通用性,對解決類似工程問題具有很大的借鑒價值。

參考文獻(xiàn)

[1] 武斌,夏宇聞.數(shù)字視頻信號的長線傳輸[J].電子技術(shù)應(yīng)用,2003,(10):62-65.

[2] 代芬,漆海霞,俞龍.幾種常用邏輯電平電路的特點及應(yīng)用[J].單片機(jī)與嵌入式系統(tǒng)應(yīng)用,2005,(5):5-7.

[3] Differential PECL/ECL/LVPECL/LVECL?clock and data driver.Maxim integrated?products,2004.

[4] LVDS Ownerps Manual.National Semicon-ductor,2004.

[5] DS92LV18 datasheet.National Semicon ductor,2003.