隨著今天模數(shù)轉(zhuǎn)換器的數(shù)據(jù)轉(zhuǎn)換采樣速度進入到每秒千兆次采樣(GSPS),系統(tǒng)需要能夠支持這樣高的轉(zhuǎn)換速度,模擬器件必須產(chǎn)生和放大高頻信號。除了模擬信號路徑外,設(shè)計師需要完全了解采樣時鐘和高比特率數(shù)據(jù)獲取電路方面。信號路徑設(shè)計師將為這兩個關(guān)鍵的方面提供建議方案。下面的信息與需要高性能ADC的系統(tǒng)緊密相關(guān)。

時鐘源

在高速數(shù)據(jù)轉(zhuǎn)換系統(tǒng)中一個最重要的子系統(tǒng)是時鐘源,這是因為時鐘信號的時序準(zhǔn)確性可以直接影響ADC的動態(tài)特性。為減少這種影響,ADC時鐘源必須表現(xiàn)出非常低的時序抖動或相位噪聲。如果在選擇時鐘電路時沒有考慮到這種因素,無論前端模擬電路或者ADC的質(zhì)量有多高,系統(tǒng)可能表現(xiàn)出很差的動態(tài)性能。優(yōu)良的時鐘將總能在精確的時鐘間隔內(nèi)出現(xiàn)時鐘沿的轉(zhuǎn)換。實際上,時鐘邊沿到達的時間間隙總是在不斷變化的,這種時序的不確定性帶來的結(jié)果是采樣波形的信噪比會受到數(shù)據(jù)轉(zhuǎn)換過程的影響。

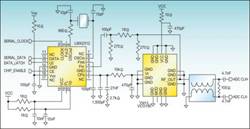

圖1:PLL與VCO時鐘系統(tǒng)。

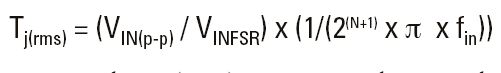

可以容忍的最大時鐘抖動為抖動噪聲超過量化噪聲(1/2LSB)前的時鐘抖動。這可以用下面的公式定義:

如果優(yōu)化輸入電壓(VIN)使之等于ADC的輸入電壓范圍(VINFSR),那么抖動要求成為ADC分辨率(N位)和被采樣的輸入頻率(fin)的一個因子。

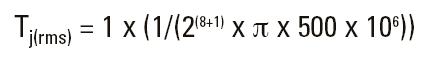

對于達到奈奎斯特速率(對于1GSPS轉(zhuǎn)換速率為500MHz)的輸入頻率,總的抖動要求是:

這個值代表了來自所有抖動源的總抖動。ADC器件本身導(dǎo)致的一個抖動源稱為窗口抖動(aperture jitter),這是輸入采樣和器件的保持電路相關(guān)的一種時序不確定性,在確定時鐘源允許的最大時鐘抖動時,需要考慮這種不確定性。

時鐘電路抖動=(Tj(rms)2-(ADC(窗口抖動)2))1/2

以ADC08D1000為例,窗口抖動在數(shù)據(jù)手冊中給定的值為0.4ps,這個值將ADC時鐘的抖動標(biāo)準(zhǔn)限制到-1.1ps。

然而,當(dāng)用在數(shù)據(jù)轉(zhuǎn)換系統(tǒng)中時,將振蕩器的性能數(shù)據(jù)與規(guī)范要求簡單地匹配或許并不足以獲得期望的結(jié)果。這是因為頻率分量也扮演著重要的作用。因此,用頻譜分析儀來對時鐘信號進行檢查很重要,并確保與基本頻率相關(guān)的能量沒有在很大的范圍內(nèi)擴展。延伸到更高頻率的毛刺可能很明顯,也將會對性能產(chǎn)生直接的影響。

圖1顯示了針對ADC08D1000的推薦時鐘電路,由一個鎖相環(huán)器件(LMX2312)連接到可變電感壓控振蕩器(VCO)組成。PLL和VCO維持達到奈奎斯特輸入頻率ADC08D1000要求的信噪比(46dB)。

數(shù)據(jù)獲取

對信號進行高頻(1GSPS及以上)采樣意味著轉(zhuǎn)換所產(chǎn)生的數(shù)字輸出數(shù)據(jù)必須儲存起來,或者至少快速地轉(zhuǎn)移。處理每秒超過一億次轉(zhuǎn)換的兩個關(guān)鍵問題是系統(tǒng)中數(shù)字器件之間的信號完整性,以及每個時鐘周期數(shù)據(jù)轉(zhuǎn)移的速度。

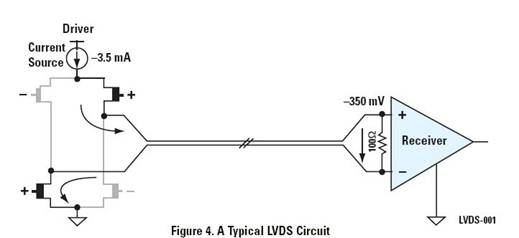

為使數(shù)字輸出信號完整性最大化,高速ADC使用低電壓差分信號(或者LVDS)傳輸(見圖2)。

圖2:典型的LVDS電路。

LVDS信號傳輸方法的主要優(yōu)點是以非常低的功率預(yù)算實現(xiàn)高數(shù)據(jù)速率,對每個將通過一個電路板或者電纜傳輸?shù)姆蛛x信號采用兩條連線來實現(xiàn)這種低功耗。每條線上的電壓變化的方向互相相反,且與像CMOS或者TTL這樣的單端信號相比信號的強度比較小(一般為350mV)。這是因為差分電路固有的抗噪聲能力,因此可以使用低電壓擺幅信號。這反過來意味著信號頻率可以更快,因為信號的上升時間更短了。

電路板上傳輸差分波形的信號線應(yīng)該設(shè)計成具有100Ω的特征阻抗(LVDS標(biāo)準(zhǔn)所定義的值),這些線在接收器端用100Ω的電阻來進行端接以與線路匹配。通過發(fā)射器電路上的電流源在100Ω的電阻上流過3.5mA的電流,產(chǎn)生一個信號電壓,提供350mV的信號擺幅,供接收電路檢測。

高速發(fā)送數(shù)據(jù)只是問題的一半,還需要考慮將數(shù)據(jù)存儲在存儲器陣列中以作后

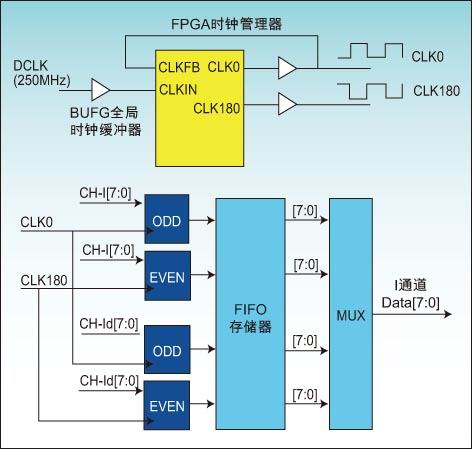

續(xù)處理。ADC對其每個通道提供一個解復(fù)用的數(shù)據(jù)輸出。器件不是提供一個運行在等于采樣速度的單一8位總線,而是同時在兩個8位數(shù)據(jù)總線上輸出兩個連續(xù)采樣。這種方法將數(shù)據(jù)速率減半,但是增加了數(shù)據(jù)位數(shù),對于一個1GSPS的采樣速率,來自ADC的轉(zhuǎn)換數(shù)據(jù)輸出速度為500MHz。即使在這種降低的速度下,大多數(shù)分立存儲器或者FPGA內(nèi)部存儲器在可靠獲取這個數(shù)據(jù)上也存在問題。因此使用DDR非常有利,因為DDR在時鐘的上升和下降沿都輸出數(shù)據(jù)。盡管數(shù)據(jù)速率對于DDR信號傳輸來說不變,時鐘頻率減半,達到更便于管理的250MHz,這個頻率在CMOS存儲電路的范圍內(nèi)。在數(shù)據(jù)能保存在存儲器之前,需要在輸入到FPGA器件中間采用一個數(shù)據(jù)鎖存器對。第一個鎖存器使用同步數(shù)據(jù)時鐘,而第二個鎖存器使用180度異相的時鐘,或者反向數(shù)據(jù)時鐘(見圖3)。

圖3:FPGA數(shù)據(jù)獲取架構(gòu)框圖。

為簡化這種時鐘要求,F(xiàn)PGA帶有一種以PLL(鎖相環(huán))或者DLL(延時鎖定環(huán))形式實現(xiàn)的數(shù)字時鐘管理器。這些器件允許在內(nèi)部產(chǎn)生時鐘信號,這些時鐘信號能與輸入時鐘信號鎖定,提供相位延時間隔為0、90、180和270度。這種時鐘管理功能允許DDR時鐘方案通過提供一種精確的180度移相時鐘來有效工作。這反過來允許輸入數(shù)據(jù)與下降沿同步,以能可靠地獲取到數(shù)據(jù)鎖存器中。

在鎖存之后,輸入數(shù)據(jù)可以被傳輸?shù)紽IFO存儲器或者Block RAM。在這里,數(shù)據(jù)可以以很低的速度輕易地被系統(tǒng)微控制器獲得,以進行獲取后的處理。