??? 摘 要: 介紹了傳統(tǒng)模擬Costas環(huán)路存在的問題,通過對(duì)Costas環(huán)路原理的分析,利用連續(xù)時(shí)間域與離散時(shí)間域之間的變換關(guān)系,推導(dǎo)出Costas環(huán)路的離散模型,據(jù)此闡述了環(huán)路各模塊參數(shù)的計(jì)算及電路設(shè)計(jì)。最后利用FPGA對(duì)Costas環(huán)載波恢復(fù)電路進(jìn)行了實(shí)現(xiàn),并給出了所實(shí)現(xiàn)的RTL原理圖。

??? 關(guān)鍵詞: Costas環(huán)? 載波恢復(fù)? FPGA

?

??? Costas環(huán)路作為一種通用的BPSK載波恢復(fù)方法,其實(shí)質(zhì)是一個(gè)負(fù)反饋電路,從而決定了它具有使本地載波的相位或頻率與信號(hào)載波保持一致的能力。Costas環(huán)有許多優(yōu)良的特性,如:載波跟蹤特性、調(diào)制跟蹤特性等[1]。但是傳統(tǒng)模擬Costas環(huán)路因?yàn)榇嬖谕嘀泛驼恢凡黄胶庑约安豢杀苊獾牧泓c(diǎn)漂移,均使環(huán)路的性能受到影響,同時(shí)模擬的Costas環(huán)路調(diào)試?yán)щy,而采用全數(shù)字的實(shí)現(xiàn)方式可以很好地解決以上問題。

1 二階Costas環(huán)的連續(xù)域模型

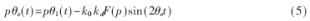

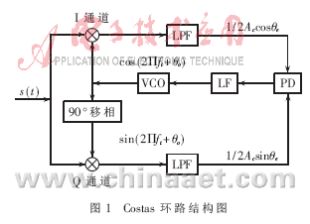

??? 圖1所示為一個(gè)二階Costas環(huán)路。其中輸入信號(hào)為:

???

??????????????????

??? 壓控振蕩器(VCO)的輸出信號(hào)分別為:

???  ????

????

??? 式中kd為鑒相器的靈敏度。

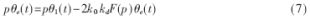

??? 既然是恢復(fù)本地載波,必然要使VCO輸出波形的相位同發(fā)送端波形的相位一致。由此可以建立整個(gè)環(huán)路方程[2]:

?式中:k0是VCO的靈敏度,p是微分算子,F(xiàn)(p)是環(huán)路濾波器" title="環(huán)路濾波器">環(huán)路濾波器(LF)的傳輸算子。

????因?yàn)樵诮?jīng)過幾個(gè)周期之后,θe將會(huì)變得很小,即有:

???  ?

?

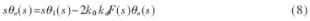

??? 將式(7)進(jìn)行拉氏變換以后可得到:

???  ?

?

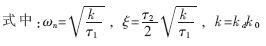

??? 由此可知Costas環(huán)的連續(xù)域模型如圖2所示。

?????????????

??? 為了達(dá)到較好的穩(wěn)態(tài)誤差及動(dòng)態(tài)響應(yīng),環(huán)路濾波器一般采用有源RC積分濾波器,其傳遞函數(shù)" title="傳遞函數(shù)">傳遞函數(shù)為:

???  ?

?

??? 所以二階Costas環(huán)路在連續(xù)域中的開環(huán)傳遞函數(shù)為:

???  ?

?

??? 通過引入環(huán)路固有頻率ωn和阻尼系數(shù)ξ,環(huán)路的開環(huán)傳遞函數(shù)可以表示為:

???  ?

?

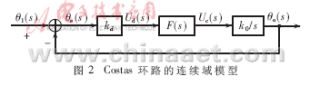

2 二階Costas環(huán)的離散域模型

??? 利用后向差分法可以將連續(xù)時(shí)間域的數(shù)學(xué)模型變換為穩(wěn)定的離散時(shí)間域模型,即用 代替開環(huán)傳遞函數(shù)中的s,可以得到離散的開環(huán)傳遞函數(shù):

代替開環(huán)傳遞函數(shù)中的s,可以得到離散的開環(huán)傳遞函數(shù):

???  ?

?

??? 二階Costas環(huán)路的開環(huán)離散模型如圖3所示。

?????????????????????

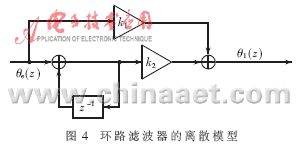

??? 因?yàn)閂CO的離散形式就是數(shù)控振蕩器(NCO),其數(shù)學(xué)模型為 ,所以可以推導(dǎo)出環(huán)路濾波器的離散傳遞函數(shù)為:

,所以可以推導(dǎo)出環(huán)路濾波器的離散傳遞函數(shù)為:

???

??? 環(huán)路濾波器的數(shù)學(xué)模型如圖4所示,據(jù)此可以對(duì)環(huán)路濾波器進(jìn)行設(shè)計(jì)。

?????????????????????????

3 Costas環(huán)路的設(shè)計(jì)與仿真" title="設(shè)計(jì)與仿真">設(shè)計(jì)與仿真

??? 設(shè)計(jì)中系統(tǒng)時(shí)鐘為48MHz,作為NCO、LPF的控制時(shí)鐘。載波頻率為240kHz,在一個(gè)周期內(nèi)采樣20個(gè)點(diǎn),所以采樣時(shí)鐘為4.8MHz,同時(shí)也作為乘法器" title="乘法器">乘法器的時(shí)鐘。本文所有的設(shè)計(jì)都是基于Xilinx ISE7.1i的集成開發(fā)環(huán)境與ModelSim6.1b仿真軟件。

3.1 NCO的設(shè)計(jì)

??? 數(shù)控振蕩器采用直接數(shù)字頻率合成DDFS(簡稱DDS技術(shù))設(shè)計(jì)。DDS是從相位概念出發(fā)直接合成所需波形的一種新的頻率合成技術(shù)[3]。一個(gè)直接數(shù)字頻率合成器一般由一個(gè)相位累加器、ROM波形表組成。其中相位累加器由一個(gè)N位全加器和一個(gè)N位累加寄存器級(jí)聯(lián)而成,對(duì)頻率控制字" title="控制字">控制字的二進(jìn)制碼進(jìn)行累加運(yùn)算。在每個(gè)系統(tǒng)時(shí)鐘沿fclk的控制下,N位加法器將頻率控制字X與累加寄存器輸出的相位數(shù)據(jù)相加,把相加后的結(jié)果再送至累加寄存器,累加寄存器中新的相位數(shù)據(jù)即反饋到加法器的輸入端,以使加法器在下一個(gè)fclk時(shí)鐘周期中繼續(xù)與頻率控制字X相加,同時(shí)累加寄存器的高M(jìn)位數(shù)值將作為查找ROM表中取樣數(shù)據(jù)的地址值。ROM查找表中儲(chǔ)存著一個(gè)完整周期的正弦波幅度信息,通過取得的采樣地址值進(jìn)行查表,從ROM表中輸出相應(yīng)的波形采樣數(shù)據(jù)fout。可以證明:

???? ?

?

??? 用VHDL對(duì)NCO進(jìn)行設(shè)計(jì)時(shí),可以分為三個(gè)子模塊,第一個(gè)是頻率控制字的載入模塊,第二個(gè)是相位累加模塊,第三個(gè)是查表模塊。

3.2 乘法器設(shè)計(jì)與仿真

??? 數(shù)字乘法器有各種實(shí)現(xiàn)方式,如Booth乘法器、Baugh-Wooley乘法器、串行并行乘法器等。各種實(shí)現(xiàn)算法的速度、資源占用情況都不一樣[4]。此處直接調(diào)用了Xilinx公司的IP Core。該乘法器是一個(gè)有符號(hào)數(shù)乘法器,且是一級(jí)流水。對(duì)于本設(shè)計(jì)兩個(gè)輸入都是8位的,輸出結(jié)果是16位。由于兩個(gè)輸入都是介于-1與+1之間的數(shù),而在FPGA設(shè)計(jì)中采用整數(shù)定點(diǎn)運(yùn)算,所以乘法器的最終輸出應(yīng)該除以128。圖5是乘法器的仿真輸出結(jié)果。

??????????????????????

3.3 低通濾波器的設(shè)計(jì)與仿真

??? 通過分析可知:低通濾波器應(yīng)該將乘法器輸出信號(hào)中480kHz的高頻濾去。由于該FIR數(shù)字濾波器的階數(shù)比較高,直接設(shè)計(jì)困難較大,所以利用Matlab中Simulink的FDAtool工具箱來設(shè)計(jì)。設(shè)計(jì)中的參數(shù)選擇如下:fs=4.8MHz,fpass=48kHz,fstop=456kHz,低通段的增益為1db,截止段的增益為-40db。按以上參數(shù)設(shè)計(jì)完成后得到一個(gè)17階的數(shù)字濾波器,其系數(shù)分別為:2、3、4、6、8、9、11、12、12、12、11、9、8、6、4、3、2,然后將這些系數(shù)下載到一個(gè)ROM存儲(chǔ)器中。最終的仿真輸出結(jié)果如圖6所示,由圖可知濾波效果非常好。

??????????????????????

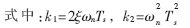

3.4 環(huán)路濾波器的設(shè)計(jì)

??? 根據(jù)圖4所示環(huán)路濾波器的離散模型,可以直接用VHDL進(jìn)行描述。離散域內(nèi)的IIR濾波器由一個(gè)帶反饋的一級(jí)流水線的累加器和一個(gè)一級(jí)流水線的加法器組成。兩個(gè)和系數(shù)相乘的乘法器將簡化為數(shù)據(jù)寄存器的左移和右移,設(shè)計(jì)關(guān)鍵點(diǎn)是對(duì)k1、k2兩個(gè)參數(shù)進(jìn)行計(jì)算。考慮到整個(gè)環(huán)路的增益、量化、擴(kuò)位以及進(jìn)一步的計(jì)算,最終取k1=64,k2=2。具體推導(dǎo)見參考文獻(xiàn)[5]。

??? 圖7是整個(gè)Costas環(huán)在FPGA上實(shí)現(xiàn)以后的頂層RTL原理圖。

??????????????????????

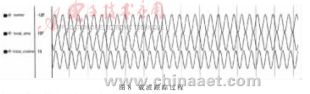

??? 圖8為載波跟蹤的仿真輸出。由圖可見在經(jīng)過有限個(gè)載波周期之后,本地恢復(fù)波形就與載波的相位對(duì)準(zhǔn),由于載波頻率為240kHz,可以知道即使在經(jīng)過240周期之后二者相位才對(duì)準(zhǔn),載波恢復(fù)的時(shí)間仍然能夠達(dá)到1ms,所以具有很好的快速跟蹤性能。

????????????????????????

??? 利用現(xiàn)代EDA技術(shù)將原先用分立元件實(shí)現(xiàn)的模擬Costas環(huán)集成在一塊Xilinx Spartan-3 XC3S400 FPGA器件上面,不僅提高了系統(tǒng)的可靠性,而且由于FPGA自身的可重配置性,使得采用FPGA進(jìn)行設(shè)計(jì)具有設(shè)計(jì)靈活性,用戶可以在不改變外部設(shè)計(jì)的情況下,根據(jù)需要非常方便地改變Costas環(huán)路的跟蹤頻率帶寬,隨時(shí)優(yōu)化、擴(kuò)展電路的功能,系統(tǒng)整體柔性得到提高。

參考文獻(xiàn)

[1] Roland E Best.Phase-Locked Loops?Design,Simulation and Applications.北京:清華大學(xué)出版社,2003.

[2] 王福昌,魯昆生.鎖相技術(shù).武漢:華中科技大學(xué)出版社,1997.

[3] MORELLI D.Modulating Direct Digital Synthesizer in a?Quciklogic FPGA.http://www.ieechina.com

[4] 張欣.VLSI數(shù)字信號(hào)處理——設(shè)計(jì)與實(shí)現(xiàn).北京:科學(xué)出版社,2003.

[5] 張欣.?dāng)U頻通信數(shù)字基帶信號(hào)處理算法及其VLSI實(shí)現(xiàn).北京:科學(xué)出版社,2004.