數(shù)據采集系統(tǒng)是通過采樣電路將輸入的模擬信號轉換成離散信號,并送入CPU、MCU或DSP進行處理。現(xiàn)在流行的基于PCI總線設計的采集卡是數(shù)據采集系統(tǒng)的主流,其優(yōu)點是可以利用PCI總線的研究成果快速的開發(fā)系統(tǒng)軟件,整體運行速度快,能夠實現(xiàn)實時采集實時處理。但在一些工業(yè)測控現(xiàn)場檢測大型設備時,從現(xiàn)場到機房有一定的距離,模擬信號傳到安裝在PC內的PCI數(shù)據采集卡會有不同程度的衰減,且易受工業(yè)環(huán)境的干擾。而單純用由微控制器(MCU)為核心的數(shù)據采集系統(tǒng)時,把數(shù)據采集器置于被監(jiān)測的設備處,雖然可以避免模擬信號的衰減和被干擾,但在這種數(shù)據采集系統(tǒng)中,A/D轉換器的啟動、讀取數(shù)據并存入到存儲器的整個過程由MCU來參與控制,由于受MCU執(zhí)行指令時間的限制,采集的速率較低,難以適應高速信號采集的需要。本文利用ARM微處理器和CPLD器件組成的現(xiàn)場數(shù)據采集系統(tǒng),然后通過以太網接口于上位機相連,就可以有效解決上述問題。

系統(tǒng)的設計方案

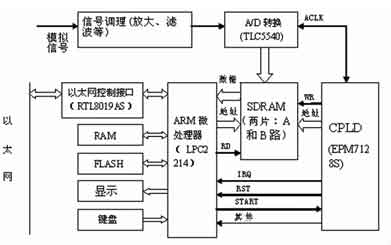

整個數(shù)據采集系統(tǒng)如圖1所示。數(shù)據采集系統(tǒng)首先對采集的信號進行前端處理,如信號放大、濾波等預處理。采用的CPLD器件實現(xiàn)整個系統(tǒng)的控制邏輯,它控制著采集通道的切換、A/D轉換的起/停、轉換后的數(shù)據存放在存儲單元的地址發(fā)生器、產生中斷請求以通知ARM讀取存放在存儲器中的數(shù)據,由ARM微處理器進行快速的處理和傳輸。

圖1 數(shù)據采集系統(tǒng)框圖

1 信號調理模塊

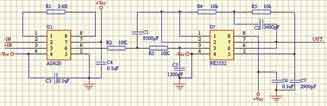

在信號進行數(shù)模轉換前,在保證被采集信號不失真的前提下,對輸入的信號進行放大、濾波等預處理。高速數(shù)據采集系統(tǒng)的輸入信號通常為高頻信號,需要進行阻抗匹配和前置放大,可以選用高速低噪聲信號前置放大器和信號變壓器。信號前置放大器的優(yōu)勢是:放大系數(shù)可變,信號輸入的動態(tài)范圍大,還可以配置成有源濾波器。但放大器的最高工作頻率和工作寬帶必須滿足系統(tǒng)設計的需要,避免信號失真,同時應該考慮放大器引入的噪聲損失,為避免對A/D轉換器性能的不利影響,前置放大器的信噪比應遠大于A/D轉換器的信噪比。當頻率遠遠大于100MHz時,盡可能采用信號變壓器,其性能指標(如最高工作頻率和工作帶寬)優(yōu)于信號放大器,而且信號失真很小,但信號放大系數(shù)固定,輸入信號的幅度受到限制。該設計中采用前置放大器,其前端的信號調理電路如圖2所示。

圖2 信號調理電路

2 A/D轉換模塊

將連續(xù)信號轉換成離散信號進而轉換成數(shù)字信號以適用于處理的重要芯片是A/D轉換器。一般的逐次逼進型A/D轉換芯片的轉換速度最多在每秒鐘幾萬次,不能滿足高速采樣的要求。該設計中選擇TI公司的TLC5540高速模數(shù)轉換芯片,其具有8位分辨率,內置采樣和保持電路,該芯片采用一種改進的半閃結構、CMOS工藝制造,因而大大減少了器件中比較器的數(shù)量,而且在高速轉換的同時,能夠保持低功耗,轉換速率可達40Mb/s。

TLC5540以流水線的工作方式進行工作,在每一個CLK周期均啟動一次采樣,完成一次采樣,每次啟動采樣是在CLK的下降沿進行,第n次采樣的數(shù)據經過3個時鐘周期的延遲之后,送到內部數(shù)據總線上,所以系統(tǒng)剛啟動時讀取的3個數(shù)據是無效數(shù)據,在軟件設計時,必須拋棄系統(tǒng)啟動時讀取的前3個數(shù)據。

3 CPLD模塊

該設計中采用ALTERA公司的EPM7128S, 它實現(xiàn)整個系統(tǒng)的控制邏輯。主要有下面幾個控制模塊電路構成:

- 時鐘控制電路,提供A/D轉換器的時鐘信號(ACLK),該信號同時提供了給存儲器的WR,以控制整個系統(tǒng)的采樣頻率。

- 地址產生電路,生成SRAM的地址控制信號,每寫完一次SRAM, 地址自動加1。

- 地址總線切換電路,對內部地址發(fā)生器和LPC2214產生的兩組地址進行切換,提供給存儲器。當處于寫存儲器時,存儲器的地址由內部地址發(fā)生器發(fā)生;當處于LPC2214讀存儲器時,存儲器的地址由LPC2214的地址總線提供。

- 數(shù)據總線切換電路,對A/D的數(shù)據線和LPC2214的數(shù)據總線進行切換,當寫數(shù)據時,使數(shù)據從A/D輸出到存儲器,讀數(shù)據時,使數(shù)據從存儲器讀到LPC2214的數(shù)據總線。

- 地址譯碼及邏輯控制電路,完成對系統(tǒng)地址總線的譯碼,產生各種必須的控制信號。

4 MCU模塊

該設計中采用Philips公司的LPC2214的微處理器,用它來對采集到的數(shù)據進行存儲、顯示、處理操作,并作為系統(tǒng)與上位機溝通的橋梁。LPC2214是基于ARM7TDMI核的RISC微處理器,ARM7TDMI為低功耗、高性能的16/32位核,最適合對價格及功耗敏感的場合。LPC2214在ARM7TDMI核的基礎上擴展了一系列通用外圍器件,使其特別適用于工業(yè)控制、醫(yī)療系統(tǒng)、訪問控制,由于內置了寬范圍的串行通信接口,使其也非常適用于通信網關、協(xié)議轉換器、嵌入式軟MODEM以及其他類型的應用。

5 ARM與網卡芯片接口設計

為使采集到的數(shù)據或處理后的數(shù)據傳送到上位機,需在系統(tǒng)中增加以太網接口,通常有兩種方法:(1)ARM微處理器+網絡控制器,這種方法對處理器沒有特殊的要求,只要把以太網芯片連接到處理器的總線上即可,此方法的通用性較強,不受處理器的限制;(2)采用帶以太網接口的ARM微處理器,但通常這種處理器往往是面向網絡應用而設計的,不是特別適用于工業(yè)領域。故該設計中選用第一種方法。

網路控制器RTL8019AS是目前比較常用的10Mb/s嵌入式以太網控制芯片,在芯片內部集成了DMA控制器,ISA總線控制器和16KB SRAM,網路PHY收發(fā)器。用戶可以通過DMA方式把需要發(fā)送的數(shù)據寫入片內SRAM中,讓芯片自動將數(shù)據發(fā)送出去;而芯片在接受到數(shù)據后,用戶也可以通過DMA方式將其讀出。

系統(tǒng)基本工作原理

數(shù)據采集器置于被監(jiān)控的設備處,對傳送過來的模擬信號進行信號調理,LPC2214啟動系統(tǒng)數(shù)據采集,CPLD控制器輸出一個脈沖給A/D轉換器的CLK端,使其開始第n次A/D轉換,同時將CPLD內部地址發(fā)生電路產生的地址信號經地址選擇器直接送到存儲器,A/D轉換器所采集到的第n-3次的數(shù)據經數(shù)據總線直接輸入到存儲器中保存。

由于采樣頻率高,用CPLD將采樣數(shù)據存儲到兩路同步動態(tài)存儲器(SDRAM)中。CPLD先把采集到的數(shù)據以DMA的方式存儲到A路SDRAM中。 等數(shù)據寫滿A路SDRAM后,由CPLD器件引起LPC2214外部中斷,LPC2214進入中斷處理程序,讀取SDRAM中的數(shù)據,并進行處理,同時CPLD將接下來采集到的數(shù)據以DMA的方式存儲到B路SDRAM中, 等存儲器B數(shù)據裝滿后,CPLD器件引起LPC2214外部中斷,LPC2214進入中斷處理程序,讀取B路SDRAM中的數(shù)據,并進行處理,如此循環(huán)下去,完成數(shù)據的接收和傳輸并行。

可以看到ARM微處理器只控制數(shù)據采集的啟動和對采集到的數(shù)據進行快速處理和傳輸,在數(shù)據采集的過程中,ARM微處理器不對采集通道進行任何控制,完全由硬件自動實現(xiàn)數(shù)據采集的全過程,實現(xiàn)了高速數(shù)據采集的目的。

系統(tǒng)軟件設計

軟件部分要分別編寫LPC2214的處理模塊程序和CPLD的控制模塊程序,LPC2214的程序包括嵌入式操作系統(tǒng)μC/OS-II和各應用程序的編寫,CPLD控制模塊程序用VHDL語言來實現(xiàn)。

在編寫處理器的處理程序時,如采用單任務順序機制,系統(tǒng)的安全性差,這對于穩(wěn)定性、實時性要求高的數(shù)據采集系統(tǒng)是不允許的,因此根據整個裝置實現(xiàn)的功能和對它的要求進行系統(tǒng)任務的分割,并分配優(yōu)先級,由操作系統(tǒng)來進行管理調度。本設計選用μC/OS-II操作系統(tǒng),μC/OS-II V2.52已通過美國航空航天管理局(FAA)的安全認證,其采用優(yōu)先級調度算法完成任務間的調度,支持搶占式調度,具有執(zhí)行效率高、占有空間小、實時性能優(yōu)良和擴展性強等特點,其內核還提供信號量、消息郵箱、消息隊列、內存管理等系統(tǒng)服務。程序架構如圖3所示。

圖3 程序架構圖

根據應用,本系統(tǒng)分為以下幾個任務:軟復位任務(程序對系統(tǒng)初始狀態(tài)進行重新設定),對SDRAM的讀取、與上位機的TCP/IP通信、顯示任務、鍵盤管理任務和數(shù)據處理任務,任務間的通信通過消息隊列來完成。系統(tǒng)中的每個任務包括應用程序、任務堆棧和任務控制塊三部分。任務控制塊是一個數(shù)據結構,當任務的CPU使用權被剝奪時,μC/OS-II用它來保存該任務的狀態(tài),當任務重新獲得CPU的使用權時,任務控制塊能確保任務從被中斷的那一點執(zhí)行下去,操作系統(tǒng)可以通過查詢任務控制塊的內容從而對任務進行調度管理。

在用μC/OS-II作為內核來編寫數(shù)據采集系統(tǒng)系統(tǒng)的應用軟件之前,必須完成μC/OS-II在微處理器的移植工作,由于μC/OS-II在設計之初就充分考慮了在不同處理器上的移植問題,其結構化設計把與處理器相關的部分分離出來,因此在任何處理器上的移植 μC/OS-II都只需要關心三個文件:頭文件OS_CPU.H、文件OS_CPU_C.C和匯編文件OS_CPU_A.ASM。

為了滿足系統(tǒng)與以太網直接交換信息的需要,本設計在μC/OS-II中移植了LWIP(Light Weight IP輕型IP協(xié)議)協(xié)議棧。LWIP是瑞士計算機科學院Adam Dunkels等開發(fā)的一套用于嵌入式系統(tǒng)的開放源代碼TCP/IP協(xié)議棧。LWIP可以移植到操作系統(tǒng)上,也可以在無操作系統(tǒng)的情況下運行,LWIP實現(xiàn)的重點是在保持TCP協(xié)議主要功能的基礎上減少對RAM的占用,一般它只需要幾十字節(jié)的RAM和40Kb左右的ROM就可以了。

LWIP可以很容易地在μC/OS-II的調度下,為系統(tǒng)增加網絡通信和網絡管理功能。LWIP把所有與硬件、操作系統(tǒng)、編譯器相關的部分獨立出來,放在/src/arch目錄下,因此LWIP在 μC/OS-II上的移植修改這個目錄下的文件即可。

結論

在ARM微處理器中移入嵌入式實時操作系統(tǒng)μC/OS-II,使系統(tǒng)的穩(wěn)定性、實時性得到保證,實時操作系統(tǒng)將應用分解成多任務,簡化了應用系統(tǒng)軟件的設計;采用CPLD器件集成了電路的全部控制功能,擺脫了單純用由微控制器為核心的數(shù)據采集系統(tǒng)時的速度瓶頸,極大提高了數(shù)據采集速度。整個系統(tǒng)具有速度高、實時性好、抗干擾能力強、性價比高等特點。