摘 要: 給出了基于Nios II" title="Nios II">Nios II的通用數(shù)字調(diào)制器" title="數(shù)字調(diào)制器">數(shù)字調(diào)制器的實現(xiàn)方法,具體說明了系統(tǒng)的基本原理、總體結(jié)構(gòu)、硬件設(shè)計,以及軟件流程等。該系統(tǒng)把可編程邏輯的固有優(yōu)勢集成到嵌入處理器的開發(fā)流程中,具有高度的靈活性、可重配置功能,便于升級和擴展,適于軟件無線電" title="軟件無線電">軟件無線電的應(yīng)用。

關(guān)鍵詞: Nios II 調(diào)制器 軟件無線電

在軟件無線電(SDR)的研究過程中,調(diào)制解調(diào)技術(shù)是無線通信系統(tǒng)空中接口的重要組成部分。目前常用的數(shù)字調(diào)制方式有多種,如果按照傳統(tǒng)的硬件實現(xiàn)方法,要使一部通信機產(chǎn)生多種調(diào)制信號,其系統(tǒng)就會非常龐大復(fù)雜。

altera" title="altera">altera.com/">Altera公司的Nios II處理器是用于可編程邏輯器件的可配置的軟核處理器。Nios II軟核處理器和存儲器、I/O接口等外設(shè)可嵌入FPGA中,組成一個可編程單芯片系統(tǒng)(SOPC),大大降低了系統(tǒng)的成本、體積和功耗。基于Nios II處理器系統(tǒng)的通用數(shù)字調(diào)制器是一種軟件化硬件的解決方案,可以產(chǎn)生多種模式的數(shù)字調(diào)制信號,具有多功能性、通用性、集成度高、易于升級等優(yōu)點,滿足軟件無線電系統(tǒng)的要求。

1 總體系統(tǒng)結(jié)構(gòu)

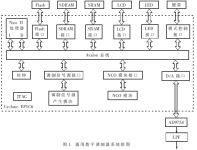

本系統(tǒng)在一個調(diào)制器中靈活多變地實現(xiàn)了多種調(diào)制功能。Nios II處理器完成人機交互和控制工作,F(xiàn)PGA邏輯從Nios II處理器接收控制信號和數(shù)據(jù)后完成相應(yīng)的硬件功能。系統(tǒng)整體框圖如圖1所示。Nios II軟核處理器、存儲器和I/O接口等外設(shè)可嵌入在FPGA中,這樣整個系統(tǒng)的數(shù)字處理部分全部集成在FPGA器件中。數(shù)控振蕩器(NCO)的各子模塊必須在Nios II處理器的控制下,不斷接收實時數(shù)據(jù)才能完成各種不同的數(shù)字信號調(diào)制。在某些情況下,這些數(shù)據(jù)傳輸是復(fù)雜的,好在Nios II處理系統(tǒng)有Avalon總線,它規(guī)定了控制器與從屬組件間的端口連接以及組件間通信的時序。NCO通過Avalon總線與Nios II處理器連接,可以簡單地看成外圍設(shè)備,很方便完成控制和數(shù)據(jù)傳輸。

本系統(tǒng)采用Nios II和CycloneEP1C6嵌入式系統(tǒng)開發(fā)板,選用AD9754作為DAC芯片,并用LC電路搭建了9階的橢圓低通濾波器,總體實現(xiàn)了一個可以產(chǎn)生多種調(diào)制信號的通用數(shù)字調(diào)制器。提供以下幾種調(diào)制方式:移頻鍵控調(diào)制(FSK)、二進制移相鍵控調(diào)制(BPSK)、四進制移頻鍵控(QFSK)、四相相移鍵控調(diào)制(QPSK)、標準載波輸出(Sin)。

調(diào)制方式和載波頻率可以通過撥碼開關(guān)和按鍵自由選擇,LED和LCD的顯示便于用戶直觀了解當前的狀態(tài)信息。系統(tǒng)工作過程中,當再次按下“啟動/停止”鍵時,可以對調(diào)制方式和頻率重新進行設(shè)置。

2 Nios II嵌入式軟核處理器簡介

Nios II嵌入式處理器是Altera公司推出的第二代用于可編程邏輯器件的可配置軟核處理器,最高性能超過200 DMIPS。Nios II是基于哈佛結(jié)構(gòu)的RISC通用嵌入式處理器軟核,能與用戶邏輯相結(jié)合,編程至Altera的FPGA中。處理器具有32位指令集、32位數(shù)據(jù)通道和可配置的指令以及數(shù)據(jù)緩沖。它特別為可編程邏輯進行了優(yōu)化設(shè)計,也為可編程單芯片系統(tǒng)(SOPC)設(shè)計了一套綜合解決方案。Nios II處理器系列包括三種內(nèi)核:高性能內(nèi)核(Nios II/f)、低成本內(nèi)核(Nios II/e)、性能/成本折中的標準內(nèi)核(Nios II/s)。本系統(tǒng)采用標準內(nèi)核。

Nios II 處理器支持256 個具有固定或可變時鐘周期操作的定制指令;允許Nios II設(shè)計人員利用擴展CPU指令集,通過提升那些對時間敏感的應(yīng)用軟件的運行速度來提高系統(tǒng)性能。

3 系統(tǒng)硬件設(shè)計

3.1 調(diào)制信號源

調(diào)制信號源可以來自外部,通過串口、并口等送入,也可以由調(diào)制器內(nèi)部產(chǎn)生。本系統(tǒng)由調(diào)制信號源產(chǎn)生模塊產(chǎn)生了偽隨機序列及其同步時鐘信號。

3.2 數(shù)字調(diào)制的實現(xiàn)

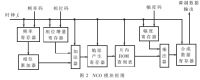

數(shù)字調(diào)制部分根據(jù)調(diào)制信號和來自CPU的控制信號產(chǎn)生可控模式、可控載頻的已調(diào)信號。NCO模塊包括頻率控制字寄存器、32位的相位累加器、相位控制字寄存器、相位-幅度變換電路、控制邏輯電路,以及相位抖動補償模塊,如圖2所示。NCO中各部件在參考頻率源的作用下同步工作。相位累加器在每一個時鐘上升沿與頻率控制字K累加一次。當累加器計數(shù)大于232時,相位累加器相當于做一次模余運算。正弦查詢表在每個時鐘周期內(nèi),根據(jù)送給ROM的地址(相位累加器的12個MSB相位值)取出ROM中已存儲的與該地址相對應(yīng)的正弦幅值,最后將該值送給DAC和LPF實現(xiàn)量化幅值到一個純凈信號的轉(zhuǎn)換。

由于資源和成本的原因,通常相位累加器輸出的32位不會全部用來尋址ROM,本系統(tǒng)取其高12位尋址 ROM,其余LSB位被舍去,這樣就不可避免地產(chǎn)生相位誤差,該誤差是NCO輸出雜散的主要原因。用于相位-幅度轉(zhuǎn)換的存儲器用片內(nèi)ROM來實現(xiàn),主要完成信號的相位序列到幅度序列之間的轉(zhuǎn)化。幅度量化誤差與波形存儲器數(shù)據(jù)總線位數(shù)相關(guān),本系統(tǒng)中為14位。

為了減小相位截斷誤差,要求在NCO的波形查表過程中保留更多的相位有效位;為了減小幅度量化誤差,要求波形存儲器保留更多的輸出數(shù)據(jù)位并選擇位數(shù)高的DAC。由于波形存儲器的容量受限,因此在低雜散設(shè)計中,可以通過改變傳統(tǒng)結(jié)構(gòu)中的相位到正弦波形的線性映射關(guān)系,采用新的結(jié)構(gòu)體系來降低波形存儲容量,以使在不增加波形存儲器容量的情況下,保留更多的相位有效位和數(shù)據(jù)總線位數(shù)。單象限正弦波存儲結(jié)構(gòu)是一種有效的方法。在這種結(jié)構(gòu)中,利用正弦波形的四分之一對稱性,將ROM表減至最初的1/4,波形存儲器只存儲一個象限[0,π/2]的波形。相位累加器用于波形尋址的有效位輸出中,最高兩位被用作映射四個象限,其余低位用來尋址波形存儲器。這樣,通過一個正/余弦表的前1/4周期就可以變換得到正/余弦的整個周期碼表。這種實現(xiàn)方法對存儲器的要求很小,節(jié)省了大量資源。

由相位截斷的分析理論,相位舍位序列是具有周期性的,如果能破壞其周期性,就能將DDS輸出頻譜中有規(guī)律的雜散分量變成隨機的相位噪聲,從而抑制相位截斷引起的雜散。因此本系統(tǒng)在ROM表之前加入了相位抖動注入模塊,通過隨機加擾的方法抑制DDS的相位截斷雜散。

本系統(tǒng)NCO輸出信號頻率fout與參考時鐘頻率fclk以及頻率控制字K之間的關(guān)系為 ,在96MHz參考時鐘的情況下,頻率分辨率為0.022 35Hz。

,在96MHz參考時鐘的情況下,頻率分辨率為0.022 35Hz。

3.3 D/A轉(zhuǎn)換與低通濾波

FPGA輸出的14位二進制數(shù)需要送到DAC進行D/A變換,得到量化的階梯波形輸出,最后經(jīng)低通濾波器濾除高頻分量,平滑后得到模擬的已調(diào)信號。DAC 非理想特性帶來的轉(zhuǎn)換誤差是影響輸出信號頻譜的又一因素,主要取決于DAC器件的性能。本設(shè)計選用AD9754作為DAC芯片。

用LC電路搭建了9階的橢圓低通濾波器,截止頻率為25MHz。其頻譜如圖3所示。

4 系統(tǒng)軟件設(shè)計

本系統(tǒng)的設(shè)計核心是根據(jù)調(diào)制信號的信息對載波頻率、相位和振幅進行精確控制。通過Nios II處理器來改變上述三個參數(shù)中的一個或幾個,以完成各種不同類型的調(diào)制。Nios II處理器的主要工作有:第一,針對不同的調(diào)制模式,輸出對應(yīng)的控制碼;第二,對某一具體的控制碼來說,要根據(jù)其控制信號的值、時鐘速率、相位累加器、ROM以及DAC位數(shù)等計算出具體的碼值。軟件流程如圖4所示。

通用數(shù)字調(diào)制器是實現(xiàn)軟件無線電的關(guān)鍵技術(shù)之一,現(xiàn)有文獻中的實現(xiàn)方法是通過“DSP+FPGA”來設(shè)計的,其外圍電路和控制邏輯復(fù)雜,成本較高。本文提出了一種基于Nios II嵌入式處理器軟核的通用數(shù)字調(diào)制器實現(xiàn)方法,使用Altera的低成本Cyclone FPGA,且具有開發(fā)周期短、成本低等特點。

本系統(tǒng)所實現(xiàn)的各種調(diào)制方式均已通過硬件測試,證明了方案的可行性和正確性。

此外,在設(shè)計過程中使用SignalTap II嵌入式邏輯分析儀可以方便調(diào)試,采用增量編譯可以縮短漫長的編譯等待時間。圖5是用SignalTap II對FSK分析時的截屏圖。

參考文獻

1 John G. Proakis,Masoud. Communication systems engineering.北京:電子工業(yè)出版社,2002

2 楊小牛,樓才義,徐建良. 軟件無線電原理與應(yīng)用. 北京:電子工業(yè)出版社,2001

3 傅豐林. Nios軟核心嵌入式處理器設(shè)計大賽優(yōu)秀作品精選. 西安:西安電子科技大學(xué)出版社,2005

4 Nios II software developer′s handbook. Altera Corporation,2005

5 Altera embedded peripherals handbook.Altera Corporation, 2005