摘 要: 分析了I2C串行總線的數(shù)據(jù)傳輸機(jī)制,用VHDL設(shè)計(jì)了串行總線控制電路,其中包括微處理器接口電路和I2C總線接口電路。采用ModelSim Plus 6.0 SE軟件進(jìn)行了前仿真和調(diào)試,并在Xilinx ISE 7.1i開(kāi)發(fā)環(huán)境下進(jìn)行了綜合、后仿真和CPLD器件下載測(cè)試。 結(jié)果表明實(shí)現(xiàn)了I2C串行總線協(xié)議的要求。

關(guān)鍵詞: I2C串行總線控制器 接口電路 VHDL CPLD

串行總線和并行總線相比具有結(jié)構(gòu)簡(jiǎn)單、占用引腳少、成本低的優(yōu)點(diǎn)。常見(jiàn)的串行總線有USB、IEEE1394、I2C等,其中I2C總線具有使用簡(jiǎn)單的特點(diǎn),在單片機(jī)、串行E2PROM、LCD等器件中具有廣泛的應(yīng)用。

I2C(Inter IC BUS)是Philips公司開(kāi)發(fā)的用于芯片之間連接的總線。 I2C總線用兩根信號(hào)線進(jìn)行數(shù)據(jù)傳輸,一根為串行數(shù)據(jù)線(SDA),另一根為串行時(shí)鐘線(SCL)。I2C總線允許若干兼容器件(如存儲(chǔ)器、A/D轉(zhuǎn)換器、D/A轉(zhuǎn)換器、LCD驅(qū)動(dòng)器等)共享總線。I2C總線理論上可以允許的最大設(shè)備數(shù),是以總線上所有器件的總電容(其中包括連線本身的電容和連接端的引出電容)不超過(guò)400pF為限,總線上所有器件依靠SDA線發(fā)送的地址信號(hào)尋址,不需要片選線。任何時(shí)刻總線只能由一個(gè)主器件控制,各從器件在總線空閑時(shí)啟動(dòng)數(shù)據(jù)傳輸。I2C總線數(shù)據(jù)傳輸?shù)臉?biāo)準(zhǔn)模式速率為100kbps,快速模式速率為400kbps,高速模式速率為3.4Mbps。

用VHDL和CPLD設(shè)計(jì)數(shù)字系統(tǒng)具有傳統(tǒng)方法無(wú)可比擬的優(yōu)越性,它已經(jīng)成為大規(guī)模集成電路設(shè)計(jì)最為有效的一種手段。為簡(jiǎn)單起見(jiàn),本文采用VHDL設(shè)計(jì)標(biāo)準(zhǔn)模式的I2C總線控制電路。

1 I2C總線上的數(shù)據(jù)傳輸

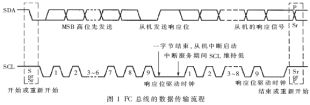

I2C總線包含時(shí)鐘線SCL和數(shù)據(jù)線SDA兩條連線,SCL由主機(jī)產(chǎn)生。I2C總線的數(shù)據(jù)傳輸流程如圖1所示。其傳輸過(guò)程為:首先主機(jī)產(chǎn)生起始位,然后傳送第一個(gè)字節(jié)。8位數(shù)據(jù)中首先傳送的是數(shù)據(jù)的最高位MSB,最低位LSB為讀寫(xiě)指示位,1表示主機(jī)讀,0表示主機(jī)寫(xiě),高7位地址可使主機(jī)尋址128個(gè)從器件。

從機(jī)收到第一字節(jié)數(shù)據(jù)后發(fā)響應(yīng)位,主機(jī)收到響應(yīng)位后接著發(fā)送第二個(gè)字節(jié)的數(shù)據(jù)。數(shù)據(jù)發(fā)送完畢后產(chǎn)生結(jié)束位,數(shù)據(jù)傳送結(jié)束。數(shù)據(jù)傳送時(shí),只有時(shí)鐘SCL為低電平時(shí)SDA才允許切換,SCL為高電平時(shí)SDA必須穩(wěn)定,此時(shí)SDA的電平就是總線轉(zhuǎn)送的數(shù)值。

在SCL為高電平時(shí),SDA線由高到低切換表示起始位,SDA線由低到高切換表示停止位。起始位和停止位由主機(jī)產(chǎn)生,在起始位產(chǎn)生后總線處于忙狀態(tài),停止位出現(xiàn)并經(jīng)過(guò)一定時(shí)間后總線進(jìn)入空閑狀態(tài)。發(fā)送器每發(fā)送一個(gè)字節(jié)后,接收器必須產(chǎn)生一個(gè)響應(yīng)位。響應(yīng)位的驅(qū)動(dòng)時(shí)鐘由主機(jī)產(chǎn)生則接收器將SDA線拉低產(chǎn)生響應(yīng)位。如果主機(jī)是接收器,則接收最后一個(gè)字節(jié)時(shí),響應(yīng)位為1,通知從機(jī)結(jié)束發(fā)送,否則響應(yīng)位為0。當(dāng)從機(jī)不能響應(yīng)從機(jī)地址(例如它正在執(zhí)行一些實(shí)時(shí)函數(shù),不能接收或發(fā)送)時(shí),或響應(yīng)了從機(jī)地址但在傳輸一段時(shí)間后不能接收更多的數(shù)據(jù)字節(jié),此時(shí)從機(jī)可以通過(guò)響應(yīng)位為1通知主機(jī)終止當(dāng)前的傳輸,于是主機(jī)產(chǎn)生一個(gè)停止位終止傳輸,或者產(chǎn)生重復(fù)開(kāi)始位開(kāi)始新的傳輸。

SDA線上傳送的數(shù)據(jù)必須為8位,每次傳送可以發(fā)送的字節(jié)數(shù)量不受限制。如果從機(jī)要完成一些其他功能(例如執(zhí)行一個(gè)內(nèi)部中斷服務(wù)程序)才能接收或發(fā)送下一個(gè)數(shù)據(jù)字節(jié),則從機(jī)可以使SCL維持低電位,迫使主機(jī)進(jìn)入等待狀態(tài)。從機(jī)準(zhǔn)備好接收或發(fā)送下一個(gè)數(shù)據(jù)字節(jié)時(shí),釋放SCL,數(shù)據(jù)傳輸繼續(xù)。

SDA和SCL都是雙向線路,使用時(shí)通過(guò)上拉電阻連接到電源。總線空閑時(shí)這兩條線路都是高電平,連接到總線的器件的輸出級(jí)必須是漏極開(kāi)路或集電極開(kāi)路,這樣總線才能執(zhí)行“線與”的功能。

主機(jī)發(fā)完第一個(gè)字節(jié)后,數(shù)據(jù)傳輸方向的變化可能存在三種情況。(1)傳輸方向不變,如主機(jī)向從機(jī)寫(xiě);(2)傳輸方向改變,如主機(jī)從從機(jī)讀數(shù)據(jù);(3)傳輸方向改變多次,如主機(jī)對(duì)從機(jī)進(jìn)行多次讀寫(xiě)。

2 時(shí)鐘同步與仲裁

I2C總線在任何時(shí)刻只能有一個(gè)主機(jī),當(dāng)I2C總線同時(shí)有兩個(gè)或更多的器件想成為主機(jī)時(shí),就需要進(jìn)行仲裁;時(shí)鐘同步的目的就是為仲裁提供一個(gè)確定的時(shí)鐘。時(shí)鐘SCL的同步和仲裁通過(guò)“線與”來(lái)執(zhí)行,SCL的低電平時(shí)間取決于低電平時(shí)間最長(zhǎng)的主機(jī),高電平時(shí)間取決于高電平時(shí)間最短的主機(jī)。

仲裁過(guò)程在數(shù)據(jù)線SDA線上進(jìn)行,當(dāng)SCL為高電平時(shí),如果SDA線上有主機(jī)發(fā)送低電平,則發(fā)送高電平的主機(jī)將關(guān)閉輸出級(jí)。因?yàn)榭偩€的狀態(tài)和自身內(nèi)部不一樣,于是發(fā)送低電平的主機(jī)贏得仲裁。仲裁可以持續(xù)多個(gè)位,在實(shí)際通信過(guò)程中,仲裁的第一階段比較地址位,如果多個(gè)主機(jī)尋址同一個(gè)從機(jī),則繼續(xù)比較數(shù)據(jù)位(主機(jī)是發(fā)送機(jī))或響應(yīng)位(主機(jī)是接收機(jī))。由于I2C總線上的地址和數(shù)據(jù)由贏得總線的主機(jī)決定,因此仲裁過(guò)程中不會(huì)丟失信息。如果一個(gè)主機(jī)具有從機(jī)功能,則當(dāng)它失去仲裁時(shí),必須立即切換到從機(jī)狀態(tài),因?yàn)樗赡苷诒黄渌鳈C(jī)尋址。

3 I2C總線控制器設(shè)計(jì)

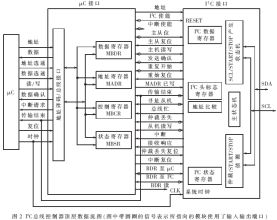

I2C總線控制器的主要作用是提供微控制器(μC)和I2C總線之間的接口,為兩者之間的通信提供物理層協(xié)議的轉(zhuǎn)換。在串行應(yīng)用系統(tǒng)中,外圍器件(如串行E2PROM、LCD、實(shí)時(shí)鐘等)連接在I2C總線上,再通過(guò)I2C總線控制器和μC連起來(lái)。其典型的應(yīng)用,如現(xiàn)在許多彩電的控制系統(tǒng)都基于I2C總線。為了使設(shè)計(jì)清晰明了,本文將控制器的設(shè)計(jì)分成兩部分。一部分為微控制器(μC)接口,另一部分為I2C接口,如圖2所示。

μC接口部分主要包含狀態(tài)寄存器(MBSR)、控制寄存器(MBCR)、地址寄存器(MADR)、數(shù)據(jù)寄存器(MBDR)和地址譯碼/總線接口模塊。狀態(tài)寄存器指示I2C總線控制器的當(dāng)前狀態(tài),如傳輸是否完成、總線是否忙等信息。控制寄存器是μC控制I2C總線控制器的主要途徑,通過(guò)置0/1完成I2C總線控制器使能、中斷使能、主/從(Master/Slave)模式選擇、產(chǎn)生起始位等操作。地址寄存器保存著I2C總線控制器作為從機(jī)時(shí)的地址。數(shù)據(jù)寄存器用于保存接收的數(shù)據(jù)或是待發(fā)送的數(shù)據(jù)。

I2C接口的核心是主狀態(tài)機(jī),它控制著整個(gè)I2C接口的運(yùn)作。和I2C總線直接相連的模塊有起始/停止位產(chǎn)生模塊、I2C Header寄存器、I2C數(shù)據(jù)寄存器和仲裁及起始/停止位檢測(cè)模塊。當(dāng)控制器是Master時(shí),起始/停止位產(chǎn)生模塊用于在I2C總線上產(chǎn)生起始位和停止位;I2C數(shù)據(jù)寄存器用于保存總線上傳送的數(shù)據(jù);仲裁及起始/停止位檢測(cè)模塊的作用是執(zhí)行仲裁,并檢測(cè)I2C總線上的起始/停止位,以便為主狀態(tài)機(jī)提供輸入。其他模塊包括:I2C狀態(tài)寄存器,用于記錄I2C總線的狀態(tài);地址比較模塊,用于比較總線上傳送的地址和本機(jī)的從機(jī)地址是否一致,如果一致,說(shuō)明其他主機(jī)正在尋址本控制器,控制器必須立即切換到從機(jī)狀態(tài),同時(shí)發(fā)出響應(yīng)位。

3.1 μC接口設(shè)計(jì)

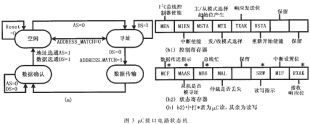

μC接口用于連接I2C接口電路和μC,主要實(shí)現(xiàn)兩者之間的信號(hào)交互握手機(jī)制。設(shè)計(jì)時(shí)可以用VHDL提供的狀態(tài)機(jī)來(lái)描述信號(hào)交互機(jī)制中的工作狀態(tài)切換,如圖3(a)所示。

μC接口電路中使用的四組寄存器的地址是24位的,高16位為I2C總線控制器的基址(MBASE),占用μC的地址空間,低8位用于區(qū)別不同的寄存器。寄存器本身是8位的,圖3(b1)為控制寄存器,圖3(b2)為狀態(tài)寄存器。圖中示出了每一位的含義。

3.2 I2C接口設(shè)計(jì)

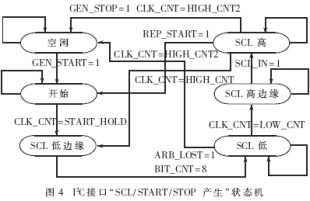

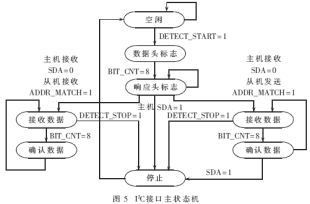

I2C接口用于連接μC接口電路和I2C總線,由兩個(gè)狀態(tài)機(jī)構(gòu)成:一個(gè)是I2C接口主狀態(tài)機(jī),用于執(zhí)行發(fā)送和接收操作;另一個(gè)為“SCL/SDA/ STOP 產(chǎn)生”狀態(tài)機(jī),當(dāng)I2C總線控制器為主機(jī)時(shí),這個(gè)狀態(tài)機(jī)產(chǎn)生SCL/START/STOP信號(hào)。

I2C接口用于I2C總線的驅(qū)動(dòng)和接收,當(dāng)I2C總線控制器為主機(jī)時(shí),I2C接口必須按I2C總線規(guī)范驅(qū)動(dòng)總線;當(dāng)總線控制器為從機(jī)時(shí),I2C必須能正確接收滿足I2C總線規(guī)范的信號(hào)。I2C設(shè)計(jì)規(guī)范對(duì)總線的時(shí)序作了詳細(xì)的定義,在不同模式下這些參數(shù)的具體數(shù)值都有明確的規(guī)定。“SCL/START/STOP 產(chǎn)生”狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換如圖4所示, I2C接口主狀態(tài)機(jī)的轉(zhuǎn)移圖如圖5所示。

4 仿真與硬件實(shí)現(xiàn)

本文中仿真工具采用Mentor公司的ModelSim Plus 6.0 SE,其顯著的優(yōu)越性能是提供了一個(gè)混合語(yǔ)言仿真環(huán)境,已在產(chǎn)業(yè)界廣泛應(yīng)用。為了測(cè)試驗(yàn)證系統(tǒng)的功能,本文采用了Atemel公司提供的采用I2C總線協(xié)議的AT24C02 E2PROM芯片(256B 8bit)的VerilogHDL仿真模型(AT24C02.v)作為從器件對(duì)象,用VerilogHDL語(yǔ)言構(gòu)建了testbench(測(cè)試向量),對(duì)所設(shè)計(jì)I2C總線控制器進(jìn)行仿真。

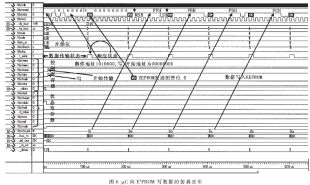

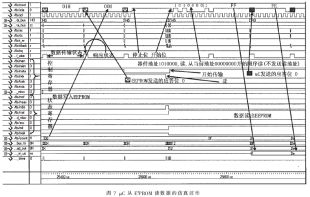

圖6和圖7為μC通過(guò)I2C總線控制器對(duì)E2PROM進(jìn)行數(shù)據(jù)寫(xiě)/讀的仿真波形(將數(shù)據(jù)FFH~0HH寫(xiě)進(jìn)地址0~255單元,然后將它們?cè)侔错樞蜃x的模式讀出)。往E2PROM寫(xiě)入時(shí)需要給出所寫(xiě)起始單元的地址(圖6中為00H); 從E2PROM順序讀時(shí)不用給出起始單元地址而從當(dāng)前地址處開(kāi)始讀(本文中寫(xiě)完256B數(shù)據(jù)后,地址指針又回到0處)。相關(guān)狀態(tài)及數(shù)據(jù)已在圖中作了標(biāo)示。由此可見(jiàn),所設(shè)計(jì)的總線控制器完全符合標(biāo)準(zhǔn)I2C串行協(xié)議的時(shí)序要求。

本文設(shè)計(jì)的系統(tǒng)實(shí)現(xiàn)平臺(tái)采用Xilinx公司的XC95216-10-PQ160 CPLD芯片,總邏輯門(mén)個(gè)數(shù)為4 800。經(jīng)綜合、適配、布局布線后占用器件資源的情況為:宏單元120/216(56%)、寄存器111/216(52%)、功能塊331/432(77%)、乘積項(xiàng)分配器544/1080(51%)。可見(jiàn),系統(tǒng)占用約一半的資源,相當(dāng)精簡(jiǎn)。整個(gè)系統(tǒng)下載到CPLD后在2MHz時(shí)鐘頻率下運(yùn)行正常。

參考文獻(xiàn)

1 王 誠(chéng),薛小剛,鐘信朝. FPGA/CPLD設(shè)計(jì)工具Xilinx ISE使用詳解.北京:人民郵電出版社,2005:439~478

2 劉 韜,樓興華. FPGA數(shù)字電子系統(tǒng)設(shè)計(jì)與開(kāi)發(fā)實(shí)例導(dǎo)航.北京:人民郵電出版社,2005:84~126

3 夏宇聞. 復(fù)雜數(shù)字電路與系統(tǒng)的Verilog HDL設(shè)計(jì)技術(shù). 北京:北京航空航天大學(xué)出版社,1998:110~136