引言

任意波形發(fā)生器(Arbitrary Wave Generator,以下簡稱AWG)在通信系統(tǒng)、測試系統(tǒng)等方面得到廣泛應(yīng)用。本文利用自主研制的150 MSPS (Million Sampling Per Second)12位DAC (Digital Analog Converter)和300MSPS 12位DAC,基于CPLD技術(shù),設(shè)計了一種AWG。要產(chǎn)生的波形通過上位機(jī)軟件設(shè)置,然后將波形數(shù)據(jù)下載到AWG,AWG在CPLD的高速控制電路下將波形數(shù)據(jù)送高速DAC進(jìn)行轉(zhuǎn)換形成所要的波形。下面先分析AWG的硬件結(jié)構(gòu)。

任意波形發(fā)生器的硬件結(jié)構(gòu)

AWG的工作過程是,首先接收上位機(jī)送來的波形數(shù)字信號存儲到SRAM,然后啟動控制電路從SRAM取出數(shù)據(jù)送DAC進(jìn)行數(shù)摸轉(zhuǎn)換,轉(zhuǎn)換后的模擬信號

送低通濾波器形成波形。如果DAC工作在150MSPS的速度下,可以以150MHz的頻率送數(shù)據(jù)到DAC進(jìn)行轉(zhuǎn)換,微控制器的晶振輸入一般工作在40MHz以下,沒有這么高的速度送出數(shù)據(jù)到DAC,所以考慮采用CPLD構(gòu)建硬件控制電路。數(shù)據(jù)首先傳送到SRAM,然后在CPLD硬件控制電路的控制下,以150MHz的頻率從SRAM中取數(shù)送DAC轉(zhuǎn)換。其體系結(jié)構(gòu)如圖一所示。如果要形成正弦周期信號,每周期4個點就可以合成一個波形,此時可以輸出約38MHz的高頻信號。

圖一 AWG硬件結(jié)構(gòu)

CPLD(Complex Programmable Logic Device,復(fù)雜可編程邏輯器件)是在傳統(tǒng)的PAL、GAL基礎(chǔ)上發(fā)展而來的,具有多種工作方式和高集成、高速、高可靠性等明顯的特點,在超高速領(lǐng)域和實時測控方面有非常廣泛的應(yīng)用。與FPGA相比,CPLD比較適合計算機(jī)總線控制、地址譯碼、復(fù)雜狀態(tài)機(jī)、定時/計數(shù)器、存儲控制器等I/O密集型應(yīng)用,且無須外部配置ROM、時延可預(yù)測等。目前的CPLD普遍基于E2PROM和Flash電可擦技術(shù),可實現(xiàn)循環(huán)擦寫。Altera 公司的MAX7000 CPLD配置有JTAG口,支持ISP編程。用VHDL或Verilog HDL(Hardware Description Language, 硬件描述語言)設(shè)計的程序,借助EDA工具經(jīng)過行為仿真、功能仿真和時序仿真后,通過綜合工具產(chǎn)生網(wǎng)表,下載到目標(biāo)器件,從而生成硬件電路。

本裝置中,CPLD采用Altera公司的EPM7128AE [4],其最高工作頻率達(dá)200MHz。微控制器采用Atmel公司AVR微控制器AT90S8515[2],其主要特征有:增強(qiáng)型RISC體系結(jié)構(gòu)CPU,8K Flash,512 字節(jié) EEPROM,512 字節(jié) Internal SRAM,UART,SPI,寬電壓范圍: 2.7 - 6.0V。SRAM選用64K x 16的CY7C1021V。

下面對CPLD控制電路進(jìn)行分析。

CPLD電路設(shè)計

CPLD主要負(fù)責(zé)以高速率(150MHz)從SRAM中取數(shù)到DAC,其核心電路是一個13位的計數(shù)器。波形數(shù)據(jù)文件的大小為8Kbytes。如果要擴(kuò)大波形文件的大小,可以根據(jù)需要增加CPLD的地址計數(shù)器容量。在CPLD內(nèi)部構(gòu)造的DAC控制電路如圖二所示,下面對其控制流程進(jìn)行分析。

PA[15:0]接AT90S8515的2個8位并行口;D[15:0]接SRAM的數(shù)據(jù)線D0-D15;AD[12:0]接SRAM的地址線A0-A12;DB[15:0]接DAC的D0-D11(D12-D15不用);CLK_SEL選擇計數(shù)器的時鐘輸入方式;CLK_AVR接MCU的一個I/O端,通過軟件編程在CLK_AVR輸出脈沖信號作為計數(shù)器的時鐘;CLK_CPLD接150MHz時鐘信號;/WR和 /WE接MCU的I/O端。

當(dāng)PC 機(jī)下載數(shù)據(jù)時,其控制流程如下:

① CLK_SEL=0,選擇軟件時鐘

② 復(fù)位地址計數(shù)器

③ MCU送數(shù)據(jù)到PA[15:0]

④ /WR從0變到1,打開從MCU到SRAM的數(shù)據(jù)緩沖器將數(shù)據(jù)寫入SRAM

⑤ 給CLK_AVR一個脈沖,讓計數(shù)器增1從而指向SRAM的下一個接收地址單元。

當(dāng)數(shù)據(jù)下載完成后, 啟動CPLD從SRAM取數(shù)據(jù)到DAC,其控制流程如下:

① WE=1,打開從SRAM到DAC的緩沖器。

② CLK_SEL=1,計數(shù)器的輸入時鐘選擇150MHz的外部時鐘,

③ 復(fù)位地址計數(shù)器,外部高速時鐘的驅(qū)動下地址計數(shù)器開始計數(shù),從SRAM中取出數(shù)據(jù)送到DAC進(jìn)行數(shù)據(jù)轉(zhuǎn)

換。

CPLD的編程在Quartus II 5.0環(huán)境下進(jìn)行,Quartus的設(shè)計輸入支持AHDL、VHDL、Verilog HDL等硬件描述語言的程序輸入和圖形輸入,這里采用圖形輸入的方式。完成設(shè)計輸入后,依次進(jìn)行編譯、功能仿真、時序仿真。下圖三是CPLD取數(shù)據(jù)到DAC進(jìn)行轉(zhuǎn)換的時序仿真結(jié)果。圖中CPLD的工作頻率為125MHz,實際工作中最高工作在200MHz,從圖中可以看出,每來一個時鐘,CPLD從SRAM中取出一個數(shù)據(jù)送DAC進(jìn)行A/D轉(zhuǎn)換。最后將結(jié)果下載到CPLD內(nèi)部運(yùn)行。

軟件設(shè)計

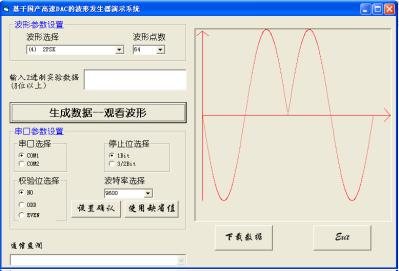

AWG的軟件采用CodeVision AVR C [3] 編寫,AT90S8515支持ISP(In System Programming, 在系統(tǒng)編程),程序編譯后經(jīng)JTAG口下載到AT90S8515中。為配合該裝置的使用,我們在VB開發(fā)環(huán)境下設(shè)計了上位機(jī)軟件,其運(yùn)行界面如圖四所示,在該軟件中選擇要產(chǎn)生的波形,然后下載到AWG。

AWG和PC機(jī)采用RS-232串口通信, 上電運(yùn)行后等待PC傳送波形,接收完波形數(shù)據(jù)后,啟動CPLD從SRAM中取出數(shù)據(jù)送DAC進(jìn)行D/A轉(zhuǎn)換,經(jīng)低通濾波器形成輸出波形。

圖四 波形數(shù)據(jù)產(chǎn)生軟件

結(jié)語

AWG和PC機(jī)通過RS232串口連接后,運(yùn)行PC機(jī)軟件,在PC機(jī)上選擇要生成的波形,生成波形數(shù)據(jù)下載到AWG,可以選擇線性調(diào)制技術(shù)的絕對相移鍵控(BPSK)、相對相移鍵控(DPSK)、四相相移鍵控(QPSK)、交錯正交相移鍵控(OQPSK)、π/4偏移差分相移鍵控(π/4—DQPSK),恒包絡(luò)調(diào)制的二進(jìn)制頻移鍵控(FSK)、最小頻移鍵控(MSK)、高斯濾波最小頻移鍵控(GMSK),混合線性和恒包絡(luò)調(diào)制技術(shù)的M相相移鍵控(MPSK)、多進(jìn)制正交幅度調(diào)制(QAM)、多進(jìn)制頻移鍵控(MFSK)等波形,下載到AWG生成所要的波形。下圖五是DAC工作在125MHz下合成的2FSK(Frequency Shift Key)波形。

圖五 2FSK波形

參考文獻(xiàn):

[1] 黃正謹(jǐn),徐堅等,CPLD系統(tǒng)設(shè)計技術(shù)入門與應(yīng)用,2002,北京

[2] Atmel Corp., AT90S8515 datasheet, 2002

[3] Atmel Corp., CodeVision AVR C Compiler Reference, 2002

[4] Altera Corp., MAX7000 Programmable Logic Device Family Data sheet, November,2001