DDS是直接數(shù)字合成(Direct Digital Synthesis)技術(shù)的簡(jiǎn)稱,是近年來隨著數(shù)字集成電路和計(jì)算機(jī)的迅猛發(fā)展而出現(xiàn)的一種新的頻率合成技術(shù)。該技術(shù)從相位概念出發(fā)來對(duì)頻率進(jìn)行合成。它采用數(shù)字取樣技術(shù),將參考信號(hào)的頻率、相位、幅度等參數(shù)轉(zhuǎn)變成一組取樣函數(shù),然后直接運(yùn)算出所需要的頻率信號(hào)。由于是全數(shù)字結(jié)構(gòu),其輸出信號(hào)中含有大量雜散譜線。另外,其超寬頻帶信號(hào)也將遇到諧波電平高,從而難以抑制諧波等問題。這些問題嚴(yán)重影響了DDS輸出信號(hào)的頻譜純度,也成為限制其應(yīng)用的主要因素。本文提出了一種解決此問題的電路方案,并對(duì)如何改善信號(hào)源的頻譜質(zhì)量進(jìn)行了討論。

1 AD9952芯片介紹

1.1 AD9952的主要特點(diǎn)

AD9952是ADI公司2003年推出的新產(chǎn)品。該芯片能以早期DDS芯片十分之一的功耗提供速度高達(dá)400MHz的內(nèi)部時(shí)鐘,可合成高達(dá)160 MHz的頻率。AD9952的主要性能如下:

●具有高達(dá)400MHz的內(nèi)部時(shí)鐘,可單端或雙端差分輸入,并附有PLL參考時(shí)鐘和可編程乘法器(4倍~20倍)。

●超低功耗,1.8V時(shí)的功耗小于250mW。

●內(nèi)部集成有14位DAC和超高速比較器,可產(chǎn)生高穩(wěn)定度的方波輸出。

●內(nèi)含32位相位累加器和19位正弦查詢表ROM。

●含有可編程的相位/幅度抖動(dòng)電路;可以減小由于相位截?cái)嗪停模粒昧炕`差帶來的雜散。

●DAC輸出相位噪聲小于-125dBc/Hz/1kHz;動(dòng)態(tài)性能為:80dB SFDR@130MHz(偏移±100kHz)。

●采用2線或3線串口控制,48腳EPAD-TQFP封裝形式。

1.2 AD9952的結(jié)構(gòu)原理

AD9952的內(nèi)部功能框圖如圖1所示。

AD9952共有6種時(shí)鐘輸入模式,通過ClkMode-Select管腳、CFR2<0>和CFR2<73>(CFR2為24位的第二控制功能寄存器)可決定使用哪種模式。

PLL的控制則通過控制功能寄存器的5位參考時(shí)鐘倍乘器來實(shí)現(xiàn)(即CFR2<73>)。當(dāng)編程數(shù)據(jù)在0X04~0X14(十進(jìn)制即:4~20)之外時(shí),PLL被旁路,此時(shí)PLL處于節(jié)電狀態(tài)。實(shí)驗(yàn)證明,直接使用參考晶振作時(shí)鐘時(shí),其輸出信號(hào)的相噪、雜散電平、SF-DR性能比使用倍乘器時(shí)有較大的改觀;而付出的代價(jià)是必須采用頻率較高的晶振,成本有所增加。

AD9952中的14位DAC可輸出兩路互補(bǔ)信號(hào),這種差分形式的輸出可減少DAC輸出可能存在的共模噪聲,提高信噪比。輸出電流由連接在DAC_RSET管腳與DAC地之間的Rset決定:

Rset=39.19/Iout

最大輸出電流為15mA,但是從最優(yōu)化SFDR的角度考慮,一般取輸出電流為10mA。

AD9952采用單點(diǎn)頻工作模式,與其他芯片相比功能上有些單一。凡是存儲(chǔ)在FTW0中的控制字就會(huì)被提供給相位累加器進(jìn)行累加;將一個(gè)新的控制字寫入FTW0并發(fā)出I/O UPDATE命令即可改變輸出頻率值。通過相位偏置寄存器可以調(diào)整輸出信號(hào)的相位。

AD9952內(nèi)部共有16個(gè)8位控制寄存器,可分別用來控制輸出信號(hào)的頻率、相位、幅度、同步以及器件操作等。與ADI公司先前的系列產(chǎn)品不同,AD9952只采用串口進(jìn)行控制。該串口可兼容多種同步傳輸格式,如:MOTOROLA 6905/11 SPI和IN-TEL8051 SSR協(xié)議等。

在AD9952的串口操作中,表1所列的指令字(Instruction Word)具有重要作用。其中指令字A<4:0>用于指定具體哪一個(gè)寄存器被訪問;MSB位為高時(shí),進(jìn)行讀操作;為低時(shí),進(jìn)行寫操作。

表1 AD9952的指令表

在每一個(gè)通信周期中,控制電路的前8?jìng)€(gè)時(shí)鐘周期用來寫入指令字,之后對(duì)應(yīng)于不同寄存器的數(shù)據(jù)被串行輸入到AD9952,傳送的字節(jié)數(shù)與被訪問的寄存器有關(guān)。比如:當(dāng)需要訪問CFR2寄存器時(shí),由于CFR2是3個(gè)字節(jié),所以,指令字后的3字節(jié)就默認(rèn)為是需要傳送的內(nèi)容。傳完3字節(jié),一個(gè)通信周期也就完成了。

2 XC2C128芯片介紹

XC2C128是Xilinx公司CoolRunnerⅡ系列中有128?jìng)€(gè)宏單元的CPLD器件。這種器件包含了16個(gè)內(nèi)部互聯(lián)的功能塊(AIM)每個(gè)AIM能為功能塊提供40個(gè)輸入,每個(gè)功能塊包含16個(gè)宏單元,這些宏單元同時(shí)包含了大量的配置寄存器。

另外,這些寄存器能被全局預(yù)置和復(fù)位,也可以被提前設(shè)置成D或T觸發(fā)器。可以有多種時(shí)鐘信號(hào),分別為全局或局部的電路服務(wù)。例如在同步時(shí),可以同時(shí)應(yīng)用三個(gè)不同的時(shí)鐘信號(hào)。

下面是XC2C128的一些主要特性:

●可采用1.5V、1.8V、2.5V、3V、3.3V等電源供電,XC2C128內(nèi)部有兩個(gè)BANK,因而允許采用不同電壓供電而不需電壓轉(zhuǎn)換器:

●片延時(shí)僅5ns;

●在1.8V供電時(shí),靜態(tài)電流可低至25μA;

●采用RealDigital CPLD技術(shù)和先進(jìn)的低功耗高速可編程邏輯技術(shù);具有低至33μW的靜態(tài)功耗;

●帶有輸入滯回和可編程地(GND),提高了高速I/O信號(hào)完整性;

●可提供多種封裝形式;

●采用通用的JTAG接口;

●帶有雙邊緣觸發(fā)器,因而速度更快;

●帶有多種LVCMOS、HSTL和SSTL I/O,其靈活的I/O可支持多種器件接口;

●具有四級(jí)設(shè)計(jì)保密功能;

●具有靈活的時(shí)鐘模式,可以直接采用外部時(shí)鐘,也可以利用內(nèi)部的時(shí)鐘分頻器(包括2、4、6、8、10、12、14、16分頻)。

3 基于CPLD和DDS的數(shù)頻源設(shè)計(jì)

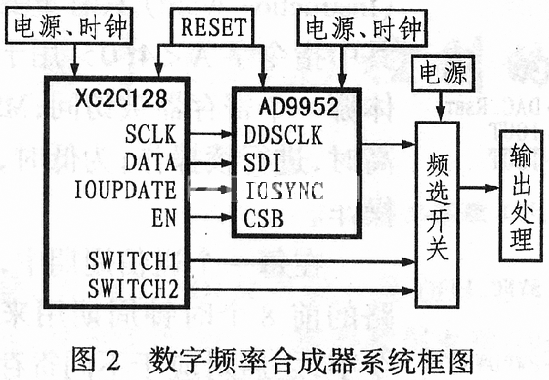

圖2所示是一個(gè)數(shù)字頻率合成器的總體框圖。圖中,先由CPLD芯片根據(jù)DDS需要的輸出頻率計(jì)算出頻率控制字,然后附上DDS寄存器地址輸出給DDS芯片,同時(shí)輸出一路信號(hào)給開關(guān),以便分段進(jìn)行后續(xù)處理。

為了實(shí)現(xiàn)極低噪聲,首先注意晶振的選取,因?yàn)楦鶕?jù)資料分析,輸出信號(hào)的相位噪聲取決于時(shí)鐘信號(hào)的相位噪聲,并將以20log(Fout/Fclk)的規(guī)律變化,這意味著在輸出信號(hào)頻率不變的情況下,10MHz時(shí)鐘信號(hào)所產(chǎn)生的相位噪聲將會(huì)比100MHz時(shí)鐘信號(hào)惡化20dB。所以必須選取相噪指標(biāo)極低的高頻率晶振作為DDS的時(shí)鐘。同樣,根據(jù)20log(Fout/Fclk)的公式,在時(shí)鐘不變的情況下,100MHz輸出信號(hào)的相位噪聲也會(huì)比10MHz輸出信號(hào)惡化20dB。

由于工作頻帶的相對(duì)帶寬很寬,因此降低輸出頻譜諧波電平是著重考慮的問題。如果按照原來的辦法,在輸出信號(hào)后加一級(jí)濾波器選擇信號(hào),那么無用的諧波分量就會(huì)混入到有用信號(hào)帶寬內(nèi),從而造成諧波電平超標(biāo),頻譜質(zhì)量降低。因此可以考慮將輸出信號(hào)頻帶分段,即由選通開關(guān)分配給幾組濾波鏈,最后再合成f1~f2 4.5倍頻程寬帶信號(hào);濾波器要求帶外抑制特性好,帶內(nèi)平坦度好,插損盡可能小。選通開關(guān)控制信號(hào)可由CPLD控制電路給出。

AD9952時(shí)鐘輸入采用雙端差模輸入,由外部晶振通過差分器提供。將時(shí)鐘工作模式的選擇管腳接地,即直接應(yīng)用參考時(shí)鐘頻率的工作模式。輸出IOUT和IOUT是一對(duì)互補(bǔ)信號(hào),這種差分形式可以減少輸出的共模噪聲、提高信噪比;DAC_RSET通過可調(diào)電阻接地,有利于找到能夠抑制噪聲的最佳的電阻值;DACBP通過一個(gè)0.01μF的電容接至模擬電源,可以改善其諧波失真和雜散電平性能;DDSRE-SET由按鍵開關(guān)控制,按下并抬起可形成一個(gè)寬幅脈沖來使AD9952復(fù)位;串口輸入控制由DDSCLK、DDSDATA、DDSCSB、DDSIOUPDATE組成,全部由控制電路輸出;它們之間的關(guān)系是:由DDSCLK提供串行時(shí)鐘,并在它的作用下DDSCSB由高變低時(shí),使DDS芯片處于使能狀態(tài),然后輸出一個(gè)完整的控制數(shù)據(jù)(包括寄存器地址和頻率控制字的內(nèi)容),之后再將DDSIOUPDATE由低變高,使已傳輸?shù)剑粒模梗梗担驳臄?shù)據(jù)產(chǎn)生作用并使輸出頻率發(fā)生跳變,從而完成了一個(gè)動(dòng)作。繼而完成CPLD作為控制電路要實(shí)現(xiàn)的主要功能。

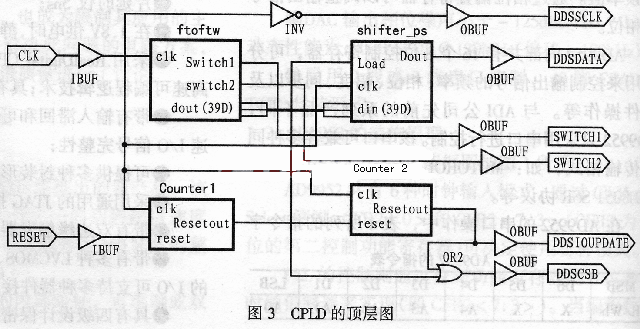

通過對(duì)AD9952的分析可知,控制電路必須輸出4組信號(hào)給DDS芯片,包括DDSDATA、DDSCSB、DDSSCLK和DDSIOUPDATE,同時(shí)還要輸出兩組信號(hào)給后面的頻選開關(guān)。DDSDATA信號(hào)是寄存器地址和頻率控制字的總和,共有40位;DDSCSB作為芯片的使能信號(hào)是單獨(dú)脈沖;DDSSCLK是串行時(shí)鐘,DDSIOUPDATE也是單獨(dú)脈沖。因此根據(jù)上面的分析,要實(shí)現(xiàn)DDSDATA、DDSCSB、DDSIOUPDATE信號(hào)都是很困難的。圖3是CPLD頂層的電路組成。

在CPLD內(nèi)部,為了簡(jiǎn)化設(shè)計(jì),重復(fù)性使用,常常將一部分功能做成模塊的形式。圖3的左上腳有一個(gè)頻率轉(zhuǎn)換模塊ftoftw,它的功能是根據(jù)要輸出的頻率(其典型值通過內(nèi)部預(yù)先設(shè)置的對(duì)應(yīng)表的查詢來實(shí)現(xiàn),非典型值則通過公式計(jì)算來實(shí)現(xiàn))來輸出想要的頻率控制字和附加的頻率寄存器地址。該模塊之所以采用查表方式是出于速度的考慮。圖3左下腳的模塊可將一個(gè)寬幅的按鍵RESET信號(hào)轉(zhuǎn)化成一個(gè)時(shí)鐘周期的RESET信號(hào),并且將輸出作為使能信號(hào)送到右邊的兩個(gè)模塊;該模塊內(nèi)部是由一個(gè)計(jì)數(shù)器來實(shí)現(xiàn)的,當(dāng)計(jì)到某一值時(shí)輸出一個(gè)脈沖,而后進(jìn)入一個(gè)無輸出的開循環(huán)以滿足單獨(dú)的脈沖輸出。右上腳的模塊是一個(gè)并串轉(zhuǎn)換模塊(shifter_ps),它可將40位的并行信號(hào)轉(zhuǎn)換成串行信號(hào),并在串行時(shí)鐘的參考下一位一位地輸出給DDS芯片,從而實(shí)現(xiàn)對(duì)寄存器的修改。這樣,給輸入時(shí)鐘加一個(gè)反門就可得到想要的串行時(shí)鐘,而且可以很方便地使之隨著輸入時(shí)鐘的變化而變化。右下腳的模塊是一個(gè)簡(jiǎn)單的計(jì)數(shù)器(counter2),它的輸出正是40個(gè)時(shí)鐘周期后的DDSIOUPDATE信號(hào),同時(shí)和前一個(gè)計(jì)數(shù)器的輸出通過或門得到DDSCSB信號(hào)。

該電路是數(shù)模混合電路,為了保證相噪和雜散性能,除了在原理設(shè)計(jì)和元器件選擇方面要注意外,在電路的具體布局和布線方面也要加以考慮,以防止額外干擾的產(chǎn)生。PCB采用4層板設(shè)計(jì),數(shù)字電源與模擬電源要分開,時(shí)鐘也要單獨(dú)供電;為降低電源紋波和其它干擾,還要對(duì)每一組電源分別用電容去耦。地平面上要將數(shù)字地和模擬地分開,并應(yīng)在大面積鋪地處通過一點(diǎn)連接,各相鄰地平面通過磁珠相連。時(shí)鐘盡量遠(yuǎn)離其它信號(hào),并應(yīng)加地線屏蔽。

4 結(jié)束語

直接數(shù)字頻率合成技術(shù)具有頻率轉(zhuǎn)換速度快、頻率分辨率高、輸出相位連續(xù)和全數(shù)字化、易于集成、易于控制等優(yōu)點(diǎn),是頻率合成器的理想選擇。采用CPLD控制能進(jìn)一步發(fā)揮DDS的優(yōu)勢(shì),本文針對(duì)具體的寬帶低噪聲頻率源給出了電路方案,對(duì)如何提高頻譜質(zhì)量進(jìn)行了一些探討。