10月29日消息,Intel首款采用Chiplets(芯粒)設(shè)計(jì)的桌面處理器Arrow Lake——酷睿Ultra 200S全球首發(fā)之后,其第一份“分解式”GPU設(shè)計(jì)專利也隨之曝光。

本月早些時候,Intel申請了一份分解式GPU架構(gòu)的專利,這可能是第一個具有邏輯小芯片的商業(yè)GPU架構(gòu)。

據(jù)了解,分解式GPU架構(gòu)將GPU的單芯片設(shè)計(jì),改為多個小型專用小芯片,然后使用相關(guān)技術(shù)互連。

通過將GPU劃分為小芯片,制造商可以針對特定使用場景(例如計(jì)算、圖形或AI)微調(diào)每個小芯片,從而發(fā)揮出最大效能。

此外,分解式GPU架構(gòu)的另一個巨大優(yōu)勢是節(jié)能。因?yàn)閱蝹€小芯片允許電源門控,這意味著當(dāng)它們不使用時,可以關(guān)閉電源以節(jié)省能源。

這種設(shè)計(jì)技術(shù)還帶來了其他一些好處,例如工作負(fù)載定制、模塊化和靈活性。在GPU設(shè)計(jì)領(lǐng)域,這種技術(shù)被視為未來的基準(zhǔn)。

其實(shí),AMD早在2022年就在RDNA3 GPU架構(gòu)第一次引入了chiplet小芯片設(shè)計(jì),包括一個GCD圖形核心、最多六個MCD顯存與緩存核心,但總體思路還是“一個大核心多個小核心”的思路。

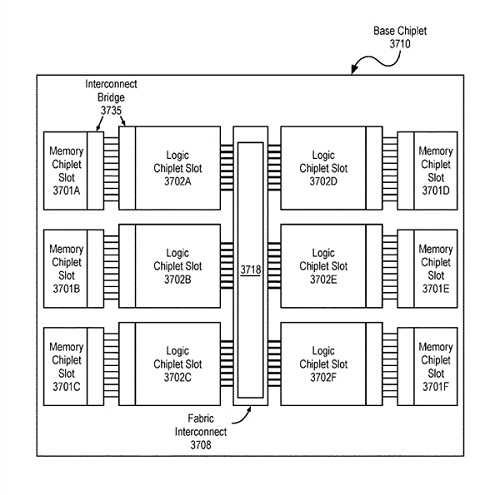

而Intel這份GPU架構(gòu)里面的邏輯小芯片,顯然每個各自獨(dú)立,且都有配套顯存模塊,可以看作是真正意義上的芯粒GPU。

事實(shí)上,隨著摩爾定律逼近極限,5nm以下制程突破面臨重重阻礙,Chiplet(芯粒)先進(jìn)封裝技術(shù)正是在這樣的背景下橫空出世。

在Chiplet思路下, 芯片被分割成較小的功能塊或核心,然后將這些“chiplet芯片粒”以先進(jìn)封裝技術(shù)集成在一起以構(gòu)建性能更強(qiáng)、更復(fù)雜化的芯片系統(tǒng)。

這種思路可以提高設(shè)計(jì)和封裝靈活性,使不同類型的芯片塊可以分別進(jìn)行優(yōu)化和制造,然后再通過先進(jìn)封裝技術(shù)集成在一起,以實(shí)現(xiàn)更高的性能和效率。

未來,無論是CPU、還是GPU,芯粒都是大勢所趨。

當(dāng)然, Intel這份專利何時才能落地,目前尚未可知。期待Intel未來能帶來好消息。