7 月 28 日消息,據(jù)外媒 TechRader 報道,富士通詳細(xì)介紹了計劃于 2027 年出貨的 FUJITSU-MONAKA(以下簡稱 MONAKA)處理器。

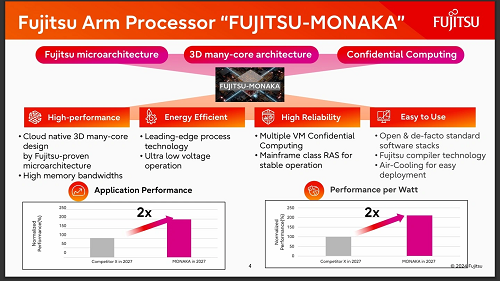

MONAKA CPU 基于“云原生 3D 眾核”架構(gòu),采用 Arm 指令集,面向數(shù)據(jù)中心、邊緣與電信領(lǐng)域,適用于 AI 計算,能實現(xiàn)大型機級別的 RAS1。

富士通表示,MONAKA 將在能效和性能方面實現(xiàn)飛躍:得益于超低電壓(ULV)工藝等技術(shù),該 CPU 可實現(xiàn) 2027 年競品 2 倍的能效,冷卻無需水冷;此外該處理器的應(yīng)用性能也可達(dá)對手 2 倍。

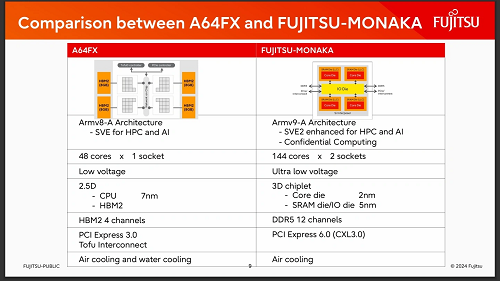

在指令方面,MONAKA 配備的矢量指令集升級至 SVE2,能更好滿足 AI 與 HPC 領(lǐng)域的需求;此外該 CPU 還新增了對機密安全計算的支持。

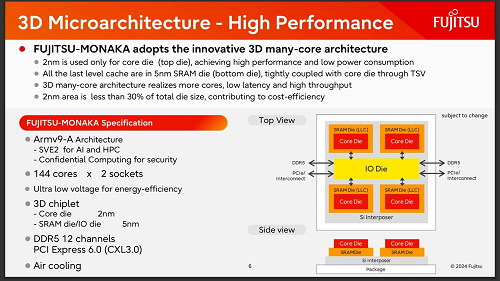

MONAKA 支持雙路,每顆 CPU 包含 144 個 Armv9 架構(gòu)核心。

其每顆 CPU 包括一個中央的 IO Die 和四個 3D 垂直堆疊復(fù)合體,底部則是連接各個部分的硅中介層(Si Interposer)與封裝層;

每個復(fù)合體又由處理器核心 Core Die 與 LLC 末級緩存 SRAM Die 組合而成,Core Die 位于 SRAM Die 上方。

MONAKA 的 Core Die 基于 2nm 工藝,下方的 SRAM Die 和中央的 IO Die 則建立在更成熟的 5nm 工藝上。

富士通表示,其處理器的 2nm 部分僅占整體 Die 面積的 30%,有助于實現(xiàn)更優(yōu)秀的成本效益。

由于片上的 3D 堆疊 SRAM 緩存已可提供卓越帶寬,MONAKA 處理器在在片外存儲上放棄了前代產(chǎn)品 —— 被用于“富岳”超算的 A64FX—— 使用的 HBM 內(nèi)存,采用了更為傳統(tǒng)的 12 通道 DDR5 內(nèi)存。

該處理器還可提供 PCIe 6.0 通道,支持 CXL 3.0 互聯(lián)。

注:

1RAS 即 Reliability(可靠性)、Availability(可用性)與 Serviceability(可維護性)的首字母簡寫。