隨著芯片制造工藝的不斷進(jìn)步,單個(gè)芯片的晶體管數(shù)量持續(xù)增長(zhǎng),從數(shù)萬(wàn)級(jí)到今天的數(shù)百億級(jí)。

長(zhǎng)期以來(lái),提高晶體管密度一直是實(shí)現(xiàn)更大規(guī)模集成電路的主要途徑,我們的關(guān)注點(diǎn)也一直聚焦在芯片制程的升級(jí)上。

但隨著工藝臨近物理極限,這種路徑已經(jīng)難以為繼,多芯片封裝技術(shù)的出現(xiàn)了,給了我們另一種提升晶體管數(shù)量和電路規(guī)模的途徑。

就像臺(tái)積電最近在IEDM展示的芯片技術(shù)線路圖那樣,在這張線路圖上有3D Hetero Integration和Monolithic Integration兩種不同的芯片集成方式:

1、3D Hetero Integration,即異質(zhì)3D集成技術(shù)。它是通過垂直堆疊和互連多個(gè)不同功能的裸芯片(Chiplet),實(shí)現(xiàn)芯片堆疊的一種封裝與互連技術(shù)。其優(yōu)點(diǎn)是可以混合匹配不同工藝節(jié)點(diǎn)的芯片,實(shí)現(xiàn)更高性能密度。

2、Monolithic Integration,即單體芯片一體化技術(shù)。它是在一塊硅基板上,使用統(tǒng)一的制造工藝集成不同功能的電路元件,產(chǎn)出單個(gè)大規(guī)模的復(fù)雜芯片。其優(yōu)點(diǎn)是信號(hào)傳輸更快,芯片之間沒有互連瓶頸。

兩者都是實(shí)現(xiàn)大規(guī)模集成電路的重要方式。3D Hetero Integration依賴封裝技術(shù),Monolithic Integratio則依賴制程技術(shù),在兩者共同作用下,臺(tái)積電預(yù)計(jì)在2030年前后實(shí)現(xiàn)整合超過1萬(wàn)億個(gè)晶體管的芯片解決方案,單體芯片的晶體管數(shù)量也在快速增長(zhǎng)到2000億級(jí),工藝制程將來(lái)到1納米。

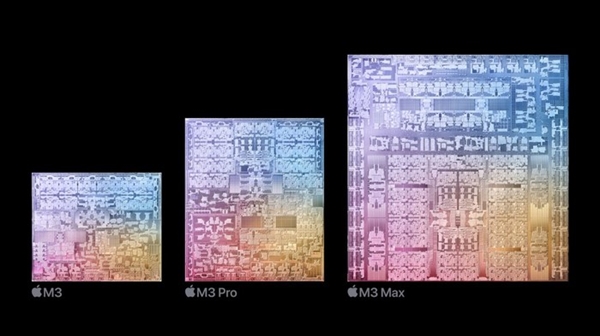

目前最大規(guī)模的單體芯片是蘋果的M3 Max,這顆芯片中的晶體管數(shù)量達(dá)到920億個(gè),采用最先進(jìn)的臺(tái)積電3nm工藝制造。而在上一個(gè)工藝節(jié)點(diǎn)上(臺(tái)積電4nm),最大的單體芯片是NVIDIA的H100 GPU,其核心集成有800億個(gè)晶體管,芯片面積為814平方毫米。

至于多芯片集成方案,多見于AMD和英特爾的數(shù)據(jù)中心加速卡上,比如AMD今年推出的Instinct MI300X AI加速卡,借助臺(tái)積電SoIC 3D片間堆疊和CoWoS先進(jìn)封裝技術(shù),其內(nèi)部集成了12個(gè)5/6nm工藝的小芯片(HMB和I/O為6nm),晶體管數(shù)量達(dá)到驚人的1530億個(gè)。

而英特爾的Ponte Vecchio集成了47個(gè)FPGA和HPC加速器芯片,整套芯片包含了驚人的1000億個(gè)晶體管。

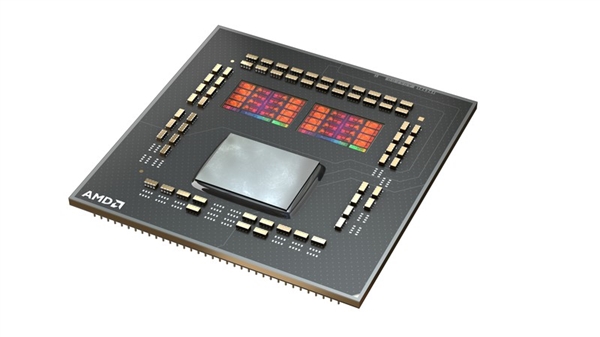

在面向普通用戶的產(chǎn)品中,AMD比Intel更早采用了多芯片封裝技術(shù)。早在2017年發(fā)布的EPYC服務(wù)器處理器中,AMD就使用了多芯片模組(MCM)方案,在同一個(gè)處理器封裝內(nèi)集成了多個(gè)芯片級(jí)別的組件。

在2019年,該技術(shù)應(yīng)用于Ryzen系列消費(fèi)級(jí)處理器中,采用Zen2架構(gòu)的AMD Ryzen 3000系列,首次使用晶片分離設(shè)計(jì),其核心部分使用成本較高的臺(tái)積電7nm,IO部分使用12nm,最后將核心和IO兩個(gè)部分集成在同一塊基板上。

隨后,AMD持續(xù)優(yōu)化了Chiplet架構(gòu),使AMD在性能和性價(jià)比上都占據(jù)明顯優(yōu)勢(shì),獲得了巨大商業(yè)成功。

相比之下,Intel直到2024年底發(fā)布的酷睿Ultra處理器中,才在消費(fèi)級(jí)產(chǎn)品上使用了多芯片集成封裝技術(shù),雖然比AMD的Ryzen系列稍晚,但這標(biāo)志著x86芯片制造商全面進(jìn)入多芯片時(shí)代。

酷睿Ultra具有Compute Tile、Graphics Tile、SoC Tile和I/O Tile四個(gè)小芯片,通過英特爾Foveros 3D封裝技術(shù)連接到一起,在核心架構(gòu)上實(shí)現(xiàn)了異構(gòu)整合。

據(jù)Intel介紹,F(xiàn)overos 3D封裝技術(shù)的核心是通過微觸點(diǎn)(Microbump)在邏輯芯片基板上垂直堆疊多個(gè)裸露芯片,并用TSV(通孔)實(shí)現(xiàn)芯片間的信號(hào)垂直互聯(lián)。這種垂直3D封裝方式可以實(shí)現(xiàn)異構(gòu)芯片的混合封裝和匹配,其空間效率和性能密度都很高,大大提升了芯片設(shè)計(jì)的靈活性。

毫無(wú)疑問,多芯片集成封裝技術(shù)已經(jīng)成為現(xiàn)在乃至未來(lái)五年芯片發(fā)展的重要技術(shù),同時(shí)也讓我們對(duì)過去封裝技術(shù)的演進(jìn)產(chǎn)生了興趣。

芯片封裝的發(fā)展歷史和代表產(chǎn)品:

1、DIP封裝:雙列直插封裝,1970-1980年代流行,典型產(chǎn)品為8086 CPU。

2、PGA封裝:帶連接孔的封裝形式,因Intel 80486而流行。

3、PQFP封裝:塑料四方扁平封裝,應(yīng)用于1990-2000年代的微處理器。

4、BGA封裝:球柵陣列,以Pentium作為典型產(chǎn)品,90年代中后期流行。

5、Flip Chip CSP: 翻轉(zhuǎn)芯片芯片級(jí)封裝,應(yīng)用于Intel Core和AMD Athlon系列CPU。

6、MCM封裝:多芯片模塊封裝,EPYC服務(wù)器處理器。

7、Chiplet封裝:面向現(xiàn)代處理器和AI加速器,如Zen 4和Intel Ponte Vecchio采用。

隨著芯片的小型化和功能的增加,封裝技術(shù)也在不斷發(fā)展,以滿足電性能和成本的需求。

這些多樣的封裝互連技術(shù)也必將不斷演進(jìn)與創(chuàng)新,推動(dòng)產(chǎn)業(yè)實(shí)現(xiàn)更高性能與復(fù)雜度的異質(zhì)融合芯片,以滿足AI、高性能計(jì)算等應(yīng)用的持續(xù)需求。制程與封裝的協(xié)同發(fā)展,也將開啟電子信息產(chǎn)業(yè)新的成長(zhǎng)空間。