本文作者: 李飛

本文來源:半導(dǎo)體行業(yè)觀察

原文鏈接:https://mp.weixin.qq.com/s/KZO_pWsdWN6p0cBcBN7lgQ

六月底,來自中科院的團(tuán)隊(duì)在預(yù)印本平臺(tái)arxiv上發(fā)表了重磅論文《Pushing the Limits of Machine Design:Automated CPU Design with AI》(機(jī)器設(shè)計(jì)新突破:使用人工智能自動(dòng)設(shè)計(jì)CPU),其中使用了人工智能的方法,成功地在5個(gè)小時(shí)內(nèi)完成了一個(gè)基于RISC-V指令集的CPU的設(shè)計(jì),而且該設(shè)計(jì)經(jīng)過后端布局布線后已經(jīng)成功流片點(diǎn)亮并且能運(yùn)行Linux和Dhrystone。

該論文一經(jīng)發(fā)表,就得到了半導(dǎo)體業(yè)界的廣泛關(guān)注,我們認(rèn)為,該論文中提出的方法有其歷史淵源,但是團(tuán)隊(duì)提出了對于已有方法的一種從數(shù)學(xué)角度來看很優(yōu)美的改進(jìn),從而能夠讓基于機(jī)器學(xué)習(xí)的自動(dòng)芯片設(shè)計(jì)成為現(xiàn)實(shí)。

首先,我們回顧一下現(xiàn)有的數(shù)字芯片設(shè)計(jì)流程。主流的芯片設(shè)計(jì)流程是,芯片設(shè)計(jì)師首先描述數(shù)字邏輯設(shè)計(jì),而EDA工具軟件則把這樣的電路描述映射到完全等價(jià)的數(shù)字邏輯電路。在這個(gè)過程中,整個(gè)數(shù)字邏輯或者是用Verilog等硬件描述語言來描述(常常是芯片設(shè)計(jì)師使用的描述方法),或者是使用等價(jià)的布爾邏輯圖的形式來描述(常見于一些EDA軟件的內(nèi)部優(yōu)化過程中)。布爾邏輯圖和硬件設(shè)計(jì)語言兩者是等價(jià)的,其特點(diǎn)就是能夠完全描述數(shù)字邏輯。例如,如果是一個(gè)簡單的有n比特輸入的組合邏輯,那么在描述中就需要能夠生成一張布爾邏輯表格(真值表),該表格需要能覆蓋所有2^n種輸入比特組合的對應(yīng)輸出。而對于時(shí)序邏輯,則還需要考慮內(nèi)部狀態(tài)比特,需要的表格就更大了。

與之相對應(yīng)的是,基于機(jī)器學(xué)習(xí)的自動(dòng)設(shè)計(jì)關(guān)注的問題是:如果我們只給出真值表的一部分,能否同樣可以生成正確的數(shù)字邏輯?舉例來說,該論文中針對的CPU自動(dòng)生成的問題,其中有1798個(gè)輸入和1826個(gè)輸出,在這種情況下如果直接使用真值表需要(2^1798)*1826大小的真值表,這樣大的真值表基本上是不可能在合理的時(shí)間內(nèi)生成的,而且也沒有可行的算法來處理如此大的真值表。對此,論文提出的觀點(diǎn)是,可以使用一種新的算法,該算法可以只使用真值表的一小部分來訓(xùn)練,就能夠生成自動(dòng)推理出真值表的其他部分,并且保證有很高的準(zhǔn)確度。因此,設(shè)計(jì)流程就變成了:用戶提供一個(gè)芯片邏輯真值表的一部分(需要是高質(zhì)量數(shù)據(jù),能夠抓住電路邏輯的主要特點(diǎn)),機(jī)器學(xué)習(xí)算法根據(jù)這個(gè)邏輯真值表自動(dòng)推理并補(bǔ)全真值表的其他部分,并且把該完整真值表送到傳統(tǒng)的EDA工具里去做邏輯綜合和物理設(shè)計(jì)。因此,電路設(shè)計(jì)流程也就由大量人工參與邏輯設(shè)計(jì)迭代(下圖a)變成了用戶提供一個(gè)輸入輸出數(shù)據(jù)集,AI直接綜合出邏輯和電路(下圖b)。

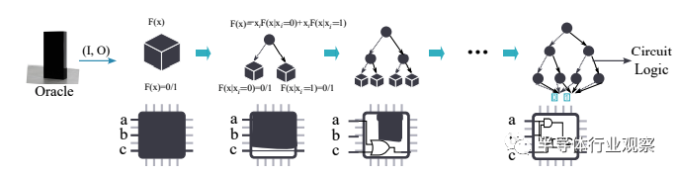

為了實(shí)現(xiàn)這樣的功能,論文提出了BSD算法。BSD算法的本質(zhì)是一種動(dòng)態(tài)圖算法:對于任意的邏輯,它首先生成一個(gè)初始的圖(例如,無論輸入如何輸出都是0);然后隨著用戶提供更多的輸入輸出數(shù)據(jù)(即提供真值表的一部分),BSD的圖會(huì)隨之更新(添加更多邊和節(jié)點(diǎn)),從而讓BSD對應(yīng)的邏輯能夠滿足用戶提供的真值表。例如,在一比特加法器的例子中,一開始的BSD邏輯圖對應(yīng)的是一個(gè)輸出永遠(yuǎn)是0的簡單邏輯,但是隨著用戶給出更多的輸入輸出的數(shù)據(jù),BSD圖也在不斷地修正,最后當(dāng)用戶給出足夠多的數(shù)據(jù)時(shí)(不一定需要給出真值表的全部),BSD就收斂到了正確的一比特加法器邏輯。

如前所述,這樣得到的BSD可以通過推理的方法來補(bǔ)完整個(gè)真值表,但是這樣的真值表對于現(xiàn)有的EDA軟件來說會(huì)太大而無法處理,因此論文又提出了一種BSD圖的處理方法可以把一個(gè)大的BSD分解成多個(gè)子BSD,并且在每個(gè)子BSD中進(jìn)行圖節(jié)點(diǎn)合并以進(jìn)一步減小BSD圖的大小,最后能把BSD圖中的節(jié)點(diǎn)縮減到一百萬個(gè)左右,從而EDA工具可以輕松處理。

為了驗(yàn)證該算法的有效性,團(tuán)隊(duì)選擇了RISC-V處理器作為目標(biāo)設(shè)計(jì)。具體來說,在數(shù)據(jù)集方面,論文團(tuán)隊(duì)使用RISC-V模擬器隨機(jī)生成了2^40組輸入輸出數(shù)據(jù)作為訓(xùn)練數(shù)據(jù),另一方面團(tuán)隊(duì)把之前RISC-V設(shè)計(jì)中使用的測試樣例(通常是最具有代表性的輸入輸出數(shù)據(jù))也加入了訓(xùn)練集中。值得注意的是,RISC-V CPU的輸入和輸出分別有1789和1826個(gè),因此理論上完整真值表需要有1826*(2^1789)個(gè)輸入輸出數(shù)據(jù),而團(tuán)隊(duì)使用的訓(xùn)練數(shù)據(jù)集只是完整真值表所需數(shù)據(jù)微不足道的一小部分,同時(shí)也可以在合理的時(shí)間內(nèi)產(chǎn)生出來。

之后,團(tuán)隊(duì)使用了該訓(xùn)練集在5小時(shí)內(nèi)完成了算法的訓(xùn)練,并且把生成的BSD送入EDA軟件中進(jìn)行綜合,在經(jīng)過FPGA驗(yàn)證后進(jìn)行了流片,最后CPU芯片能跑在300MHz時(shí)鐘頻率并且能成功運(yùn)行Linux和Dhrystone。

BSD模型對于芯片設(shè)計(jì)方法學(xué)的影響

我們認(rèn)為,該論文中提出的設(shè)計(jì)方法對于未來的芯片設(shè)計(jì)可能有深遠(yuǎn)的影響。

首先,該論文中的算法訓(xùn)練時(shí)間僅僅為5小時(shí),這樣的時(shí)間遠(yuǎn)遠(yuǎn)小于常規(guī)的處理器完成設(shè)計(jì)的時(shí)間——即使是所有的架構(gòu)定義和輸入輸出樣例都已經(jīng)完備,人工完成這樣的設(shè)計(jì)需要的時(shí)間至少是在幾周到一個(gè)月的級別,這遠(yuǎn)遠(yuǎn)高于5小時(shí)的訓(xùn)練時(shí)間。更重要的是,未來隨著計(jì)算平臺(tái)算力的升級,該算法訓(xùn)練需要的時(shí)間可望進(jìn)一步減小:以目前每兩年人工智能算力翻倍的勢頭來看,大約五年內(nèi)該訓(xùn)練時(shí)間就可以做到一小時(shí)以下。

其次,該算法是典型的數(shù)據(jù)驅(qū)動(dòng),需要大量的高質(zhì)量數(shù)據(jù)。這意味著未來對于芯片設(shè)計(jì)來說,如何產(chǎn)生這些數(shù)據(jù)會(huì)非常重要。在論文中,我們可以看到這些數(shù)據(jù)來源于RISC-V處理器的功能模擬器(simulator),換句話說未來芯片設(shè)計(jì)師的任務(wù)可能會(huì)更加集中到上層的功能定義以及描述(例如使用Python或者C語言對于芯片的功能進(jìn)行建模)。類似的使用高級語言來描述電路并實(shí)現(xiàn)綜合的嘗試已經(jīng)有十余年(例如高級語言綜合High level synthesis,HLS等),但是獲得的成功一直有限,僅僅在一些特定的電路中獲得應(yīng)用;而如今使用機(jī)器學(xué)習(xí)的方法配合高級語言進(jìn)行電路功能描述可能是實(shí)現(xiàn)類似高級語言綜合的一個(gè)可行路徑。

最后,雖然論文中使用機(jī)器學(xué)習(xí)直接產(chǎn)生了一個(gè)CPU這樣的大型設(shè)計(jì),但是從產(chǎn)業(yè)界的角度,更有可能的做法是從中小型IP開始,搭建一個(gè)基于AI的設(shè)計(jì)平臺(tái),并且在經(jīng)過幾輪迭代后再漸漸推廣到更大的設(shè)計(jì),并且最終簡化設(shè)計(jì)的流程。

BSD與其他人工智能如何進(jìn)一步推動(dòng)芯片設(shè)計(jì)

我們認(rèn)為,BSD的提出是一個(gè)自動(dòng)設(shè)計(jì)的一個(gè)突破,因?yàn)樗蚱屏酥霸O(shè)計(jì)綜合需要完整真值表的限制。同時(shí),我們也認(rèn)為接下來BSD算法會(huì)進(jìn)一步迭代并取得更好的結(jié)果,并且和其他人工智能算法一起進(jìn)一步簡化芯片設(shè)計(jì)。

首先,論文中提到的BSD的搭建是從零開始,并且通過訓(xùn)練數(shù)據(jù)來完成創(chuàng)建。一個(gè)有可能的未來發(fā)展方向是,如何從一個(gè)基礎(chǔ)參考設(shè)計(jì)開始做一定的改動(dòng),來實(shí)現(xiàn)一個(gè)新的設(shè)計(jì)?類似的參考設(shè)計(jì)方法是芯片設(shè)計(jì)行業(yè)的常規(guī)操作,而在人工智能業(yè)界,相對應(yīng)的做法就是預(yù)訓(xùn)練和微調(diào)——即在較大的訓(xùn)練數(shù)據(jù)集上進(jìn)行訓(xùn)練實(shí)現(xiàn)一個(gè)基礎(chǔ)模型,然后使用一個(gè)較小的數(shù)據(jù)集來微調(diào)來滿足定制化。如果未來BSD能實(shí)現(xiàn)這樣的參考設(shè)計(jì)和微調(diào),那么將進(jìn)一步減小對于用戶產(chǎn)生數(shù)據(jù)量的需求和訓(xùn)練時(shí)間,從而進(jìn)一步提升BSD的使用體驗(yàn)。

其次,BSD可以和其他人工智能算法結(jié)合來進(jìn)一步提升設(shè)計(jì)的效率。例如,目前的ChatGPT類大語言模型對于Python已經(jīng)有了很好的支持,但是對于Verilog等語言的支持以及設(shè)計(jì)流程的支持還不夠完備;在未來,對于一個(gè)芯片IP的設(shè)計(jì),我們可望看到ChatGPT類大語言模型去幫助生成上層使用Python描述的功能模型,使用該功能模型去生成輸入輸出數(shù)據(jù),然后使用BSD來完成最終的數(shù)字邏輯設(shè)計(jì)。

綜合上述的分析,我們認(rèn)為BSD有希望成為未來EDA流程中的重要一環(huán),它可以幫助推動(dòng)高級語言邏輯綜合,同時(shí)也可望和其他人工智能大語言模型一起進(jìn)一步簡化芯片設(shè)計(jì)流程,并且大大降低芯片設(shè)計(jì)需要的時(shí)間和成本。未來的芯片設(shè)計(jì)中,對于芯片設(shè)計(jì)師的要求越來越多會(huì)集中到更上層的功能定義,而不是具體的邏輯編寫。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<