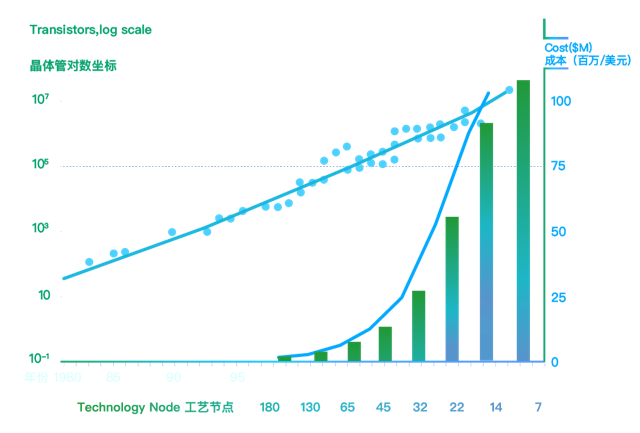

近年來,隨著大規(guī)模集成電路制造工藝發(fā)展速度減緩,相對于線性提升的芯片規(guī)模,芯片的制造成本呈現(xiàn)指數(shù)級上升,下圖可以很清晰地看到兩種趨勢變化。

圖1 芯片晶體管規(guī)模與制造成本提升趨勢

(數(shù)據(jù)來源:美國DARPA)

這些數(shù)字表明,我們正在為越來越復(fù)雜的芯片付出得越來越多。但是從1990年代到2000年代的經(jīng)驗(yàn)好像并不是這樣:每一代電腦手機(jī)價(jià)格漲得并不多,但是性能總是有大幅增長,甚至性價(jià)比都是在提高的,更好的電子產(chǎn)品甚至越來越便宜。為什么現(xiàn)在我們的感覺變化了?

這里有兩方面的原因:第一,過去很長時(shí)間里消費(fèi)電子的用戶數(shù)量在指數(shù)級增長,這樣的增長攤薄了指數(shù)級增長的成本;第二個(gè)原因就是摩爾定律,隨著工藝改進(jìn),芯片上的晶體管數(shù)量每隔一段時(shí)間就會“無成本”翻倍,從而帶來性能的飛速增長,所以我們感覺芯片的性價(jià)比總是在提高。摩爾定律會永遠(yuǎn)持續(xù)嗎?最近這10年里,我們反復(fù)聽到這個(gè)說法:摩爾定律已經(jīng)結(jié)束。

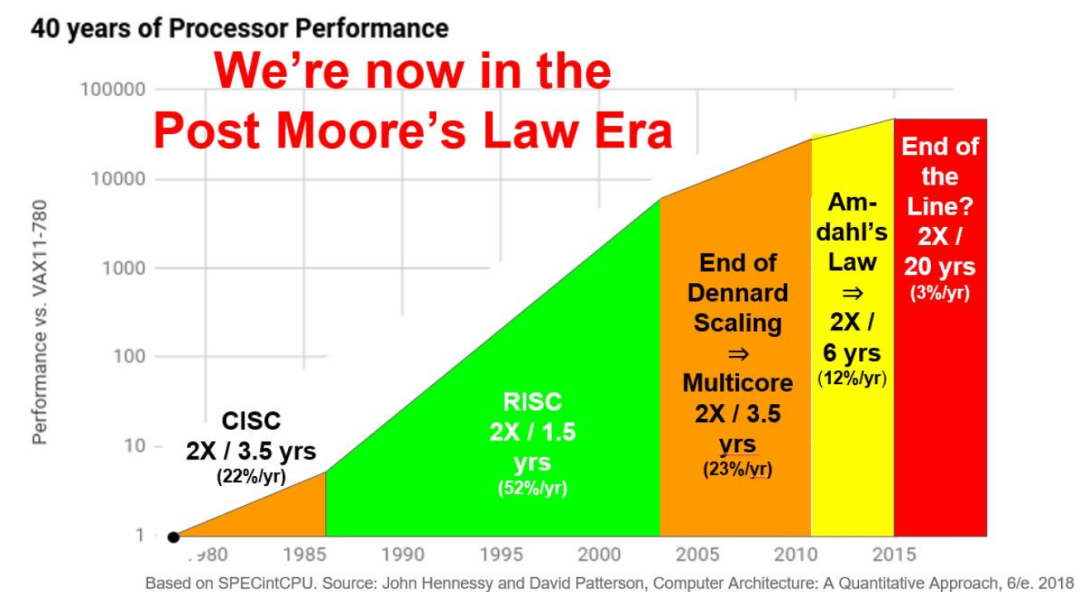

關(guān)于摩爾定律的發(fā)展歷史,從下圖可以看得比較清楚,縱坐標(biāo)是處理器性能,橫坐標(biāo)是不同的工藝和架構(gòu)發(fā)展階段。

從70年代中期開始,基于CISC復(fù)雜指令集的處理器,經(jīng)歷了10年的快速發(fā)展,每3.5年性能就翻一倍。然后精簡指令集RISC由于它流水線比較好設(shè)計(jì),容易利用工藝的發(fā)展,所以能繼續(xù)推動性能的快速發(fā)展,差不多1年半就提高一倍,當(dāng)然這個(gè)時(shí)期也出現(xiàn)了制造工藝大發(fā)展,所以芯片性能提高比較快。

到2005年左右有一個(gè)重要的規(guī)律Dennard Scaling,或者叫MOSFET scaling差不多發(fā)展到頭了,它的含義就是說工藝發(fā)展了,晶體管變小驅(qū)動電壓就會變小,會自然帶來芯片功耗的降低,所以你只管增加芯片復(fù)雜度,下一代工藝出來了自然會幫你把功耗壓住。但是到這個(gè)階段不行了,漏電壓不住了,單位功耗無法再降,那么單核頻率就沒辦法再提高了,那怎么辦呢?我們都知道答案,就是轉(zhuǎn)向多核處理器,多核又帶來一個(gè)高速發(fā)展期,還是三五年就能提高一倍的性能。

但是,多核也存在一些問題,無論是手機(jī)上還是高性能計(jì)算上,都不是有多少核就總是能用多少核的,Amdahl定律就是描述這個(gè)規(guī)律,即算法里面的串行部分總會卡住最高的性能。同時(shí),并行化也有額外開銷,即使像圖像深度學(xué)習(xí)這么極端的并行數(shù)據(jù)算法,也存在一些偏向串行化或者全局的算子會變成性能瓶頸。所以我們看到過去10年里面,處理器的實(shí)際應(yīng)用性能提高遠(yuǎn)沒有前30年那么快了。

總結(jié)來說,過去的四十年里面,不斷發(fā)展的工藝和架構(gòu)設(shè)計(jì)共同推動著摩爾定律持續(xù)前進(jìn),即使是今天也還有3nm、2nm、1nm先進(jìn)工藝在地平線上遙遙可及。但是現(xiàn)實(shí)趨勢來看,更高工藝、更多核、更大的芯片面積已經(jīng)不能帶來過去那種成本、性能、功耗的全面優(yōu)勢,摩爾定律確實(shí)是在進(jìn)入一個(gè)發(fā)展平臺期,也意味著我們進(jìn)入了“后摩爾時(shí)代”。

如今,摩爾定律已經(jīng)到了一個(gè)部分失效的階段,即晶體管密度雖然還在繼續(xù)增加,但功耗密度和性能密度已經(jīng)很難進(jìn)一步提高,也就是沒有那種隨著工藝改進(jìn)自動發(fā)生的進(jìn)步了。后摩爾時(shí)代,我們也觀察到幾個(gè)趨勢正在給驗(yàn)證EDA帶來更高的要求:

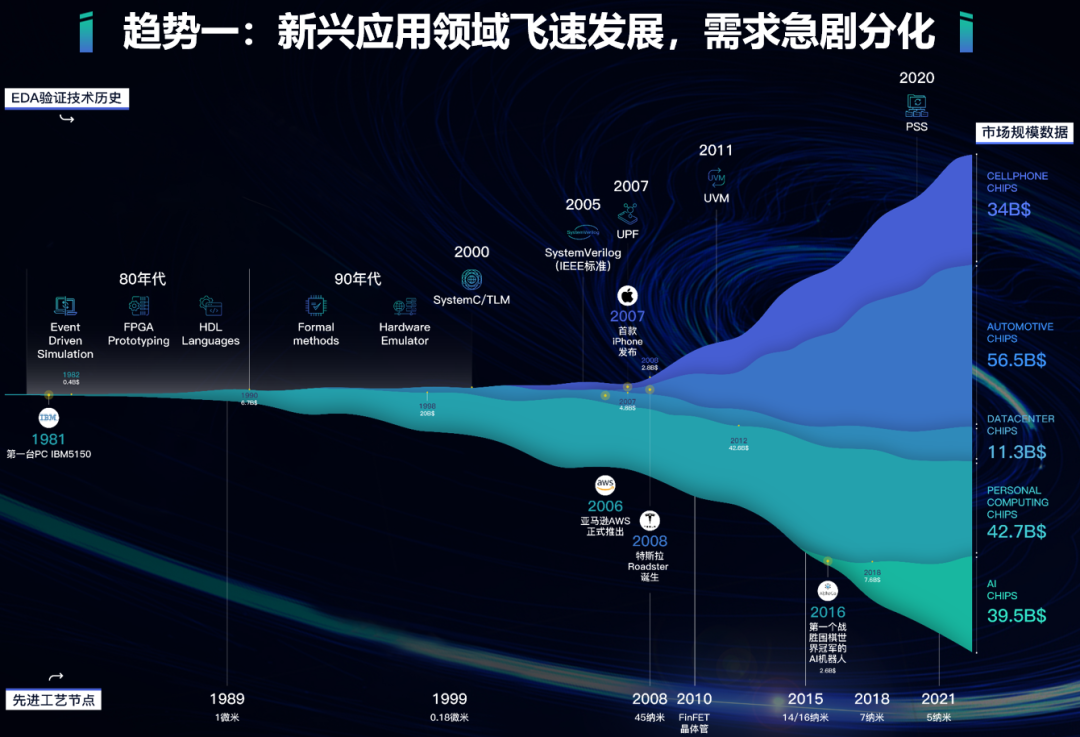

新興應(yīng)用領(lǐng)域飛速發(fā)展,需求急劇分化

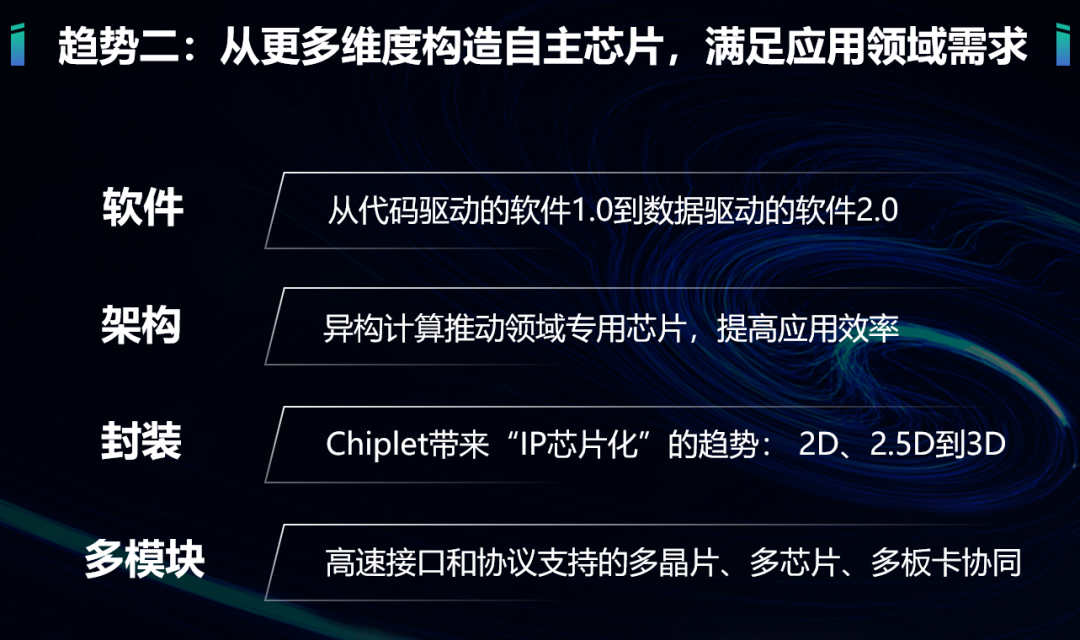

從更多維度構(gòu)造自主芯片,滿足應(yīng)用領(lǐng)域需求

壓力巨大的應(yīng)用創(chuàng)新周期

過去幾十年里,通用電子設(shè)備如個(gè)人電腦、手機(jī)、汽車、云計(jì)算等新興應(yīng)用領(lǐng)域正快速推動著芯片和EDA產(chǎn)業(yè)的發(fā)展。曾經(jīng)圍繞這些設(shè)備里芯片的一個(gè)關(guān)鍵詞是“快”,更快的芯片就是更好的芯片,因?yàn)楣摹⒊杀竞臀锢硐拗贫疾皇菃栴},那是一個(gè)美好的年代。

但是,后摩爾時(shí)代沒有那么容易設(shè)計(jì)出“更快”的芯片了,或者說更快的芯片一定更貴了,是不是芯片不會再變化了呢?答案是否定的,未來芯片的變化反而會更大,不同的指令集、內(nèi)存類型、內(nèi)存大小、外部接口、專用指令或加速器、軟硬件分工模式、封裝模式等等,都沒有絕對的好壞,甚至一味追求更高工藝都不一定正確了,因?yàn)閱晤w芯片繼續(xù)簡單增加功能或者提高工藝,必然帶來成本的增加,對用戶不一定是好事。

這種情況下,設(shè)計(jì)就不一定是做加法了,很多時(shí)候我們可能還要做減法。任何改變都是取舍權(quán)衡,那么權(quán)衡由什么來決定呢?由應(yīng)用系統(tǒng)的需求決定。未來,如何發(fā)揮一顆芯片的設(shè)計(jì),也需要應(yīng)用系統(tǒng)和軟件做相應(yīng)的變化。過去那種軟件不需要太多變化,隔幾年用同樣的錢換新一代的芯片就能看到系統(tǒng)性能提升,這樣的經(jīng)驗(yàn)已經(jīng)不再適用了。

所以,后摩爾時(shí)代的芯片創(chuàng)新空間是變大了,而不是變小了。但是設(shè)計(jì)的約束和目的變了,從設(shè)計(jì)更快的芯片轉(zhuǎn)變?yōu)樵O(shè)計(jì)更符合系統(tǒng)應(yīng)用創(chuàng)新需求的芯片。我們也確實(shí)看到了業(yè)界在發(fā)生這樣的變化:蘋果、特斯拉、華為、谷歌、阿里巴巴等手機(jī)、汽車、服務(wù)器、AI、云服務(wù)等高科技系統(tǒng)公司,都在從“采購和使用通用芯片”,轉(zhuǎn)向“定制自己的芯片”,在內(nèi)部不斷加強(qiáng)芯片團(tuán)隊(duì)方面的投資,通過SoC芯片和ASIC芯片的創(chuàng)新來實(shí)現(xiàn)系統(tǒng)創(chuàng)新。同時(shí),新興高科技的發(fā)展也反過來促進(jìn)芯片設(shè)計(jì)和EDA的發(fā)展,比如人工智能、機(jī)器學(xué)習(xí)、云計(jì)算等技術(shù)對芯片設(shè)計(jì)和 EDA工具本身的影響也越來越大。

對于國內(nèi)公司來說,在高工藝發(fā)展受限的大背景下,就更沒有必要完全把注意力放在先進(jìn)工藝上,應(yīng)該看到即使是在14nm、16nm、28nm甚至更低工藝上,國內(nèi)很多芯片產(chǎn)品整體來看還是跟國際巨頭有差距,這種差距恰恰是架構(gòu)、軟件、編譯器以及應(yīng)用需求匹配等因素造成的。后摩爾時(shí)代的芯片創(chuàng)新,會有更多不同的維度。

后摩爾時(shí)代的第二個(gè)趨勢是,芯片設(shè)計(jì)約束變得更多維。過去在工藝發(fā)展驅(qū)動下,一般都以圍繞著工藝的PPA(性能、功耗、面積)指標(biāo)作為核心維度實(shí)現(xiàn)芯片設(shè)計(jì),其中面積也約等于芯片成本。但是發(fā)展到后摩爾時(shí)代,PPA三者之間的矛盾互斥已經(jīng)大到很難平衡,而成本也不再簡單取決于芯片面積,因此我們可以觀察到芯片設(shè)計(jì)的約束維度已經(jīng)開始發(fā)生明顯的變化,其中包括:

軟件

越來越定制化的芯片,必然也越來越依賴針對性的軟件去利用這些創(chuàng)新的芯片功能。蘋果手機(jī)在自主設(shè)計(jì)芯片之前,曾經(jīng)長期CPU工藝落后于高通,但是基于iOS軟件系統(tǒng)的蘋果手機(jī)流暢程度、用戶體驗(yàn)都優(yōu)于大部分競爭對手。這個(gè)例子充分說明了系統(tǒng)級軟硬件集成優(yōu)化的重要性,而單個(gè)芯片的PPA指標(biāo)并不必然能給整個(gè)應(yīng)用系統(tǒng)帶來提升。

而軟件的優(yōu)化,不能等到芯片開發(fā)生產(chǎn)完成再做,必需要從項(xiàng)目規(guī)劃階段就能根據(jù)應(yīng)用需求做好軟硬件劃分,并把“特定軟件”和“特定芯片”結(jié)合到一起,去實(shí)際評估最終能否達(dá)到性能需求。這樣就出現(xiàn)了“先有雞還是先有蛋”的問題,因此新一代EDA工具需要對軟件提前定制和優(yōu)化需求進(jìn)行支持。

架構(gòu)

過去,處理器指令集以從CISC發(fā)展來的x86指令集為典型代表,在發(fā)展過程中不斷增加新的指令,越來越龐大。但RISC-V為代表的新型ISA和架構(gòu)反其道而行之,從一個(gè)非常簡單的指令集出發(fā),只為特定應(yīng)用增加特定指令和加速器。基于這種思路,誕生了大量的DSA(領(lǐng)域特定)芯片,在AI監(jiān)控、自動駕駛、IoT等領(lǐng)域取得了比通用處理器更好的效果。另一個(gè)更激進(jìn)的架構(gòu)演進(jìn)方向代表是存內(nèi)計(jì)算,讓存儲和計(jì)算能夠在同一個(gè)器件內(nèi)完成,這打破了馮諾依曼架構(gòu)的固定模式,在很多機(jī)器學(xué)習(xí)應(yīng)用上都能帶來與工藝發(fā)展無關(guān)的效率提升。

同時(shí),在多核、多計(jì)算單元、多芯粒(die)并行的復(fù)雜芯片中,SoC體系結(jié)構(gòu)的優(yōu)化也還存在很大的空間。舉例來說,我們可以在某些ARM架構(gòu)服務(wù)器芯片,或者在某國產(chǎn)x86 CPU芯片上,都觀察到單核頻率和特定計(jì)算性能高于同檔次Intel Xeon處理器的情況,這說明單純從處理器核的設(shè)計(jì)和生產(chǎn)工藝上,后來者們都已經(jīng)達(dá)到一定的水準(zhǔn)。但是在運(yùn)行多核、多socket的數(shù)據(jù)庫等復(fù)雜系統(tǒng)軟件時(shí),性能還是有一定差距,這也反向證明了在一個(gè)復(fù)雜的多核、多芯片、多級存儲體系里,架構(gòu)優(yōu)化的重要性。

封裝

隨著多芯粒(die)封裝從2D逐漸過渡到3D,高帶寬高密度互連的Chiplet封裝成了最近很火的一個(gè)技術(shù)方向。它把不同工藝的模塊化芯片,像拼接樂高積木一樣用封裝技術(shù)整合在一起,實(shí)現(xiàn)更高的性能。Chiplet可以更容易地賦能系統(tǒng)公司自定義創(chuàng)新芯片,也可以幫助中小型的芯片公司和團(tuán)隊(duì)降低創(chuàng)新門檻,把資源投入在核心創(chuàng)新點(diǎn)上。比如國產(chǎn)GPU公司壁仞科技最近發(fā)布的7nm GPU產(chǎn)品,通過CoWoS Chiplet技術(shù)集成了計(jì)算芯粒和高帶寬HBM2內(nèi)存芯粒,實(shí)現(xiàn)了媲美競爭對手4nm高端GPU的同等算力,并且在不同產(chǎn)品線之間共享計(jì)算芯粒,有效降低了成本和提高了良率。

但是Chiplet包含了很多EDA相關(guān)的新技術(shù),比如說跟制造相關(guān)的包括封裝里面功耗分析、散熱分析等,Chiplet芯片的設(shè)計(jì)驗(yàn)證也對傳統(tǒng)EDA提出了新的要求。特別是在驗(yàn)證技術(shù)和工具方面,實(shí)際上已經(jīng)成為Chiplet發(fā)展的瓶頸。因?yàn)镃hiplet目前還以單一公司完成全系統(tǒng)為主,但未來多廠商合作的新型Chiplet模式會把傳統(tǒng)SoC流程打破,這就要求在IP建模、互連架構(gòu)分析、系統(tǒng)功能驗(yàn)證、功耗驗(yàn)證等方面提出新的模式,而不僅僅是解決了制造問題就能實(shí)現(xiàn)全新的Chiplet產(chǎn)業(yè)結(jié)構(gòu)。

多模塊

從應(yīng)用系統(tǒng)出發(fā)的新趨勢,也決定了單顆芯片無法達(dá)成系統(tǒng)設(shè)計(jì)目的,因此芯片的定義、設(shè)計(jì)和驗(yàn)證也必須考慮多顆芯片之間的協(xié)同。比如Nvidia公司的NVLink GPU片間通信接口協(xié)議,給GPU處理器增加了高性能數(shù)據(jù)交換接口,繞過了原來的PCIe瓶頸,有效提高了多GPU協(xié)同訓(xùn)練大型AI模型的效率。目前復(fù)雜處理器的規(guī)模在幾億到上百億等效邏輯門,但未來一個(gè)電子應(yīng)用系統(tǒng)的總邏輯門數(shù)量會在幾千億、幾萬億,這不可能用單顆芯片或單顆封裝去完成,必須充分考慮幾十到幾百顆芯片的擴(kuò)展,并有效處理子系統(tǒng)之間的連接和分工。

這種通過異構(gòu)、多芯粒、多模塊系統(tǒng)集成的方式,也體現(xiàn)了從系統(tǒng)設(shè)計(jì)角度出發(fā)去定義和設(shè)計(jì)芯片的理念。半導(dǎo)體設(shè)計(jì)產(chǎn)業(yè)開始不僅是通過工藝的提升,而是更多考慮系統(tǒng)、架構(gòu)、軟硬件協(xié)同等,從系統(tǒng)應(yīng)用來導(dǎo)向、從應(yīng)用來導(dǎo)向去驅(qū)動芯片設(shè)計(jì),讓用戶得到更好的體驗(yàn)。

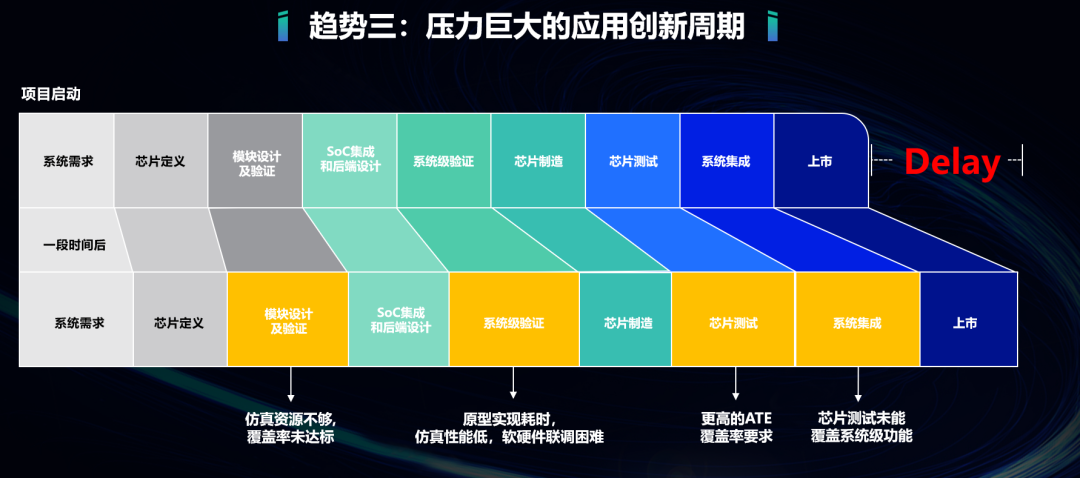

再來說項(xiàng)目周期,自定義芯片驅(qū)動的系統(tǒng)創(chuàng)新周期是從應(yīng)用需求創(chuàng)新開始,對系統(tǒng)和芯片提出新的需求,因此推導(dǎo)出需要一顆或多顆在功能、功耗、性能上權(quán)衡的芯片,然后開始芯片的設(shè)計(jì)和生產(chǎn),芯片被制造出來之后投入使用,與軟件一起形成新的系統(tǒng)。但是這個(gè)周期當(dāng)中的芯片設(shè)計(jì)驗(yàn)證環(huán)節(jié),對系統(tǒng)公司來說是一個(gè)全新的領(lǐng)域,不管是外包還是自研,在當(dāng)前的EDA工具和方法學(xué)流程中,都存在1-2年的創(chuàng)新間隔。

由于系統(tǒng)級軟硬件和傳統(tǒng)芯片設(shè)計(jì)思路之間的隔閡,這樣的創(chuàng)新性項(xiàng)目周期,往往從一開始就會耗費(fèi)比預(yù)計(jì)更長的時(shí)間,從系統(tǒng)的功能性能指標(biāo)到具體的芯片定義是一個(gè)非常復(fù)雜的過程,需要跨領(lǐng)域的架構(gòu)工程師團(tuán)隊(duì)緊密合作,基于多種工具平臺分解需求和向下映射。

鑒于系統(tǒng)級應(yīng)用的復(fù)雜性和技術(shù)挑戰(zhàn),這些步驟往往需要比預(yù)期中更多的時(shí)間,這會迫使項(xiàng)目通過驗(yàn)證和測試等下游步驟去彌補(bǔ)損失的時(shí)間,進(jìn)一步壓縮本就很緊張的時(shí)間表。但是復(fù)雜SoC芯片和高級工藝的超高成本,又決定了芯片的驗(yàn)證要求很高,需要保證功能和性能驗(yàn)證的覆蓋率,于是我們往往會看到芯片設(shè)計(jì)項(xiàng)目在仿真、調(diào)試、原型驗(yàn)證等環(huán)節(jié)碰到資源、人員、驗(yàn)證平臺實(shí)現(xiàn)等各種瓶頸,引入更多的時(shí)間延誤。即使芯片成功流片,進(jìn)入生產(chǎn)階段,系統(tǒng)級應(yīng)用帶來的復(fù)雜測試環(huán)境,對傳統(tǒng)ATE測試方法又帶來速度、資源上的各種限制,影響項(xiàng)目真正實(shí)現(xiàn)“進(jìn)入市場”的時(shí)間點(diǎn)。

因此,這里的第三個(gè)趨勢,是前兩個(gè)發(fā)展趨勢所必然帶來的挑戰(zhàn)。如果不能直面這些挑戰(zhàn),那么系統(tǒng)創(chuàng)新驅(qū)動的多維芯片創(chuàng)新就會受到影響。

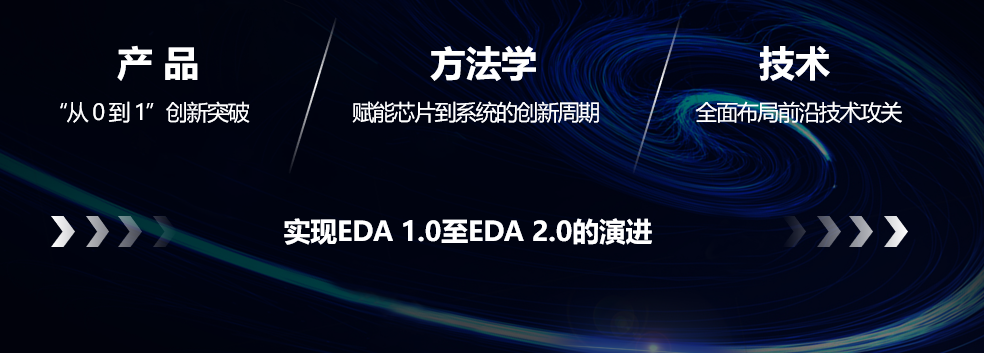

后摩爾時(shí)代,針對以上三大趨勢,芯華章貫徹“終局思維”,以終為始,致力于打造更智能的EDA 2.0,其核心目標(biāo)是:

建立起能夠覆蓋從芯片級別到最終系統(tǒng)級別的驗(yàn)證和測試方法學(xué),提升芯片及電子系統(tǒng)的性能表現(xiàn)。

讓系統(tǒng)工程師和軟件工程師都參與到芯片設(shè)計(jì)中來,用智能化的工具和服務(wù)化的平臺來縮短從芯片需求到系統(tǒng)應(yīng)用創(chuàng)新的周期,降低復(fù)雜芯片的設(shè)計(jì)和驗(yàn)證難度,賦能電子系統(tǒng)創(chuàng)新。

未來,系統(tǒng)應(yīng)用將是芯片設(shè)計(jì)的核心驅(qū)動力。芯華章所提出的EDA 2.0并不是一個(gè)0和1的狀態(tài)變化,而是要在當(dāng)前的基礎(chǔ)上進(jìn)一步增強(qiáng)各環(huán)節(jié)的開放程度。在開放和標(biāo)準(zhǔn)化的前提下,將過去的設(shè)計(jì)經(jīng)驗(yàn)和數(shù)據(jù)吸收到全流程EDA工具及模型中,形成智能化的EDA設(shè)計(jì),形成從系統(tǒng)需求到芯片設(shè)計(jì)、驗(yàn)證的全自動流程。同時(shí),為了滿足算力和平臺化的要求,EDA 2.0應(yīng)該與云平臺和及云上多樣化的硬件結(jié)合,充分利用成熟的云端軟硬件生態(tài)。要支持應(yīng)用廠商快速得到需要的芯片,EDA 2.0還應(yīng)該是產(chǎn)品和服務(wù)的結(jié)合,最終實(shí)現(xiàn)電子設(shè)計(jì)服務(wù)——EDaaS(Electronic Design as a Service)。

2022年7月,芯華章成立研究院,匯集了沈昌祥、毛軍發(fā)等中國兩院院士,更有數(shù)十位來自集成電路設(shè)計(jì)、電子設(shè)計(jì)自動化與信息算法系統(tǒng)領(lǐng)域的頂級專家學(xué)者,以研究下一代EDA 2.0方法學(xué)與技術(shù)為目標(biāo),面向工業(yè)應(yīng)用的核心基礎(chǔ)技術(shù)做長期、持續(xù)地研發(fā)投入與技術(shù)攻關(guān),推動從EDA 1.0往2.0發(fā)展,滿足數(shù)字世界中系統(tǒng)應(yīng)用對芯片多樣化的需求,打造自主可信賴的電子系統(tǒng)創(chuàng)新基石。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<